Многофункциональный логический элемент

Иллюстрации

Показать всеРеферат

Союз Советскик

Социапистическик респубики

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ iu 898618 (6i ) Дополнительное к авт. свид-ву— (22)Заявлено 06.03.80 (21) 2891014/18-21 с присоединением заявки №(51)М. Кл.

Н 03 К 19/00

Государстнапвй комитет

ССС1 (23) Приоритетпо делан иаобоетекнй и открыткй

Опубликовано 15. 01. 82, Бкц летень № 2 а

Дата опубликования описания 15.01.82 (53) УДК 621 ° 374 (088. 8) В.Д.Козюминский,В.А.Мищенко, А.Н.Се и С.M.Tåðåøêo (72) Авторы изобретения (7!) Заявитель (54) МНОГОФУНКЦИОНАЛ6НЫЙ ЛОГИЧЕСК!Ф ЭЛЕМЕНТ

Изобретение относится к автоматике, вычислительной технике и радиоэлектронике.

Известен многофункциональный логический элемент, реализующий все логические функции двух и более переS менных (1).

Недостаток этого элемента в том, что он имеет сложную конструкцию, обладает большим числом внешних вы" о водов, что снижает его надежность и быстродействие и имеет сложную организацию настройки, что исключает его непосредственное применение в адаптивных вычислительных структу15 рах и многофункциональных автоматах.

Известен многофункциональный логический элемент на МОП-транзисторах, который содержит элементы ИЛИ, формирователи с прямыми и инверсными входами и входные шины, элемент ИЛИИсключительно и дополнительные транзисторы, затворы транзисторов элемента ИЛИ-Исключительно и затворы дополнительных транзисторов подключень1 ко входным шинам, а входы формирователей подключены к истокам нагрузочных транзисторов элемента ИЛИИсключительно (2$.

Недостатком этого элемента является сложная настройка, так как при реализации заданных логических функций на его настроечные входы должны поступать входные переменные, что затрудняет его использование без дополнительных схем коммутации в адаптивных (перестраиваемых) структурах и схемах многофункциональных автоматов. что сужает область его применения.

Целью изобретения является упрощение многофункционального логического элемента и расширение области его применения.

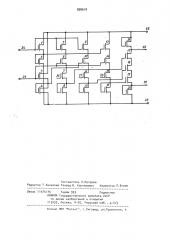

Для достижения поставленной цели многофункциональный логический элемент на МОП-транзисторах, реализующий все логические функции двух пе,8986 ременных, выполнен на двух инверторах и четырех трехвходовых элементах И-НЕ, причем первый информационный вход подключен ко входу первого инвертора и к первым входам первого и второго элементов И-НЕ, второй информационный вход подключен ко входу второго инвертора и ко вторым входам первого и третьего элемента И-НЕ, первый, второй и третий настроечные 1о входы подключены соответственно к третьим входам первого, второго и третьего элементов И-НЕ, выходы первого и второго инверторов подключены соответственно к первому входу третьего элемента И-HE и ко .второму входу второго элемента И-НЕ, выходы первого, второго и третьего элементов И-НЕ подключены соответственно к первому, второму и третьему входам четвертого элемента И-НЕ, имеющего два выхода — прямой и инверсный, которые одновременно являются выходами многофункционального логического элемента. 25

На чертеже представлена электрическая принципиальная схема многофункционального логического элемента на МОП-транзисторах.

В многофункциональном логическом элементе первый и второй инверторы выполнены на последовательно включенных переключательном и нагрузочном транзисторах 1,2 и 3,4 соответственно. Каждый из четырех элементов И-НЕ Ç5 содержит последовательно включенные три переключательных транзистора и один нагрузочный 5-7 и 8; 9-11 и 12;

13-15 и 16; 17-19 и 20 соответственно. В четвертом элементе И-HE исток 40 первого переключательного транзистора 17 подключен к истоку дополнительного нагрузочного транзистора 21.

Элементы И-НЕ и инверторы включены между шиной 22 питания и общей шиной 4s

23. Первый информационный вход 24 подключен к затворам транзисторов

1,5 и 9, второй информационный вход

25 подключен к затворам транзисто pos 3, 6 и 14. Первый 26, второй 27 о и третий 28 настроечные входы подключены соответственно к затворам транзисторов 7,11 и 15. Выходы первого и второго инверторов (стоки транзисторов 1 и 3) подключены соответственно к затворам транзисторов

13 и 10, выходы первого, второго и

18

4 третьего элементов И-HE (стоки транзисторов 7, 11 и 15 соответственно) подключены соответственно к. затворам транзисторов 17-19 четвертого элемента И-НЕ, имеющего два выхода прямой 29, подключенный к истоку транзистора 17, и инверсный - 30, подключенный к стоку транзистора 19, которые одновременно являются выходами многофункционального логического элемента.

Устройство работает следующим образом.

В соответствии с алгоритмом настройки (см.таблицу) на настроечные входы 26-28 поступают сигналы О или

1, одновременно на информационные входы 24 и 25 элемента поступают входные переменные. При этом на пря:мом и инверсном выходах элемента об-" разуются сигналы, соответствующие конкретным логическим функциям двух переменных. Прямой и инверсный выходы элемента описываются следующими логическими зависимостями у =x„x

) У прямом (инверсном) выходе элемента; х,х — выходные логические пе1) ременные на входах 24 и 25 соответственно;

u,u,u — сигналы настройки, цй принимающие значения в соответствии с приве-. денным алгоритмом в таблице на входах 26, 27 и 28 соответственно.

Таким образом, многофункциональный логический элемент реализует все логические функции двух переменных и обладает при этом простейшей схемой настройки, так как не требует коммутации настроечных входов с информационными; и более широкими областями применения, так как на входы настройки поступают только контакты 0,1, что позволяет реализовать на его основе адаптивные вычислительные и управляющие структуры. Предлагаемый элемент более прост, так как реализован всего на 21 ИОП-транзисторе (известный на 22); кроме того, weмент имеет меньшее количество внешних выводов — 9 (у известного - 11); за счет более простой конструкции элемент более надежен.

898618

29

Х1Х2

Х1 Х2

Х1Ч Х2

Х1Х2ч Х1Х2

X1" Х2

Х1Х2

X1X2YX I Х2

Х1Х

Х2

Х2

Xl

Х1&Х2

X1VX2

45

Значение сигналов настройки на входах

26 27 28

Формула изобретения

Многофункциональный логический элемент на МОП-транзисторах, реализующи все логические функций двух переменных, отличающийся тем, что, с целью упрощения и расширения области применения, он выполнен на двух инверторах и четырех трехвходовь|х элементах И-НЕ, причем первый информационный вход подключен ко входу первого инвертора и к первым входам первого и второго элементов И-НЕ, второй информационный вход подключен ко входу второго инвертора и ко вторым входам первого и третьего элемента И-НЕ, первый, второй и третий настроечные входы подключены соответственно к третьим входам перЛогические функции, реализуемые на выходах вого, второго и третьего элементов

И-НЕ, выходы первого и второго инверторов подключены соответственно к первому входу третьего элемента И-НЕ и ко второму входу второго элемента:

И-НЕ, выходы первого, второго и третьего элементов К-НЕ, подключены соответственно к первому, второму и третьему входам четвертого элемента

И-НЕ, имеющего два выхода — прямой и инверсный, которые одновременно яв» ляется выходами многофункционального логического элемента.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N 405177, кл. H 03 К 19/00, 1972.

2. Авторское свидетельство СССР и 446948, кл. Н 03 K 19/00, 1973

898618

Составитель Л.Петрова

Редактор Т.Веселова Техред Ж. Кастелевиц Корректор О Билак

Заказ 11974/75 Тираж 953 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная,