Входной усилитель-формирователь с запоминанием информации

Иллюстрации

Показать всеРеферат

8. В. Баранов, IO.M. Герасимов, А

П.Б. Поплевин и З.П. Сав (72) Авторы изобретения (7l) Заявитель (54) ВХОДНОЙ УСИЛИТЕЛЬ-фОГМИРОВАТЕЛЬ

С ЗАПОМИНАНИЕМ ИНФОРМАЦИИ изобретение относится к запоминаю щим устройствам и может быть использовано при построении микромощных ин-. тегральных запоминающих устройств на

КМДП"транзисторах в качестве элемента адресного или информационного буферного регистра, согласующегося с

ТТЛ-схемами.

Известны входные усилители-формирователи с запоминанием информации, о содержащие два инвертора на КИДП-транзисторах и транзистор р-типа, причем к входу схемы подключен сток транзистора р-типа и входы. инверторов I.I3.

Недостаток устройств - невысокое

15 быстродействие и низкое входное со-. противление в динамическом режиме.

Наиболее близким техническим решением к предлагаемому является усилитель-формирователь с запоминанием информации на КМДП-транзисторах, согласующийся с ТТЛ-схемами, содержащий триггер на транзисторах р" типа и и-типа, истоки транзисторов р-типа подключены к шине источника питания, а истоки транзисторов и-типа - к стоку ключевого транзистора п-типа, исток которого соединен с шиной нулевого потенциала, два установочных транэис тора р-типа, истоки которых подключе ны к шине источника питания, а стоки соответственно к обьединенным стокам транзисторов триггера, стоки первых транзисторов р-типа и и-типа триггера соединены с затворами вторых трам зисторов р-типа и п-типа, стоки которых соединены с затворами первых транзисторов р-типа и и-типа тригге-. ра, затворы установочных транзисторов и ключевого транзистора соединены с управляющей шиной; два инвертора на транзисторах р-типа и п-типа, причем истоки транзисторов n"Tèâà инверторов соединены с шиной нулевого потенциала, а стоки транзисторов р-типа инверторов - с шиной источника питания, затворы транзисторов п-.типа и р-типа первого инвертора подключены к

903970 стокам первого транзистора р-типа триггера и первого транзистора обрат- ной связи, затвор которого подключен к стокам транзисторов первого инвертора и прямому выходу устройства, за творы транзисторов второго инвертора подключены к стоку второго транзисто ра р-типа триггера и стоку второго транзистора обратной связи р-типа, затвор которого подключен к стокам транзисторов второго инвертора и инверсному выходу устройства, а исток соединен со стоком опорного транзистора р-типа, исток которого подключей к шине источни ха питания, а зат вор.к шине источника опорного напряжения, 1 сток первого транзистора обратной связи соединен со стоком информационного транзистора р-типа, исток которого подключен. к шине источника питания, а затвор - ко входу устройства 32l.

Недостаток этого устройства заключается e его сложности, твк как оно содержит большое число элементов и нуждается в стабильном источнике опорного напряжения, который в ин тегральных схемах должен выполняться в виде отдельной схемы на том же крис галле.

Цель изобретения - упрощение усипителя-формирователя.

Поставленная цель достигается тем, Что во входной усилитель"формирователь с запоминанием информации, со" держащий КИДП-транзисторы р-типа и й-типа, причем истоки первого и второго нагрузочных транзисторов р-типа соединены с шиной питания, истоки первого и второго переключающих транзис торов и -mna подключены к стоку ключевого транзистора и -типа, нагрузочные и переключающие транзисторы соединены по триггерной схеме, исток ключевого транзистора подключен к шине нулевого потенциала, а затвор соединен с шиной управления и затво рами первого и второго установочных транзисторов р-типа, истоки которых подключены к шине питания; сток первого установочного транзистора соеди.НЕн СО СТОКОМ ПЕРВОГО НаГруЗОЧНОГО траНзистора и является инверсным выходом, а сток второго установочного транзистора подключен к стоку второго нагруэочного транзистора и является прямым выходом устройства, введв" ны управляющий транзистор щ-типа и информационный транзистор и-типа, 5

3S

?0

?5

36

46

4 причем сток управляющего транзисторе ! соединен со стоком первого установоч ного транзистора, затвор - со стоком второго установочного транзистора, а исток - со стоком информационного транзистора, исток которого подключен к стоку ключевого транзистора, а затвор является входом усилителя-форМирователя.

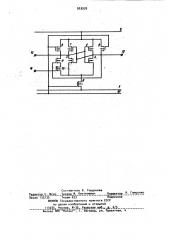

На чертеже изображена принципи" альная схема предлагаемого устрои ства.

Усилитель-формирователь содержит первый 1 и второй 2 нагруэочные тран;зисторы р-типа, первый 3 и второй 4 переключающие транзисторы -типа, шину 5 питаний, ключевой транзистор 6 -типа, шину 7 нулевого потенциала, ;первый 8 и второй 9 установочные транзисторы р"типа, шину 10 управления, управляющий транзистор 11 И -ти"па и информационный транзистор 12 и-типа. На чертеже обозначены инверсный выход 13, информационный вход 14 и прямой выход 15 усилителя-формирователя. Яирина канала транзистора 4 выбрана большей, чем у транзистора 3 (сопротивление транзистора 4 меньше сопротивления транзистора 3). Размеры транзисторов 1, 2 и 8, 9 попарно одинаковые. Размеры транзисторов. 1f и 12 выбираются так, чтобы суммарное сопротивление транзисторов 3, 11 и 12 было меньше сопротивления транзистора 4.

Усилитель-формирователь работает следующим образом.

В исходном состоянии (режим хранения ) потенциал на шине 10 соответствует "О". Транзистор 6 закрыт, а открытые транзисторы 8 и 9 на выходах

13 и 15 схемы устанавливают "1". При этом транзисторы 1 и 2 закрываются, а транзисторы 3 и 4 открываются. Транзистор 11 открыт. В зависимости от логического уровня на входе 14 транзистор 12 может быть либо открыт, либо закрыт, причем в любом случае состояние транзистора 12 не влияет на состояние усилителя-формирователя, поскольку транзистор 6 закрыт. В режиме хранения на входе 14 должна быть установлена информация.

В режиме приема и запоминания входной информации (режим обращения) на входе 14 устанавливается "1". Трэнзисторы 8 и 9 закрываются, а .транзистор 6 открывается. Параэитные емкости в узлах схемы, связанных с выходателя заключается в его упрощении по сравнению с известным. формула изобретения

Входной усилитель-формирователь с запоминанием информации, содержащий КИДП-транзисторы р-типа и п-типа, причем истоки первого и второго нагрузочных транзисторов р-типа соединены с шиной питания, истоки первого и второго переключающих транзисторов и-типа подключены к стоку ключевого транзистора п-типа, нагрузочные и переключающие транзисторы соединены по триггерной схеме, исток ключевого транзистора подключен к шине нулевого потенциала, а затвор соединен с шиной управления и затворами первого и второго установочных транзисторов р-типа, истоки которых подключены к шине питания, сток первого установочного транзистора соединен со стоком первого нагрузочного транзистора и является инверсным выходом, а сток второго установочного транзистора подключен к стоку второго нагрузочного транзистора и является прямым выходом устройства, о тл и ч а ю шийся тем, что, с це" лью упрощения усилителя"формировате" ля, он содержит управляющий транзис-. тор и-типа и информационный транзистор п-типа, причем сток управляющего транзистора соединен со стоком первого установочного транзистора, затвор - со стоком второго установочнаго транзистора, а исток — со стоком информационного транзистора, исток которого подключен к стоку ключевого транзистора, а затвор является входом усилителя-формирователя.

Источники информации, принятые во внимание при экспертизе

1. Патент Великобритании N 1543872, кл. H 03 K 17/60, опублик. 1979.

2. Electronics, 1978, т. 51,N 14, с. 106-111 (прототип).

90397 ми 13 и 15, начинают разряжаться через открытые транзисторы 3, 4 и 6. Если на входе 14 установлен "0" (транзистор 12 закрыт), ток разряда, проходящий через транзисторы 4 и 6, сольше тока, проходящего через транзисторы 3 и 6.Транзисторы 1-4, соединенные по триггерной схеме, устанавливаются в состояние, когда на выходе 1 имеется "0", а на выходе 13 - "1" (тран- >О зисторы l и 4 открыты, транзисторы 2 и 3 закрыты). По цепи обратной связи транзистор 11 закрывается и усилительформирователь сохраняет установившееся состояние при любых изменениях 15 информации на входе 14.

В случае подачи в исходном состоянии на вход 14 "1" открывается транзистор 12 и суммарный ток разряда, проходящий через транзисторы 11, 12, 2о

3 и 6, больше тока, проходящего через транзисторы 4 и 6, и транзисторы 1-4 триггера устанавливаются в состояние, при котором на выходе 15 устанавливается "1", а на выходе 13 - "0" тран- 2З

;зисторы 2 и 3 открыты, транзисторы 1 и 4 закрыты1. 8 этом состоянии транзистор 11 остается открытым, íî, поскольку на выходе 13 установлен "0", изменение информации на входе 14 не Зо влияет на состояние усилителя-формирователя.

Такии образом, усилитель-формирователь эапоиинает поданную на вход 14 информацию. При зтои входная информация подается на вход 14 до перехода к режииу обращения и удерживается в этом .режиме на время, определяемое быстродействием транэистордв 1-4 триггера, после чего инфориа- 4о ция на входе 14 может изменяться.

Уровень срабатывания усилителяфориарователя по входу 14 определяется пороговым напряжениеи транзисто- ра 12 и составляет при существующеи 4э технологическом процессе 1-2 В, что обеспечивает стыковку усилителя-4ориирователя с ТТЛ-схемами.

Технико-зкономическое преимущест1 о предлагаемого усилителя-формирова- >о

903970

Составитель В. Гордонова

«Редактор С.. Рско Техреду Ж. Кастелевич « Корректор А. р ."ц "

Заказ 133/35 Тираж 423 Подписное

ВНИИОИ Государственного комитета СССР по делам изобретений и открытий

Филиал ППП "Патент", r. Ужгород, ул. Проектная, й