Универсальный логический модуль

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ю911507

Союз Советскык

Соцыапистычесиыв

Республик

{6! ) Дополнительное к авт, свид-ву (22) Заявлено 11. 06. 80 (21) 2982027/18-24 с присоединением заявки пв (51)М. Кл.

G 06 F 7/00 фвудврвтаав11, квинтет

CCCP ав двлвм кзвбрвтеивй к, вткрытвй (23)п рноритет (53) УДК 681.3 (088. 8) Опубликовано 07.03.82. Бюллетень М 9

Дата опубликования описания 07.03.82 (72) Авторы

А.В. Гурьянов, В.Д. Козюминский, В.А. Мищенко (54) УНИВЕРСАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ

" I l ).

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для реализации логических функций и переменных.

Известно устройство для реализации всех логических функций и пере-: менных, содержащее управляющие и информационные входы. В качестве сигналов настройки в устройстве кроме сигналов "0" и "1" используются и сами входные информационные сигнаНедостатком является то, что настройка такого устройства на реализацию в нем требуемой логической функ ции осуществляется соответствующеи коммутацией информационных сигналов к управляющим входам. При электронной настройке устройства это может быть осуществлено с помощью специаль- ной схемы-коммутатора, что значительно увеличивает его общую сложность и уменьшает быстродействие.

Наиболее близки" по конструкции и способу настройки к предлагаемому универсальный логический модуль, содержащий и информационных и 2и управляющих входов, 2 элементов И и элемент ИЛИ, выход которого является выходом устройства, а его входы соединены с выходами элементов И, первые входы которых управляющие, а ос1 тальные и входов каждого из которых подключены к прямым и инверсным ин-. формационным входам устройства.Модуль путем подачи íà его управляющие входы сигналов "0" и "1" моожет настраиваться на реализацию любой логичес" кой функции и входных-информационных переменных f2).

Недостатком данного устройства является его сложность, так как он содержит элемент ИЛИ на 2 входов и и

2и элементов И на и+1 вход каждый (суммарная сложность устройства по числу входов логических элементов S = 2 (и+2) ) .

3 911507 емую модулем логичесЦель изобретения - упрощение мо- ределяет реализуем ю мо дуля., кую функцию входных информационных

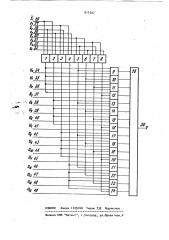

Поставленная цель достигается переменных В сх м схеме модуля с помощью тем, что универсальный логический элементов И 1-24 реализуются все модуль, содержащий элемент ИЛИ и 2" произведения наборо я на оров входных переменэлементов И (n — количество информа- ных таким образом о разом, что на выходах ционных входов), управляющие входы элементов И 9-24 фо рмируются сигналы которых подключены к упраВляющим вхо- произведений наборов 0-15, где иодам модуля соответственно, а выходы - мер набора соответствует двоичному к входам элемента ИЛИ, выход которого t0 номеру, образованному входными пе ва еш ато подключен к выходу модуля, содержит ременными х i = 1 4 б т.е. на ор два дешифратора, причем прямые и ин- 0 соответствует произведению х х x .. версные информационные входы первой а набор 1 - х х 2 х б группы модуля подключены к входам 15 - хх х х . В результате этого ора, à прямые и ин- is выходной сигнал модуля формируется в . нфор ц о ные входы второи соответствии с логическим выражением группы модуля подключены к входам f y ц,К („ . х ) второго дешифратора, выходы первого К х

„х„, х, хз, х, где дешифратора подключены к первым ин(х, х, х, х„) — набор аргуменформационным входам weментов мотов 7<„x д ментов И мо- щ для настройки модуля на реализадуля, вторые информационные вхо ы которых подключены к выхо ам нф р ц ные входы цию некоторой логической функции. дешифратора. д е к выходам второго достаточно положить сигнал U 0 15 (У ° равным "1" для тех наборов, на котоТакой модуль имеет более и очн олее прочную рых реализуемая функция равна единиконструкцию, чем известный, так как 2з це и положить U 0 бсуммарное число входов логических

l для тех на оэлементов в нем меньше. ров, на которые эта функция равна нулю.

Иа чертеже представлена схема Аналогично строится схема модуля универсал чого логического мо ля н о о модуля на для реализации логических функций и нфор ц ных входа (и-4). зв переменных, при этом она содержит

ИЛИ: 25, информационные вхо ы 26-33 для прямых и инверсных значений мент на 2 входов.

ИЛИ 2" д вхсфных переменных, управля ие входы 34-39 и выход 50. у ра ляющие вхо- Таким образом, общая сложность

Выход предлагаемого модуля по суммарному числу входов его логических элеменыход элемента ИЛИ 25 является выходом 50 модуля, а его вхо ы с выход и 50 ду, его входы соеди- тов определяется выражением S иены с выходами элементов И 9-24,пер- = и . 2"/ + 2"+ . вые входы которых являются управляющими вхо ами 34-49 и

Сложность же схемы известного мощими входами 3 9 модуля, Входы ) дуля $ ю (и 2) ° 2 и элементов И 1-8 подключены к информационным входам 26-33 модуля, а их Схема предлагаемого модуля имеет выходы попарно соединены с входами меньшую сложность, чем схема известэлементов И 9-24. о ного. Причем выигрыш в обьеме обору"

Сх ема универсального логического дования с увеличением и возрастает. модуля работает следующим образом Следует о™е™ть, что.если и нечетНа информационные входы 26-33 мо» ное число, то схема предлагаемого дуля подается прямые и инверсные ко- УстРойства Должна соДеРжать, кроме ды информационных переменных х °, 1 элементов И на три входа и эле4

1, 4. Элементы И 1-8 образуют мента ИЛИ, 2 элементов И на И+ /й

У 1i+1/< два цешифратора. имеющие 2"/ + при входов и Ря элементов И на И-4j< и четном и 2 +2 при и нечетй+ Ф и-a/2 входов, реализующих все коньюкции наборов соответствующих переменных. ментов И.

На управляющие входы 34-49 подаются сигналы настройки Uc-U g, принимающие значения "0" или "1". При этом двоичный код сигналов Uo-И onО .Ю

Формула изобретения

Универсальный логический модуль, содержащий элемент ИЛИ и Р элемен5 91150 тов И (n - количество информационных" входов), управляющие входы которых подключены к управляющим входам модуля соответственно, а вь ходы - к входам элемента ИЛИ, выход которого подключен к выходу модуля, о т л ич а ю шийся тем, что, с целью упрощения модуля, он содержит два дешифратора, причем прямые и инверсные информационные входы первой груп- 10 пы модуля подключены к входам первого дешифратора, а прямые и инверсные информационные входы второй группы мод1 ля подключены к входам второго

7 6 дешифратора, выходы первого дешифратора подключены к первым информационным входам элементов И модуля, вторые информационные входы которых подключены к выходам второго дешифратора.

Источники информации, принятые во. внимание при экспертизе

1. Авторское свидетельство СССР

N 333550, кл. G 06 F 1/00, 1973.

2. Ивлев В.А. Структурная избыточность в логических устройствах. И., "Связь!, 1978, с. 115 рис.2.3 (прототип).