Устройство для функционального контроля больших интегральных схем

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К ASVOPCK©МУ СВИДО БДЬСПВУ («i922773

Союз Соавтекнк

Соцнапнстнчвекнк

Респубики (61) Дополнительное к авт. евид-ву (22)Заявлено 19.06.74 (21) 2035014/18-24 с присоединением заявки М (53)%. Кл.

G 06 F 15/46

G 01 и 31/28 (23)Приоритет

Опубликовано 23.04 .82. Бюллетень РЙ 15 (53) УДК 68! „326 (088. 8) Дата опубликования описания 23.04. 82

0.Ã.Ãðà÷ås, В.Ф.Гузенко, Н.H.Äàíèëèí, В,Б.3

И.С.Лебедев и Л.И.Попель убровский

:)

1 (54) УСТРОЙСТВО ..get ФУНКЦИОНАЛЬНОГО K0HTP0SZ

БОЛЬШИХ ИНТЕГРАЛЬНЫХ СХЕМ

Изобретение относится к вычислительной технике и контрольно-измерительной технике н может быть ис.пользовано для функционального контроля цифровых больших интегральных схем.

Известно устройство функционального контроля цифровых интегральных схем, которое содержит генератор контрольных сигналов регистры сдви16 га, блоки коммутации, блока сравнения, блоки с эталонной логической схемой, блок индикации для .указания содержимого регистров в момент обнаружения неправомерности (1j.

Недостатком данного устройства является необходимость применения эталонной схемы.

Наиболее близким по технической сущности к изобретению является устройство, содержащее блок программно. го управления, соединенный с блоком синхронизации, и по числу выводов контролируемой большой интегральнбй схемы блоки формирования сигналов и сравнения„подключенные к соответствующим выходам блока синхронизации и к большой интегральной схеме, первую группу регистров сдвига, управляющие входы которых подключены к соответствующим выходам блока синхронизации (2).

Недостатком известного устройс-— ва является его невысокая надежность и ограниченное быстродействие из-за наличия многоразрядного регистра сдвига на каждом выводе контролируемой интегральной схемы.

Цель изобретения — повышение надежности и быстродействия устройства.

Поставленная цель достигается тем, что устройство содержит вторую группу регистров сдвига и по числу выводов контролируемой схемы две группы элементов И и блоки памяти, выходы которых соединены с информационными входами соответствующим регистров сдвига, управляющие входы с соответствующими выходами блока синхрониза922773

Формула изобретения ции, первые входы первой и второй группы элементов И подключены к соответствукщим выходам блока синхронизации, вторые входы — к выходам соответствующих регистров сдвига, а выходы ко входам — соответствующих блоков Формирования сигналов и сравнения.

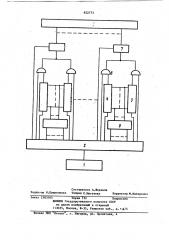

На чертеже представлена блок-схема устройства. 10

Устройство содержит блок программного управления, блок 2 синхронизации, первый регистр 3 сдвига, второй регистр 4 сдвига, блок 5 памяти, группы элементов И 6, блок 15

7 формирования сигналов и сравнения, большую интегральную схему 8.

При работе устройства из блока .1 программного управления через блок

2 синхронизации информация, например щ в виде восьмиразрядных двоичных слов, заносится для хранения в блоки 5 памяти.

Непосредственно при контроле цифровых больших интегральных схем ин- 2$

Формации в виде указанных восьмиразрядных двоичных слов параллельным кодом заносится в регистры 4 сдвига..

После чего блок 2 синхронизации за,пускает по кана ..ам синхронизации. ре- щ гистры 4 сдвига и информация последовательно разряд за разрядом через элементы И 6 поступает на блоки 7 формирования сигналов и сравнения, а затем на выводы контролируемой 35 большой интегральной схемы 8.

За время, в течение которого инФормация в виде последовательного восьмиразрядного кода выдается из регистров 4 сдвига на блоки 7, из. блоков 5 памяти восьмиразрядные слова заносятся в регистры 3 сдвига и по окончании восьми тактов работы блока 2 синхронизации информация на выводы контролируемой большой ин- тегральной схемы 8 через элементы

И 6 и блоки 7 начнет поступать из регистров 3 сдвига и в то же время инФормация из блоков 5 памяти заносится в регистры 4 сдвига и т.д.

Такое схемное решение устройства для функционального контроля больших интегральных схем позволяет на порядок уменьшить число разрядов сдвиговых регистров, а, следовательно, сократить объем электронных элементов в устройстве и повысить его надежность и быстродействие.

Устройство для функционального контроля больших интегральных схем, содержащее блок программного управления, соединенный с блоком синхронизации, и по числу выводов контролируемой большой интегральной схемы блоки формирования сигналов и сравнения, подключенные к соответствующим выходам блока синхронизации и к большой интегральной схеме, первую группу регистров сдвига, управляющие входы которых подключены к соответствующим выходам блока синхронизации, о т— л и ч а ю щ е е с я тем, что, с целью повышения надежности и быстродействия устройства, оно содержит вторую группу регистров сдвига и по числу выводов контролируемой схемы две группы элементов И и блоки памяти, выходы которых соединены с информационными входами соответствующих регистров сдвига, управляющие входи - с соответствукщим выходами блока синхронизации, первые входы первой и второй групп элементов И подключены к соответствующим. выходам блока синхронизации, вторые входы— к выходам соответствующих регистров сдвига, а выходы — к входам соответствующих блоков формирования сигналов и сравнения. г

Источники информации, принятые во внимание при экспертизе

1. Патент Японии кл. 97 (7) G 01

С 06 F. Ii/00, В 48-41739, опублик.

08.12.73.

2 ° "K0 Smith à Hinicomputer aided

mos array Testor" Журнал "Compute

:0esIgu", l970, II 12, р.р. 65-70.

922773

Составитель А.Жеренов

Редактор Н.Пушненкова Техред С.Мигунова Корректор И.Макаренко

Заказ 2583/á5 Тираж 32 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. ;fj/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4