Квадратор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22) Заявлено .11. 07. 80 (21) 2 62808/18-24 (51) М. Кп. с присоединением заявки ¹ (23) ПриоритетG 06 F 7/552

Государственный комитет

СССР по делам изобретений и открытий

t$3) УДК 681. 325 (088.8) Опубликовано 070 82. Бюллетень № 17

Дата опубликования описания 0705.82 (54 ) КВАДРАТОР

Устройство относится к вычисли-. тельной технике и может быть использовано в устройствах ввода и вывода информации ЦВМ, в системах программного управления и автоматического регулирования °

Известны устройства для пересчета и возведения в квадрат импульсных . сигналов, содержащие п -разрядный счетчик импульсов, 2п-разрядный сумматор, логические элементы И, ИЛИ, НЕ (1) и (2) .

Эти устройства обладают ограниченными функциональными возможностями, так как не позволяют реверсивно изменять значение функции на выходе устройства, что особенно важно для систем автоматического управления и регулирования.

Наиболее близким по техническОй сущности к предлагаемому является реверсивный квадратор, позволяющий реверсивно изменять значение функции на выходе устройства, содержащий и-разрядный реверсивный счетчик, суммирующий 2п. †разрядн блок, состоящий из (и+1)-разрядного параллельного -сумматора и (и-1)-разрядного реверсивного счетчика, блока управления, состоящего из триггера, прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго элементов И, выходы которых подключены к входу сложения.и вычитания (n-1)разрядного реверсивного счетчика соответственно, шести элементов И, двух элементов -ИДИ, элемента задержки, вход которого соединен с выходом первого элемента ИЛИ и и блоков формирования суммы и переноса (3).

Недостатком известного реверсивного квадратора является сложное построение цепей схемы формирования суммы и переноса, что снижает его надежность.

% Цель изобретения — упрощение схевеа реверсивного квадратора и повышение его надежности.

Указанная цель достигается тем, что квадратор, содержащий и -разрядЕый реверсивный счетчик, суммирую, щий 2п-разрядный блок, состоящий из (и+1) -разрядного параллельного сумматора и (n-1)-разрядного реверсивного счетчика, блок управления, состоящий из триггера, прямой и инверсный выходы которого соединены .с первыми входами соответственно первого

ЗО и второго элементов И, выходы кото9 26652

Рых подключены к входам сложения и вычитания (и -1) -разрядного реверсивного счетчика соответственно, шести элементов И, двух элементов

ИЛИ, элемента задержки, вход которого соединен с выходом первого 5 элемента ИЛИ и и блоков формирования суммы и переноса, блок управления содержит второй триггер, второй элемент задержки, группу элементов

И, причем вход сложения квадратора 1О соединен с единичным установочным входом первого триггера и первыми входами первого и второго элементов

ИЛИ блока управления, а вход вычитания квадратора соединен с нулевым 15 установоччым входом первого триггера и вторыми входами первого и второго элементов ИЛИ, выход второго элемента ИЛИ соединен с единичным установочным входом веерного триггера, единичный выход которого соединен с первым входом третьего элемента И блока управления и с первыми входами элементов И группы, выход третьего элемента И блока управления соедИнен с суммирующим входом и-разрядного реверсивного счетчика, выход первого элемента задержки соединен с входом второго элемента задержки, со счетным входом (и+1)-разрядного параллельного сумматора и с вторыми входами первого и второго элементов

И блока. управления, выход второго элемента задержки соединен с первым входом четвертого элемента И и со вторым входом третьего элемента И блока управления, третий вход которого соединен с единичным выходом первого триггера, второй вход четвертого элемента И соединен с нулевым выходом первого триггера, а вы- 40 ход четвертого элемента И соединен с нулевым установочным входом второго триггера, со счетным входом первого триггера, с третьим входом первого элемента ИЛИ и с вычитающим 45 входом и -разрядного реверсивного счетчика, разрядные. выходы которого подключены ко вторым входам элементов И группы, единичный выход первого триггера соединен с первым входом 50 пятого элемента И блока управления, информационным входом первого разряда (и+1) -разрядного сумматора, прямой выход которого соединен со вторым входом пятого элемента И блока управления, первый и второй информационные входы i-ro разряда (и+1)-разрядного параллельного сум-@ матора подключены к первому и второму выходам 1-ro блока формирования суммы и переноса соответственно, а прямой и инверсный выходы i-го разряда (n+1)-разрядного параллельного сумматора подключены к первому и второму входам блока формирования суммы и переноса, третий и четвертый 65 входы которого соединены с прямым и инверсным выходами соответственно первого триггера блока управления, выход i --го элемента И группы подключен к пятому входу блока формирования суммы и переноса, шестой вход которого, кроме первого блока, подключен к третьему выходу (j-1)-го, кроме и-ro, блока формирования суммы и переноса, выход пятого элемента

И блока управления соединен с шестым входом первого блока формирования суммы и переноса, третьи входы первого и второго элементов И блока управления подключены к третьему выходу п-го блока формирования суммы и переноса.

Кроме того, блок формирования . суммы и переноса содержит четыре элемента И-НЕ и элемент ИЛИ, причем первые входы элемента ИЛИ и первого элемента И вЂ” НЕ соединены с выходом

i-ro элемента И группы, подключенного к пятому входу блока, а их выходы соединены соответственно с первыми входами второго и третьего элементов И вЂ” НЕ и являются первым и вторым выходами блока соответственно, второй и. третий входы третьего элемента И-НЕ соединены с выходами соответственно второго и четвертого элементов И-НЕ, выход третьего элемента И-НЕ является третьим выходом блока, второй и третий входы второго элемента И-НЕ являются соответственно Вторым и четвертым входами блока, первый вход четвертого элемента И-НЕ подключен к выходу элемента ИЛИ, второй и третий входы четвертого элемента И-ЦЕ являются соответственно первым и третьим входами блока, вторые входы элемента ИЛИ и первого элемента И-НЕ блока являются шестым входом блока, выход третьего элемента И-HE n-го блока является третьим выходом п-го блока.

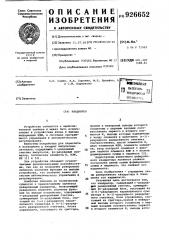

На чертеже приведена функциональная схема устройства.

Схема содержит и -разрядный реверсивный счетчик 1, суммирующий и -разрядный блок 2, состоящий из (n+1)— разрядного параллельного сумматора

3 и (n-1) -разрядного реверсивного счетчика 4, триггеры 5 и 6, элементы ИЛИ 7 и 8, элементы 9 и 10 задержки, элементы И 11-16, блок 17 формирования суммы и переноса, элемент ИЛИ 18, э)цементы И-НЕ 19-22.

Предлагаемое устройство работает следующим образом.

При поступлении импульса логическая единица по входу сложения триггер 5 устанавливается в состояние,при котором на его единичном выходе формируется потенциал логической 1, подача которого в блоки 17 на первые входы элементов

И-HE 20 дает разрешение на опера926652 цию |Сложение ° Одновременно Нос» тупление логической 1 на первый вход элемента И 15 и на управляющий

1 вход триггера младшего разряда сумматора 3 дает разрешение на добавление единицы к числу, записанно- 5 му в блоке 2.

При поступлении импульса логической 1 по входу вычитания триггер 5 устанавливается в положение 0, при котором на его единичном выходе формируется потенциал логического 0, а на нулевом выходе — логической l, подача коt0 торого на первые входы всех элементов И-HE 21 блоков 17 дает разрешение на операцию Вычитание .. Одновременно импульс, поступающий по шине вычитания, пройдя через элементы ИЛИ 7 н ИЛИ 8, соответственно

15 устанавливает триггер 6 в состояние 1 и поступает на вход элемента

9 задержки, С единичного выхода триггера 6 потенциал логической 1 поступает на первые входы всех элементов И 16 и все триггеры счетчика 1 подключаются к элементу 20.

С выхода элемента 9 задержки импульс логической 1 . поступает на вход элемента 10 задержки и на счетные входы всех триггеров сумматора 3, в котором происходит переключение триггеров, у которых на обоих управляющих входах присутствуют потенциалы логической l . ОдновреЗО менно импульс логической 1 с выхода элемента 9 задержки поступает на второй вход элемента И 13, на первом входе которого присутствует потенциал логической 1, 35 поступающий с нулевого выхода триггера 5. При этом, если на 3-ий вход элемента И 13 подан с выхода элемента И-НЕ 22 старшего разряда блока

17.потенциал логической 1, то на выходе элемента И 13 формируется импульс логической 1 переноса, который поступает.на вычитающий вход реверсивного счетчика 4 и вычитает из него единицу. Этой операцией заканчивается вычитание удвоенного числа, записанного в счетчике 1; из числа, записанного в блоке 2, С выхода элемента 10 задержки импульс логической 1 проходит через. элемент И 11, на второй вход которого подан с нулевого выхода триггера

5 потенциал логической 1 и поступает непосредственно на счетный вход триггера 5, вычитающий вход реверсивного счетчика 1, установоч55 ный вход триггера 6 и через элемент

ИЛИ 8 на вход элемента 9 задержки.

Через элемент И 12 импульс не проходит так как на один из его входов

t велю ° подан потенциал логического 0

60 поступающий с единичного выхода триггера 5. При этом установка триггера 6 в нулевое состояние, при котором на первые входы всех элементов

И 16.поступает потенциал логического

65 0 обеспечивает отключение всех

При этом, если триггер младшего разряда сумматора 3 находится в единичном состоянии, то на выходе элемента И 15 формируется логическая 1 переноса, которая поступает в блок 17 формирования суммы и переноса, соединенный с младшим разрядом реверсивного счетчика 1 и вторым разрядом сумматора 3. Одновременно импульс, поступивший по шине сложения, пройдя через элементы .

ИЛИ 7 и ИЛИ 8, соответственно уста.навливает триггер 6 в единичное состояние и поступает на вход элемента

9. задержки. С единичного выхода триггера 6 потенциал логической 1 поступает на первые входы всех Й элементов И 16, при этом происходит подключение всех триггеров реверсивного счетчика 1 к блокам 17 формирования суммы и переноса. С выхода элемента 9 задержки импульс логической l поступает на вход элемента 10 задержки и на счетные входы всех триггеров сумматора 3, в котором происходит переключение триггеров, у которых.на обоих управляющих входах присутствуют потенциалы логической 1 . Одновременно импульс логической 1 с выхода элемента 9 задержки поступает на второй вход элемента И 14, на первом входе которого присутствует потенциал логической 1, поступающий с единичного выхода триггера 5. При этом, если на третий вход элемента И 14 подан с выхода элемента И-HE 22 старшего разряда блока 17 потенциал логической 1 то на выходе элемента

Г

И 14 формируется импульс логичесной 1 переноса, который поступает на суммирующий вход реверсивного счетчика 4. Этой операцией заканчивается сложение удвоенного чисяа, записанного в счетчике 1, с содержимым суммирующего 2п-разрядного бло к 2 плюс единица. С выхода элемента а

ss e °

10 задержки импульс логической 1 через элемент И 12, на другие входы которого поданы потенциалы логической 1, поступает на суммирующий вход реверсивного счетчика 1 и добавляет единицу к записанному ранее числу. Одновременно с выхода элемента 10 задержки импульс поступает на вход элемента И 11, но не проходит через него, так как на второй вход элемента И ll поступает с нулевого выхода триггера 5 потенциал логического нуля. На этом цикл реализации математической зависимости (а+1) - = а + 2q + l заканчивается.

926652 разрядов счетчика 1 от блоков 17.

Поступление импульса на вычитающий вход реверсивного счетчика 1 уменьшает число, записанное ранее, на единицу.

По заднему фронту импульса, поступающего на счетный вход триггера

5, данный триггер устанавливается в единичное состояние и с его единичного выхода на первые входы всех элементов И-HE 20 поступает потенциал логической 1, т.е. форми10 руется разрешение на операцию Сложение, одновременно потенциал логической 1 поступает на управляющий. вход триггера младшего

15 элемента И 15, что дает разрешение на добавление единицы в блоке 2.

С выхода элемента 9 задержки импульс логической 1 поступает

20 на счетные входы всех триггеров.сумматора 3 и в сумматоре происходит переключение тех триггеров, у которых на управляющих входах присутствуют потенциалы логической 1 .

В результате к числу, записанному в блоке 2, добавляется единица.

На этом цикл реализации математической зависимости (c3-1) =ая--2 +

+ 1 заканчивается.

Для пояснения функционирования схемы формирования суммы и переноса рассмотрим работу промежуточного -го разряда блока 2, соединенного с- (1 +1) -ым разрядом сумматора 3 и

1-ым разрядом реверсивного счетчика

1, при различных сочетаниях слагаемых и наличии единицы переноса из предыдущего (-1)-ro разряда.

30

Рассмотрим операцию Сложение .

При сложении на первый вход эле- 40 мента И†HE 20 подан разрешающий потенциал логической 1, а на вход элемента И-НЕ 21 — запрещающий логический 0 °

Ю

Вариант 1. Триггер (+1) -го разряда сумматора 3 находится в единичном состоянии и/или триггЕр -ro разряда реверсивного счетчика 1 находится в единичном состоянии, но отсутствует единица переноса из

50 (-1) -ro разряда, или поступает единица переноса, но триггер i -ro разряда счетчика 1 находится в нулевом состоянии. Тогда на один из входов элемента ИЛИ 18 поступает потенциал логической 1, а на один из входов элемента И-ЙЕ 19 — потенциал логического 0 . При этом на выходах элементов ИЛИ 18 и И-HE 19 формируютая потенциалы логической 1, которые поступают на управляющие входы триггера (+1)-го разряда сумматора 3..Одновременно потенциал логической 1 поступает на второй вход элемента И-НЕ 20, 55

65 разряда сумматора 3 и на первый вход на третий вход которого также подан потенциал логической 1, поступающий с единичного. выхода триггера (+1)-ro разряда сумматора 3.

В результате совпадения трех сигналов логической 1 на входе элемента И-НЕ 20 на его Выходе формируется потенциал логического 0, который поступает на вход элемента

И†HE 22 и на его выходе формируется потенциал логической 1 переноса.

При поступлении импульса на счетный вход триггера (i+1)-ãî разряда сумматора 3 происходит его переключение в нулевое состояние.

Вариант 2 ° Триггер i -ro разряда реверсивного счетчика 1 находится в единичном состоянии и поступает единица переноса из (i-1)-го разряда..Тогда присутствие двух потенциалов логической 1 на входе элемента И-НЕ 19 обеспечивает на его выходе потенциал логического 0, который поступает на управляющий вход триггера (i+1) -го разряда сумматора 3 и на вход элемента И-HE 22, на выходе которого, независимо от состояния триггера (1+1)-го разряда сумматора 3, формируется логическая 1 переноса. При поступлении импульса на счетный вход триггера (t +1) -го разряда сумматора 3 последний не реагирует, так как на его управляющий вход подан запрещающий потенциал логического 0 .

Вариант 3. Триггер -го разряда реверсивного счетчика 1 находится в нулевом состоянии и отсутствует единица переноса из (i-1)-ro разряда. Тогда на выходе элемента ИЛИ 18 формируется потенциал логического 0, который поступает на управляющий вход триггера (i +1)-ro разряда сумматора 3 и на вход элемента

-HE 20, на выходе которого формируется потенциал логической 1 °

На выходе элементов И-НЕ 19 и

И-НЕ 21, в связи с присутствием на их входах потенциалов логических 0, также формируются потенциалы логических 1 . В результате совпадения на входе элемента И-НЕ 22 трех потенциалов логических 1 на его выходе формируется потенциал логического 0, информирующий об отсутствии единицы переноса. При поступлении импульса на счетный вход триггера (i +1) -го разряда сумматора

3 триггер, независимо от его состояния, не реагирует в связи с присутствием на управляющем входе потенциала логического 0 .

Рассмотрим операцию Вычитание .

При вычитании на первый вход элемента И вЂ” НЕ 20 подан запрещающий потенциал логического ™О, на вход926652

10 элемента И вЂ” НЕ 21 — разрешающий логической 1 .

В а р и а н т 1. Триггер (i+1)-ãî разряда сумматора 3 находится в единичном состоянии и/или триггер i -ro разряда реверсивного счетчика 1 находится в единичном состоянии, но отсутствует единица переноса из (i -1)-ro разряда (при операции Вычитание единица переноса является единицей вычитания из более старше- IO го разряда сумматора), или поступает единица переноса, но триггер -го разряда счетчика 1 находится в нулевом состоянии.

Тогда на один из входов элемента (5

ИЛИ 18 поступает потенциал логической 1, на один из входов элемента И-HE 19 — потенциал логического 0 . При этом на выходах элементов

ИЛИ 18 и И-НЕ 19 формируются потенциалы логической 1, которые поступают на управляющие входы триггера (i +1)-ro разряда сумматора 3. Одновременно потенциал логической 1 поступает на первый вход элемента

И-НЕ 22.

Так как на входы элементов И вЂ” НЕ 20 и И-НЕ 21 поступают потенциалы лоO гического 0, то на их выходах фор ру тся потенци "ы логических 30 1, которые поступают на другие входы элемента И-НЕ 22. В результате совпадения трех потенциалов логических 1 на входе элемента

И вЂ” НЕ 22 íà его выходе формируется потенциал логического 0 к инфор мирующий об отсутствии единицЫ переноса. При поступлении импульса на счетный вход триггера (i +1)-ro разряда сумматора 3 триггер переключается в нулевое состояние, 40

В а р и а н т 2. Триггер -го разряда реверсивного счетчика 1 находится в единичном состоянии и поступает единица переноса из (S -1}— го разряда. Тогда присутствие двух 45 потенциалов логической 1 на входе элемента И-НЕ 19 приводит к формированию на его выходе потенциала логического 0, который поступает на управляющий вход триггера 50 (i +1)-го разряда сумматора 3 и иа вход элемента И-НЕ 22, на выходе которого независимо от состояния триггера (1 +1)-го разряда сумматора .3 формируется потенциал логической 1 переноса. При поступлении импульса на счетный вход триггера (i+1)-ro разряда сумматора 3 триггер не реагирует и сохраняет свое первоначальное состояние.

В а р и а н т 3. Триггер (i +1) -го разряда сумматора 3 находится в нулевом состоянии и/или триггер 1-го разряда счетчика 1 находится в единичном состоянии, но отсутствует единица переноса, илн поступает единица переноса нз (-1)-го разряда, но триггер i-го разряда счетчика 1 находится в нулевом состоянии.

Тогда на один из входов элемента

ИЛИ 18 поступает потенциал логической 1, на один из входов элемента И-HE 19 — потенциал логического. 0 . При этом на выходах элементов ИЛИ 18 и И-НЕ 19 формируются потенциалы логической 1, которые поступают на управляющие входы триггера (i+1)-го разряда сумматора 3.

Одновременно потенциал логической 1 поступает на второй вход элемента И-НЕ 21, на третий вход которого также подают потенциал логической 1, поступающий с нулевого выхода триггера (i +1)-го разряда сумматора 3.

B результате совпадения трех сигналов логических 1 на входе элемента И-НЕ 21 на его выходе формируется потенциал логического 0, который поступает на вход элемента И-НЕ 22, и на выходе элемента

И-HE 22 формируется потенциал логической 1 переноса. При поступлении импульса на счетный вход триггера (i+1)-го разряда сумматора:3 происходит его переключение в единичное состояние.

На основании изложенного следует, что введение в блок управления триггера со счетным входом и линии задержки, а в каждый блок формирования суммы и переноса четырех элементов

И-НЕ с описанными выше соединениями, позволит значительно упростить схему реверсивного квадратора и тем самым повысить его .надежность.

Формула изобретения

1. Квадратор, содержащий и -разрядный реверсивный счетчик, суммирующий 2и-разрядный блок, состоящий из (и+1) -разрядного параллельного сумматора и (n-1)-разрядного реверсивного счетчика, блок управления, состоящий из триггера, прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго элементов И, выходы которых подключены к входам сложения и вычитания (и- 1)-: разрядного реверсивного счетчика соответственно, шести элементов И, двух элементов ИЛИ, элемента задержки, вход которого соединен с выходом первого элемента ИЛИ, и И блоков формирования суммы и переноса, отличающийся тем, что, с целью упрощения, блок управления содержит второй триггер, второй элемент задержки, группу элементов И, 9 26652

12 причем вход сложения квадратора соединен с единичным установочным входом первого триггера и первыми входами первого и второго элементов

ИЛИ блока управления, а вход вычитания квадратора соединен с нулевым установочным входом первого триггера и вторыми входами первого и второго элементов ИЛИ, выход второго элемента ИЛИ соединен с единичным установочным входом второго тригге- )О ра, единичный выход которого соединен с первым входом третьего элемента И блока управления и с первыми входами элементов И группы, выход третьего элемента И блока управления соединен с суммирующим входом и-разрядного реверсивного счетчика, выход первого элемента задержки соединен с входом второго элемента задержки, со счетным входом (и+1)— разрядного параллельного сумматора и с вторыми входами первого и второго элементов И блока управления, выход второго элемента задержки соединен с первым входом четвертого элемента И и со вторым входом третьего элемента И блока управления, третий вход которого соединен с единичным выходом первого триггера, второй вход четвертого элемента И соединен с нулевым выходом первого триггера, а выход четвертого элемента И соединен с нулевым установочным входом второго триггера, со счетным входом первого триггера, с третьим входом первого элемента ИЛИ, и с вычитающим входом и-разрядного реверсивного счетчика, разрядные выходы которого подключены ко вторым входам элементов И группы, единичный выход первого триггера соединен с 40 первым входом пятого элемента И блока управления, информационным входом первого разряда (и+1)-разрядного сумматора, прямой выход которого соединен со вторым входом пятого 45 элемента И блока управления, первый и второй информационные входы i --ro разряда (и+1)-разрядного параллельного сумматора подключены к первому и второму выходам:> -ro блока форми- 50 рования суммы и переноса соответственно, а прямой и инверсный выходы -ro разряда (и+1)-разрядного параллельного сумматора подключены к первому и второму входам блока формирования суммы и переноса, третий и четвертый входы которого соединены с прямым и инверсным выходами соответственно первого триггера блока управления, выход i-го элемента И группы подключен к пятому входу блока формирования суммы и переноса, шестой вход которого, кроме первого блока, подключен к третьему выходу (-1)-ro, кроме и -го, блока формирования суммы и переноса, выход пятого элемента И блока управления соединен с шестым входом первого блока формирования суммы и переноса, третьи входы первого и второго элементов И блока управления подключены к третьему выходу и -го блока формирования суммы и переноса.

2. Квадратор по и. 1, о т л ич а ю шийся тем, что блок формирования суммы и переноса содержит четыре элемента И-HE и элемент ИЛИ, причем первые входы элемента ИЛИ и первого элемента И-НЕ соединены с выходом -го элемента И группы, подключенного к пятому входу блока, а их выходы соединены соответственно с первыми входами второго и третьего элементов И-HE и являются первым и вторым выходами блока соответственно, второй и третий входы третьего HE соединены с выходами соответственно второго и четвертого элементов И-НЕ, выход третьего элемента И-HE является третьим выходом блока, второй и третий входы второго элемента И†HE являются соответственно вторым и четвертым входами блока, первый вход четвертого элемента И НЕ подключен к выходу элемента ИЛИ, второй и третий входы четвертого элемента И-HE являются соответственно первым и третьим входами блока, вторые входы элемента ИЛИ и первого элемента И-HE блока являются шестым входом блока, выход третьего элемента И-НЕ п-го блока является третьим выходом п-ro блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 555399, кл. G 06 F 7/38, 1975.

2. Авторское свидетельство СССР

Р 475619, кл. G 06 F 7/38, 1973.

3. Авторское свидетельство СССР

9 674015, кл. G 06 F 7/38, 1977.

926652

Составитель О. Савин

Редактор Н. Кешеля Техред )Х. Кастелевич Корректор А. Дзятко

Заказ 2982/41 Тираж 732 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-. 35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4