Усилитель считывания

Иллюстрации

Показать всеРеферат

Союз Соввтсиик

Социанистмчесиии

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Донолнительное к авт. свнд-ву (5l)N. Кл. (22) Заявлено 29 ° 09. 80 (21) 298643тт/18-2тт с присоединением заявки М

G 11 С 7/00

3Ьеудврстввниый квиитвт

СССР (23) Приоритет по авлзи иэвбрвтвинй и юткрыти1т

Онубликовано 15. 05. 82. Бюллетень И 18 (53) ЯК 681. .327(088.8) Дата онубликования ояисания 17.05.82

В. В. Баранов, Ю. M. Герасимов, H.

А. Н. Кармазинский, П. Б. Поплевин (72) Авторы изобретения янов (71) Заявитель (5тт3 УСИЛИТЕЛЬ СЧИТЫВАНИЯ

Изобретение относится к запоминающим устройствам и может быть исполь", зовано при построении микромощных интегральных запоминающих устройств на дополняющих ИДП-транзисторах.

Известен усилитель считывания, построенный на основе симметричного триггера, в котором затворы нагруэоч. ных транзисторов соединены с разрядныии шинами, а емкости симметричных узлов перед считыванием заряжаются до одинакового потенциала с помощью стробируемых транзисторов (11.

Недостатками этого усилителя являются низкие чувствительность и быстродействие.

Наиболее близким техническим решением к данному изобретению является усилитель считывания для запоминающего устройства на дополняю1 щих ИДП-транзисторах, содержащий первый и второй р-канальные транзисторы, соединенные триггерной связью, истоки которых подключены к шине питания

2 и истокам р-канальных транзисторов первого и второго интерторов, причем сток первого р-канального транзистора соединен с входом первого инвертора и .стоком первого нагруэочного и-канального транзистора, сток второго р-канального транзистора соединен с входом второго инвертора и стоком второго нагруэочного A-êàíàëüного транзистора, входы первого и второго- инверторов соединены соответственно с первым и вторым выходами усилителя, затворы первого и вто.рого нагрузочных и-канальных транзисторов соединены соответственно с

1S первой и второй разрядными шинами, истоки. - со стоком ключевого и-канального транзистора, затвор которого соединен с первой шиной управле"

20 ния, исток - с общей виной, истоки и-канальных транзисторов первого и второго инвертора соединены со стоком ключевого и-канального транзистора, к первой вине управления подключен

928406 затвор симметрирующего транзистора, исток которого связан с входом первого инвертора, а сток - с входом второго инвертора Г23.

Недостатками известного усилителя являются низкая чувствительность и низкое быстродействие, обусловленное отсутствием управления напряжениями отпираний транзисторов с помощью напряжения на разрядных шинах.

Цель изобретения - повышение чувствительности и быстродействия усилителя.

Поставленная цель достигается тем, что в усилитель считывания, содержащий первый и второй переключающие р-канальные. транзисторы, соединенные по триггерной схеме, нагруэочные и ключевой и-канальные транэист ры, первый и второй инвертирующие р-канальные транзисторы и третий и четвертый инвертирующие и-канальные транзисторы, причем сток первого переключающего транзистора подключен к стоку первого нагрузочного и затворам первого и третьего инвертирующих транзисторов, сток второго переключающего транзистора соединен с затворами второго и четвертого инвертирую30 щих транзисторов и стоком второго нагрузочного транзистора, истоки нагрузочных транзисторов подключены к стоку ключевого транзистора, исток которого соединен с шиной нулевого потенциала, а затвор являетея первым управляющим входом усилителя, истоки первого и второго инвертирующих транзисторов подключены к шине питания, затворы первого и второго нагрузочных транзисторов являются соответственно 4О первым и вторым входами усилителя, стоки первого и :третьего инвертирующих транзисторов объединены и являются первым выходом усилителя, а стоки второго и четвертого инвертиру- 45 ющих транзисторов объединены и являются вторым выходом усилителя, введены третий и четвертый переключающие р-канальные транзисторы, соединенные по триггерной схеме, управляющие р-канальные и разрядные и-канальные транзисторы, причем стоки третьего переключающего и первых управляющего и разрядного транзисторов соединены с истоком первого пе- 55 реключающего транзистора и затвором второго нагрузочного транзистора, стоки четвертого переключающего и. вторых управляющего и разрядного транзисторов соединены с истоком второго переключающего транзистора и затвором первого нагруэочного транзистора, истоки третьего и четвертого переключающих и первого и второго управляющих транзисторов подключены к шине питания, затворы первого и второго управляющих транзисторов соединены с затвором третьего разрядного транзистора и являются вторым управляющим входом усилителя, истоки первого и второго разрядных транзисторов подключены к стоку третьего разрядного транзистора, исток которого и истоки третьего и четвертого инверторных транзисторов соединены с истоком ключевого транзистора, затворы первого и второго разрядных транзисторов подключены соответственно к стоку первого и к стоку второго инвертирующих транзисторов, исток и сток третьего управляющего транзистора соединены соответственно с истоком и затвором первого инвертирующего транзистора, исток и сток четвеотого управляющего подключены соответственно к истоку и затвору второго инвертируащего транзистора, затворы третьего и четвертого управляющих транзисторов соединены с затвором ключевого тран-. зистора.

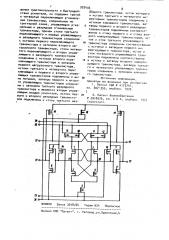

На чертеже приведена принципиальная схема усилителя считывания.

Усилитель содержит первый 1 и второй 2 переключающие р-канальные .транзисторы, первый 3 и второй 4 нагрузочные и-канальные транзисторы., ключевой 5 и-канальный транзистор, первый 6 и второй 7 р-канальные, третий 8 и четвертый 9 п-канальные инвертирующие транзисторы, третий 10 и четвертый 11 р-канальные переключающие транзисторы, первый

12, второй 13, третий 14 и четвертый 15 р-канальные управляющие транзисторы, первый 16, второй 17 и третий 18 и-канальные разрядные транзисторы; На чертеже обозначены первый 1 и второй 20 входы, первый

21 и второй 22 выходы, первый 2) и второй 24 управляющие входы усилителя, содержащего также шину 25 питания и шину 26 нулевого потенциала. На чертеже обозначены также сток

27 первого и сток 28 второго пере ключающих транзисторов. Входы 1g и 20 усилителя подключаются через

6 4 ванию транзистора 16. Через транзисторы lб и 18 происходит разряд ем" кости шины блока памяти, подключен" ной к входу 20, в результате чего открывается .транзистор 11 и закрывается транзистор 4. При этом на стоке

28 транзистора 2 устанавливается уровень логической единицы, и исклю" чается сквозное протекание тока через усилитель после его переключе" ния. Йосле окончания переходного процесса на выходе 21 устанавлива ется уровень логической единицы, а на выходе 22 - уровень логического нуля.

Технико-зкономическое преимущество предложенного усилителя закюеочается в более высоких, по сравнение с известным,быстродействии и чувствительности.

92840

Усилитель считывания, содержащий первый и второй. переключающие р-канальные транзисторы, соединенные по триггерной схеме, нагруэочные и ключевой п-канальные транзисторы, первый и второй инвертирующие р-канальные транзисторы и третий и четвертый инвертирующие (i-канальные транзисторы, причем сток первого переключающего транзистора подклю" чен к стоку первого нвгрузочного и затворам первого и третьего инаертирующйх транзисторов, сток второго переключающего транзистора соединен с затворами второго и четвертого инвертирующих:транзисторов и стоком нагруэочного транзистора, истокьВ нагрузочных транзисторов подI ключены к стоку ключевого транзис тора, исток которого соединен с ши" ной нулевого потенциала, а -:затвор является первым управляющим входом усилителя, истоки первого и второго инвертирующих транзисторов подключены к шине питания, затворы первого и второго нагрузочных транзисторов яв- ляются соответственно первым и вто" рым входами усилителя, стоки первого и третьего инвертирующих транзисторов объединены и является первым выходом усилителя, а стоки второго и четвертого инвертирующих транзисторов объединены и являются вторым выходом усилителя, о т fl и ч а юшийся тем, что, с целью поаы5 соответствующие разрядные шины и

1 дополнительные транзисторы а запоминающем устройстве (на чертеже не показаны) к запоминающим элементам блока памяти (на чертеже .не показанным).

Усилитель считывания работает следующим образом.

B режиме хранения напряжение на шинах управления 23 и 24 соответ- 1р стаует уровню логического нуля, на входах 19 и 20 - уровню логической единицы. Транзисторы 8, 9, 12 - 15 открыты, и на стоке 27 транзистора

1 и стоке 28 транзистора 2 устанав- г$ ливаются уровни логической единицы, а на выходах 21 и 22 — уровни логического нуля.

В режиме считывания первоначально подается сигнал логической едини- 26 цы на вход 24. При этом закрываются транзисторы 12 и 13, и входы 19 и

20 усилителя оказываются изолироаан- Формула .

Фо и ла . изобретения ными от шины питания 2Sj Через один из входов, например 20, начинает протекать ток считывания от выбранного элемента блока памяти (на чертеже не показанного). Изменения напряжения на входах 19 и 20 приводит к изменению проводимости нагрузочных транзисторов 3 и 4, а также к изменению напряжений на стоках 27 и

28 соответственно транзисторов 1 и 2, т.е. к изменению напряжений отпирания транзисторов 1 и 2. Если не учитывать влияние напряжения между подложкой и истоком транзисторов l и 2 на их пороговые напряжения, то изменение напряжения отпирания транзисторов l и 2 равно изменению напряжения на входах 19 и 20. Изменение напряжения между подложкой и истоком транзисторов 1 и 2 приводит к изменеР нию пороговых напряжений транзистороа 1 и -2. Это приводит к дополнительному изменению напряжений отпирания транзисторов 1 и 2. После. того как напряжение на входах 19 и 20 превысит некоторую величину (разбаланс усилителя), на первый управляющий вход 23 подается сигнал логической единицы. Транзистор 5 открывается, и а усилителе происходит регенеративный процесс. На стоке 27 транзистора 1 начинает устанавливаться

$$ уровень логического нуля, а на стоке 28 транзистора 2 - уровень логической единицы. Транзисторы б и 8 переключаются, что приводит к откры8

ВНИИПИ Заказ 3248/64 Тираж 624 Подписное филиал ППП "Патент", r. Ужгород,ул.Проектная,4

/ 92340 вения чувствительности и быстродействия усилителя, он содержит третий и четвертый переключающие р-канальные транзисторы, соединенные по триггерной схеме, управляющие р-канальные и разрядные и-канальные транзисторы, причем стоки третьего переключающего и первых управляющего и разрядного транзисторов соединены с истоком первого переключающего, 10 транзистора и затвором второго нагрузочного транзистора, стоки четвертого. переключающего и вторых управляющего и разрядного транзисторов соединены с истоком второго пере- 15 ключающего транзистора и затвором первого нвгрузочного транзистора, истоки третьего и четвертого пере-, ключающих и первого и второго управляющих транзисторов подключены к ши- 20 не питания, затворы первого и второго управляющих транзисторов соединены с затвщюм третьего разрядного транзистора и являются вторым управляющим входом усилителя, истоки пер- 2s вого и второго разрядных. транзисторов подключены к стоку третьего раэI

6. рядного транзистора, исток которого и истоки третьего и четвертого инверторных транзисторов соединены с истоком ключевого транзистора, затворы первого и второго разрядных транзисторов подключены соответственно к стоку первого и к стоку второго инвертирующих транзисторов, исток и сток третьего управляющего транзистора соединены соответственно с истоком и затвором первого инвертирующего транзистора, исток и сток четвертого управляющего транзистора подключены соответственно к истоку и затвору второго инвертирующего транзистора, затворы третьего и четвертого управляющих транзис— торов соединены с затвором ключевого транзистора.

Источники информации, принятые во внимание при экспертизе

Патент США Ю 4170741, кл. 307-355, опублик. 1979.

2. Патент Великобритании

tf 201807б, кл. G 4 А, опублик. 979 прототип).