Устройство для управления регенерацией в блоках оперативной памяти

Иллюстрации

Показать всеРеферат

Д;А. Бруевич, P.Ì. Воробьев и А.Г. Куликрв, (72) Авторы изобретения (7l ) Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ

В БЛОКАХ ОПЕРАТИВНОЙ ПАМЯТИ

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства местного управле ння оперативных накопителей, выполненных . на элементах памяти с ограниченным вре.- менем хранения информации.

Известно устройство для управления регенерацией в блоках оперативной памя ти, содержащее формирователь сигналов регенерации, четыре одновибратора режима регенерации, четыре одновибратора режима внешнего обращения, формирова тель синхронизирующих сигналов, три инвертора, два элемента 2И-НЕ и один элемент 4И НЕ (l).

Недостаток устройства заключается в его сложности.

Наиболее близким техническим решением к предлагаемому является year ройство для управления регенерацией 20 в блоках оперативной памяти, содержащее формирователь синхронизирующих сигна лов, формирователь сигналов регенерации, триггер режима, управляющую шину, триг гер конца цикла и два элемента И НЕ, причем выходы. триггера режима соедийе ны со входами первого элемента И-НЕ, выход которого. соединен со входом формирователя синхронизирую1пих сигналов, входы триггера режима соединены corn ветственно с управляющей шиной и одним из входов второго элемента И-НЕ, с выходом того же элемента и выходом формирователя сигналов регенерации„другой вход второго элемента И-НЕ соединен с единичным. выходом триггера конца пик ла, входы которого соединены соответственно с управляющей шиной и saeoäoì формирователя синхронизирующих сигналов $2).

Недостаток устройства - его сложность, а также то, что при отсутствии обращенной цо управляющей шине и запро

eos с формирователя сигналов регенера ции, устройство не запускается и нахо дится в выжидающем режиме, что casжает его быстродействие.

213

50

3 94

Бель изобретения - упрощение устрой ства.

Поставленная цель достигается тем, что в устройстве для управления регенерацией в блоках оперативной памяти, со.держащем триггер, элементы И-НЕ и формирователь сигналов регенерации и синхросигналов, причем прямой и инверсный выходы триггера соединены соотвеъст-.енно со входами первого элемента

И-НЕ, а первый вход триггера является входом устройства, выход первого элемента И-НЕ подключен к первому входу второго элемента И-НЕ, выход которого соединен со входом формирователя сигналов регенерации и синхросигналов, один из выходов которого Подключен ко второму входу второго элемента И-НЕ и вто,.— рому входу триггера, другие выходы формирователя сигналов регенерации и синхросигналов являются выходами устройства.

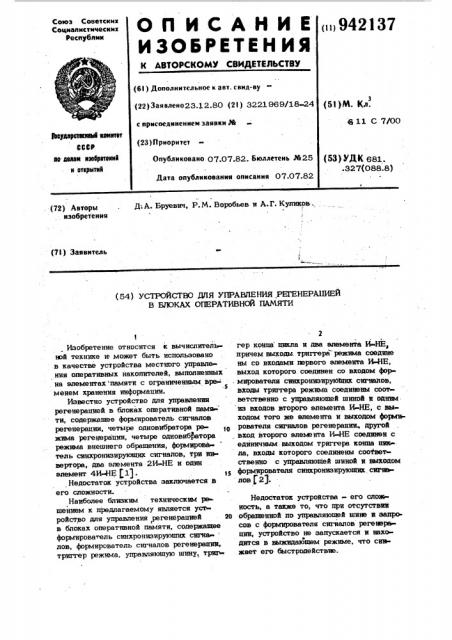

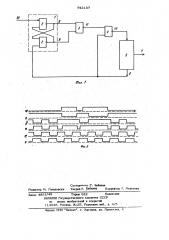

На фиг. 1 представлена функциональная схема устройства, на фиг. 2 - временная диаграмма его работы.

Устройство содержит триггер 1, выполненный на элементах И-HE 2, пер" . вый 3 и второй 4 элементы -HE и формирователь 5 сигналов регенерации и синх-. росигналов с одним из выходов 6 и други з

Ъ ми выходами 7, выходы 8 и 9 и первый вход 10 триггера, выход 11 первого эле-мента И КЕ и выход 1 2 второго элемента

Н-НЕ. Формирователь 5 построен на основе полупроводниковой линии задержки (не по- 3 казак).

На фиг. 2 изображены сигналы на входе 10 устройства, на выходах 8 и 9 триггера, на выходе 11 первого элемента -HE, на выходе 12 второго.элемента И-НЕ и сигналы синхрощкэации на выходе 6 формирователя сигналов регенерации и синхросигналов. !

Устройство работает следующим обра зом.

В исходное состояние при отсутствии обращенной к .устройству на входе 3 присутствует низкий уровень напряжения, а на выходе 8 (фиг. 2) триггера 1 - вы сокий.

При появлении сигнала на входе формирователя 5 на его выходе 6 выдается сигнал в той же фазе спустя некоторое время, равное половине длительнос-, ти цикла блока оперативной памяти (под длительностью цикла понимается время, необходимое для записи или чтения информации и подготовки к приему следукь7 4 щего запроса). Таким образом, в исходном состоянии получается замкнутая цепь из трех инвертирующих и одного неинвертирующего элемента (плечо триггера 1 элемента И-HE 3 и 4 и формирователь 5)

1 в которой происходит генерация сигналов с периодом, равным длительности цикла

1, причем в каждом цикле формирователь 5 вырабатывает все необходимые сигналы дпя режима регенерации. Таким образом, при отсутствии внешних обращений к блоку. оперативной памяти происходит непрерывная регенерация информации в нем с максимально возможной частотой. Признаком режима регенерации являются отрицательные сигналы длительностью < на выходе 9 (фиг.2) триггера 1.

При появлении. положительного сигнала на выходе 6 (фиг. 2), передний фронт этого сигнала совпадает с моментом готовности блока памяти к приему следующего запроса), на выходе 9 вырабатывается низкий уровень напряжения, а на выходе 11 (фиг. 2) И-НЕ 3 - вь .сокий, который затем поступает на первый вход элемента И-НЕ 4, на втором входе которого присутствует уровень с выхода 6 формирователя 5. При этом на выходе 12 элемента И-НЕ 4 и на входе формирова теля 5 оказывается низкий уровень напряжения. Формирователь 5 запускается и вырабатывает все сигналы, необходимые для режима регенерации. Спустя поповину длительности цикла Ь низкий уровень напряжения с выхода элемента,, И-НЕ 4 проходит всю линию задержки формирователя 5 и оказывается на вых . де 6, после чего на выходе 12 вновь возникает высокий уровень напряжения.

Одновременно сбрасывается низкий уровень нащижения на выходе 9. На входах элемента И-НЕ 3 оказываются высокие уровни напряжения, а на его выхо де 11 низкий уровень напряжения, ко торый поддерживает высокий уровень напряжения на,выходе 12 (фиг. 2). Прохождение положительного сигнала через формирователь Ц составляет вторую половину цикла Г, и при появлении этого сигнала на выходе 6 работа устройства повторяется, но уже для нового адреса

pere íåðàöèè.

Рассмотрим работу устройства при поступлении запросов на его вход.

Пусть в момент, когда на выходе 6 формирователя 5 присутствует низкий уровень напряжения, по входу 10 (фиг. 2) поступает запрос от внешне.о устройства.

Устройство для управления регенерацией в блоках оперативной памяти, со держащее триггер, элементы ИНЕ и формирователь сигналов регенераций и синхросигналов, причем прямой и инверс ный выходы триггера соединэны соответственно с входами первого элемента И-НЕ, а первый вход триггера является входом устройства, отличающееся тем, что, с целью упрощения устройства, выход первого элемента И-HE подключен к первому входу второго элемента И НЕ, выход которого соединен с входом формирователя сигналов регенерации и cRRcросигналов, один из выходов которого подключен к второму входу второго эпэ мента И-НЕ и второму входу триера, другие выходы формирователя сигналов регенерации и синхросигналов являются выходами устройства.

Источники информации, принятые во вниманю при экспертизе

1. Патент Великобритании М 142410 7, кл. О06Г 9100, опублик. 1976.

2. AsTîðñêîe свидэтельство СССР

% 752338, кл. <ЬО6F 9/00,.197ь (прототип) .

5 9421

На выходе 9 в это время находится высокий уровень напряжения, поэтому на выходе 8 (фиг. 2) сразу же возникает низкий уровень напряжения, а на вы— ходе 11 - высокий. Однако новый запуск 5 формирователя 5 не происходит, так как на втором входе элемента И-НЕ 4 все еще присутствует низкий уровень напряжения с выхода 6. После завершения текущего цикла на выходе 6 оказывается высокий уровень напряжения, а на выходе 12 - низкий. С этого момента начинается новый цикл работы устройства и блока памяти по обслуживанию внешнего обращения, признаком которого является низкий уровень напряжения на выходе 8 триггера 1. После удовлетворения текущего запроса внешнее устройство снимает признак обращения на входе 10, на выходе 8 возникает высокий уровень на- 20 пряжения, а на выходе 11 - низкий, подтверждая тем самым высокий уровень напряжения на выходе 12 элемента И-НЕ, по завершении подготовки блока памяти к приему следующего запроса, т. е. поо- 2S ле окончания цикла, на выходе 6 форми рования 5 появляется высокий уровень напряжения, и возобновляется режим регенерации. В случае, если запрос по входу 10 поступает в момент, когда на вы- зо ходе 6 присутствует высокий уровень напряжения, то потенциалы выходов триггера нэ изменяются (на выходе 8 - вы:сокий потенциал, на выходе 9 - низкий) до тех пор, пока на выходе 6 не появляется низкий уровень напряжения..В дальнейшем устройство работает, как описано выше.

Технико-экономическое преимущество предложенного устройства заключается. 4Э

37 6 в том, что оно позволяет существенно сократить, по сравнению с известным, количество элементов, необходимых для

1 его регенерации, и за счет этого упростить его, а также в повышении надежности устройства эа счет более высокой частоты сигнала регенерации,, Формула из обре те ния

Состав аль «Т. Зайнева

Редактор М. Голаковски Техред А Вабииеи Корректор Г. Решетняк

Заказ 4851/45 Тираж 622 Подписное

ВИИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, -35; Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4