Устройство для контроля интегральных операционных усилителей

Иллюстрации

Показать всеРеферат

Союз Советск ик

Социапистичесиик республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I ) Дополнительное к авт. свид-ву (22) аявлено Об. 01. 81 (21) 3231357/18-21 (53 ) M. Кл.

G 01 R 3 /28 с присоединением заявки №

1Ьеударстваеьй квинтет

СССР ав аелаи кэебретекик и открытки (23) Приоритет

Опубликовано 23.07.82. Бюллетень № 27 (5З) УЙК бг1. 317. .008(088.8) Дата опубликования описания 23. 07, 82

А. А. Богородицкий, Л. Д. Гарин, В. А. Каз ков, д. УГУ М йаин и Б.В.цыпии 1 1 Йййищр. (72) Авторы изобретения %341

Пензенский политехнический институт и П нзе л

Всесоюзного научно-исследовательского технологиче института приборостроения (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИНТЕГРАЛЪНЫХ

ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ

Изобретение относится к контрольноиспытательной технике и может быть использовано для контроля исправности интегральных операционных усилителей . в составе электронных блоков.

Известно устройство контроля усилителей, содержащее компаратор, формирователь импульсов, элемент совпа-, дения, формирователь и триггер индикации Pl).

1О

Однако это устройство обладает недостаточными функциональными воз\ можностями, так как не позволяет

< контролировать усилители, вмонтированные в электронный блок.

Наиболее близким техническим решением к изобретению является устройство для контроля интегральных схем, содержащее преобразователь код-напряжение, усилитель,коммута- 2в тор, блок управления, запоминающие элементы, измеритель и индикатор 12).

Недостатком известного устройства являются также низкие функциональные воэможности, так как оно не может быть использовано для контроля интегральных операционных усилителей, включенных в рабочую схему и распаянных на плату.

Цель изобретения - расширение функциональных возможностей, заклю-. чающихся в контроле интегральных операционных усилителей, включенных непосредственно в рабочую схему.

Поставленная цель достигается тем, что в устройство, содержащее усилитель и индикатор, вводятся зле мент ИЛИ, три элемента совпадения, инвертор, два пороговых элемента, источник опорных напряжений, два фильтра постоянной и составляющей напряжения и блок вычитания, причем входы блока вычитания соединены параллельно входам проверяемого интегрального операционного усилителя, а выход его соединен через первый фильтр постоянной составляющей с входом первого порогового эле-, соединены с входами элемента ИЛИ 12, выход которого соединен с входом индикатора 13. Выход проверяемого интегрального операционного усилителя 14 соединен через второй фильтр

3 постоянной составляющей с входом усилителя 5., Устройство работает следующим образом.

Напряжения, действующие непосредственно на прямом Q + и инвертирующем U -входах проверяемого интегрального операционного усилителя 14, подаются на входы блока 1 вычитания.

Выходное напряжение блока 1 вычитания Ц, = U+ — 1-1- равно разностному сигналу, действующему на входах проверяемого интегрального операционного усилителя t4. С помощью фильтра 2 постоянной составляющей выделяется постоянная составляющая напряжения 0,р = д — О, „ и подается на входы соответственно прямой и инвертирующий, пороговых элементов

7 и б. Входы "1" пороговых элементов

6 и 7 являются прямыми, а входы "2"инвертирующими, обозначаются на функциональной схеме знаками + и соответственно. Пороги срабатывания пороговых элементов б и 7 задаются источником 4 опорных напряжений равными паспортным предельно допустимым для данного типа операционного усилителя значениям, соответственно положительного Ос м,+ и отрицательного Ос.мо-напряжения смещения нуля.

Пороговый элемент 6 выдает на входы элементов 9 и 11 совпадения сигнал логической единицы при Ос.во Ос.пост и сигнал логического нуля при

Ос.мо < 0 А.пост . Пороговый элемент 7 выдает на входы .элементов 9 и 10 совпадения сигнал логической единицы при !с.мо "д Ои сиг нал логического нуля при Осло)цд пост.

На вторые входы элементов 10 и 11 совпадения подается выходной сигнал усилителя 5, причем нЛ элемент 11 совпадения через инвертор

8. Выходной сигнал усилителя .5 соот. ветствует логической единице, если постоянная составляющая выходного напряжения проверяемого интегрального операционного усилителя 14

U „ „ с-,, выделенная фильтром 3 постоянной составляющей, больше нуля, и соответствует логическому нулю, если 0 пои,.пост

3 945831 4 мента и входом второго порогового элемента, другие входы которых соединены с соответствующими выходами источника опорных напряжений, выход первого порогового элемента S соединен с входом первого элемента совпадения и входом третьего элемента совпадения, второй вход которого.ñoåäèHåH с выходом инвертора, а второй вход первого элемента совпа- 1о дения соединей с выходом второго порогового элемента и с входом второго элемента совпадения, второй

\ вход которого соединен с входом инвертора и через усилитель и второй

15 фильтр постоянной составляющей соединен с выходом проверяемого интегрального операционного усилителя, выходы всех трех элементов совпадения соединены с входами элемента ИЛИ, выход которого соединен с входом индикатора.

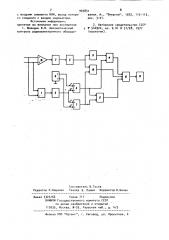

На чертеже представлена функциональная схема устройства.

Устройство содержит блок 1 вычитания, первый 2 и второй 3 фильтры . постоянной составляющей, источник 4 опорных напряжений, усилитель 5, первый 6 и второй 7 пороговые элементы, инвертор 8, первый 9 и второй 10 элементы совпадения, третий элемент

11 совпадения, элемент ИЛИ 12, индикатор 13 и проверяемый интегральный операционный усилитель 14.

Входы блока 1 вычитания подключа35 ются параллельно входам проверяемого интегрального операционного усилите-. ля 14. Выход блока 1 вычитания соединен через первый фильтр 2 постоянной составляющей с вторым входом первого порогового элемента 6 и первым входом второго порогового элемента 7. Другие входы пороговых элементов 6 и 7 соединены с выходами источника 4 опорных напряжений.

Выход первого порогового элемента 6 соединен с входами первого 9 и третьего 11 элементов совпадения.

Второй вход третьего элемента 11 совпадения соединен с выходом инверсо тора 8. Второй вход первого элемента

9 совпадения соединен с выходом второго .порогового элемента 7. Выход второго порогового элемента 7 соединен с входом в1 орого элемента 10 совпадения. Второй вход второго элемента !О совпадения соединен с входом инвертора 8 и выходом усилителя

5. Выходы элементов 9-11 совпадения

Выходные сигналы элементов 9-11 совпадения подаются на входы эле .мента ИЛИ 12, который выдает на индикатор 13 сигнал "Годен" - сигнал логической единицы при наличии единицы хотя бы на одном из входов.

На выходе элемента 9 совпадения сигнал логической единицы возникает, когда разностный сигнал, действующий на входе проверяемого интегрального операционного усилителя 14, меньше по абсолютной величине Ос до. При этом проверяемый интегральный операционный усилитель диагностируется как годный. В остальных случаях на выходе схемы 9 совпадения сигнал логического нуля.

На выходе элемента 10 совпадения сигнал логической единицы появляется, если на выходе порогового элемента

7 и усилителя 5 есть сигнал логической единицы. Это соответствует

Цд вост 0 и 0 поц п<ут70. При этом про- . веряемый интегральный операционный усилитель диагностируется как годный. В остальных случаях на выходе элемента 10 совпадения сигнал логического нуля, На выходе элемента 11 совпадения сигнал логической единицы появляется, если на выходе порогового элемента 6 есть сигнал логической единицы, а на выходе усилителя 5 есть сигнал логического нуля. Это соответс1 вует Ug поф Опоило ОПри этом проверяемый интегральный операционный усилитель диагностируется как годный. В ост«льных случаях на выходе элемента 11 совпадения сигнал логического нуля.

Таким образом, предлагаемое устройство контролирует исправность интегральных операционных усилителей путем определения соответствия знака выходного напряжения контролируемого интегрального операционного усилителя знаку его разностного входного напряжения. Введение фильтров 2 и 3 постоянной составляющей позволяет исключить влияние на результат контроля возникающих вследствие ограниченной частотной характеристики интегрального операционного усилителя фазовых сдвигов и нелинейных искажений выходного сигнала интегрального операционного усилителя относительно входных,которые могут быть произвольной формы и амплитуды.

5831

Введение пороговых элементов 6 и

7 и источника 4 опорных напряжений позволяет исключить неверный результат контроля в тех случаях, когда абсолютная величина разности входных напряжений интегрального операционного усилителя меньше допустимого U „„ . Знак выходного напряжения интегрального операционного усилителя при этом может быть любым.

Такое построение устройства K(нтроля интегральных операционных усилителей позволяет осуществлять проверку исправности интегральных операционных.усилителей непосредственно в рабочей схеме без выпаивания при наличии любых внешних цепей и любых сигналов на входе контролируемого интегрального операционного усилителя.

1о

Формула изобретения

Устройство для контроля интеграль. ных операционных усилителей, содержащее усилитель и индикатор, о тл и ч а ю щ е е с я тем, что, с . целью расширения функциональных воззо можностей, в него введены элемент

ИЛИ, три элемента совпадения, инвертор, два пороговых элемента, источник опорных напряжений, два фильтра постоянной составляющей напряжения и блок вычитания, причем входы блока вычитания соединены параллельно входам проверяемого интегрального операционного усилителя, а выход его соединен через первый фильтр постоян4О ной составляющей с входом первого порогового элемента и входом второго порогового элемента, другие входы которых соединены с соответствующими выходами источника опорных напряжений, выход первого порогового элемента. соединен с входом первого элемента совпадения и входом третьего элемента совпадения, второй вход которого соединен с выходом инвертора, а второй вход первого элемента совпадения соединен с выходок второго порогового элемента и входом второго элемента совпадения, второй вход которого соединен с входом инвертора

55 и через усилитель и второй фильтр постоянной составляющей соединен с выходом проверяемого интегрального операционного усилителя, выходы всех трех элементов совпадения соединены

Составитель В.Гусев

Техред 3. Палий Корректор О.Билак

Редактор Н.Кацалап

Заказ 5325/66 Тираж 717 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 с входами элемента ИЛИ, выход которо го соединен с входом индикатора.

Источники информации, принятые во внимание при экспертизе

1. Шляндин В.M. Автоматический контроль радиоэлектронного оборудо945831 8 вания. И., "Энергия"., 1972, 112-113, рис. 3-21.

2. Авторское свидетельство СССР

11 544924, кл. G 01 R 31/28, 1977 (прототип).