Устройство для вычисления логических выражений @ переменных

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

«»962918 (61) Дополнительное к авт. свид-ву— (22) Заявлено 040181 (2! ) 3230824/18-24 с присоединением заявки М— (23) Приоритет

Опубликова о 30,0982. Бюллетень М 36 ($g) + К т э

С 06 F 7/00

Государственный комитет

СССР но делам изобретений н открытий (ЩУДК 681.3 (088.8) Дата опубликования описания 30.09.82 (72) Авторы изобретения

A.Â. Гурьянов, В.Д. Козюминский, В.A. Мищенко, и A.Н. Семашко (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГИЧЕСКИХ

ВЫРАЖЕНИЙ 6 ПЕРЕМЕННЫХ

Устройство относится к вычислительной технике и автоматике, предназначено для вычисления значений логических выражений и может использоваться при построении комбинационных узлов и цифровых автоматов.

Известны устройства, которые могут использоваться для вычисления логических выражений, например универсальный логический модуль, содержащий п информационных и 2 управи ляющих входов, и элементов НЕ, 2" элементов И и элемент ИЛИ, выход которого является выходом устройства, а его входы подключены к выходам элементов И, первые входы которых управляющие, а остальные и входов подключены соответствующим образом к выходам элементов НЕ и информационныч входам устройства. Устройство путем настройки реализует любые логические функции входных булевых переменных (1 1.

Недостатком известного устрой.ства является большая сложность. 25

Наиболее близким к предлагаемому по технической сущности является устройство, которое имеет каскадную структуру и содержит 2п1 универсальных логических модулей, инфор- 30 мационные входы которых подключены к и-м информационным входам устройства, а их управляющие входы являются управляющими входами устройства, выходы универсальных логических модулей подключены к входам коммутатора, управляющие вхрды которого подключены к остальным а информационным входам модуля (2).

Недостатком известного устройства является сложность, что не позволяет использовать его при обработке многоразрядной информации. Например, при и = 10, m = 5 и использовании универсальных логических модулей с двухъярусной канонической структурой схема устройства будет иметь сложность по суммарному числу входов логических элементов, равную 7590.

Ф

Цель изобретения — упрощение устройства для вычисления логических выражений.

Поставленная цель достигается тем, что устройство для вычисления логических выражений и переменных, содержащее два мультиплексора, выход первого мультиплексора является выходом устройства, управляющие входы первого мультиплексора под962918

45

65 ключены к m информационным входам устройст à, n-"m информационные входы второго мультиплексора подключены к информационньм входам устройст ва, управляющие входы которого подключены к управляющим входам второго мультиплексора, содержит блок памяти, входы записи которого подключены к выходу второго мультиплексора, а входы управления - к дополнительным управляющим входам устройства, выходы блбка памяти подключены к информационным входам первого мультиплексора.

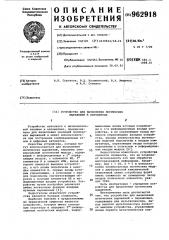

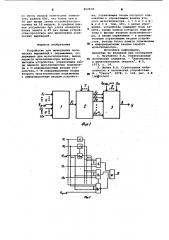

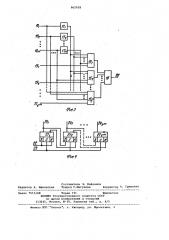

На фиг.1 представлена схема устройства; на фиг.2 — схема входного мультиплексора на Фиг.3 — схема выходного мультиплексораf на фиг.4 вариант блока памяти.

Схема устройства для.вычисления логических выражений и переменных (фиr.1) содержит мультиплексор 1, блок 2 памяти, мультиплексор 3, группы информационных входов 4 и 5, управляющие входы б, входы 7 управления блоком памяти и выход 8.

Схема мультиплексора 1 (фиг.2) содержит 2" и элементов И 9, элемент ИЛИ 10, п-m элементов НЕ 11, n"m информационных входов 12, 2" управляющих входов 13 и выход 14.

Схема мультиплексора 3 (фиг.3) содержит 2 элементов И 15, элемент ИЛИ 16, m элементов НЕ 17, m управляющих входов 18, 2" информационных входов 19 и выход 20.

Схема блока 2 памяти (фиг.4) на сдвиговом регистре содержит 2 триггеров 21, вход 22 записи, управляющий синхровход 23 и 2 выходов 24

В схеме устройства (Фиг. 1) информационные входы мультиплексора 1 подключены к группе п — m информационных входов 4 устройства, а управляю-. щие входы мультиплексора 1 подключены к управляющим входам б устройства. Выход модуля 1 подключен к входу записи блока 2 памяти, 2 выходов которого подключены к информациоНННМ входам мультиплексора 3, управляющие входы которого подключены к группе т информационных входов 5 устройства. Выход мультиплексора 3 является выходом 8 устройства.

Устройство работает следующим образом.

На информационные входы 4 устройства подаются входные сигналы х х2,..., х,„, которые поступают на информацио™нежные входы мультиплексора, который с помощью сигналов управления U., 02,..., U„, подаваемых на управляющие входы устройства, манжет быть настроен на выполйение любой логической функции

f(х„, х„ „,) входных информацион-ных переменных. Например, для настройки мультиплексора (фиг.2) достаточно положить значения сигналов и„, i = 1, 2" равными значениям реализуемой логической функции

f(x, x„ „ ) на соответствующих i-ых выборах аргументов х,, х2,..., х„ п, которые реализуются элементами И 9 .

Значения реализуемых логических функций записываются в блок памяти.

В простейшем случае блок памяти представляет собой сдвиговый 2™-разрядный регистр. Запись значений реализуемых логических функций производится блоком памяти по сигналам управления, подаваемым на входы 7 устройства. При использовании сдвигающего регистра (фиг.1) запись производится, например,по сигналу сдвига, подаваемому на синхровход 23 регистра.

Таким образом, в блок памяти могут быть записаны значения 2п логических функций f;-(x „, x„ ), О, (2" - 1), которые они принимают на некотором фиксированном наборе входных переменных х„, х2,.. °, хп,„. Ври этом для реализацйи 2 различных логических функций с помощью сигналов UÄ, 0 производится соответствующая настройка чультйплексора на логическую Функцию f <(х„, х„ и,) после того, как значение логической

Функции (х, х„ m) будет записано, в блок памятй.

На группу входов 5 устройства подаются.nl информационных сигналов х„ и,+„, х„, которые управляют работой мультиплексора 3 и подключают к выходу 8 устройства один иэ элементов памяти блока 2 памяти. В результате на выходе устройства формируется сигнал, значение которого определяется логическим выражением х ...x Е ix x п-я+1 ll-пм2 и д (n-п )

"n-in n-in+2- nx Е.,(х )ч.. v x x кХ

" п +2 " п 2п 1g 1 хп- п)чХп Х

<Х nl+2 - п 2nl q (,х„nl) которое представляет собой разложение произвольной логической функции и переменных f (x 2 ) по переменBblM х „rn1 х „.

Вычисление значения любого логического выражения на любом наборе входных переменных х, x 2,..., х„ в устройстве осуществляется за 2п тактов, на каждом из которых осуществляется настройка мультиплексора 1 на реализацию соответствующей логической функции д-а переменных

f (x„2„„,) и запись значения функции в соответствукщую ячейку блока 2 памяти.

Схема предлагаемого устройства при и = 10, m = 5 и использовании мультиплексора 1 (Фиг.2) и мультиплексора 3 (Фиг.3) имеет сложность

962918 по числу входов логических элементов, равную 600, что более чем в

10 раз проще схемы устройства-прототипа на 10 входов. В среднем данное устройство без учета сложности блока памяти в 2 ° раз проще устройства-прототипа для вычисления логических выражений.

Формула изобретения

Устройство для вычисления логических выражений n . п е рpеeм енHн ы х, содержащее два мультиплексора, выход первого мультиплексора является выходом устройства, Ifïðàâëÿùùèå входы первого мультиплексора подключены к л информационным входам. устройства, n --m информационные входы второго мультиплексора подключены к информационным входам устройства, управлякицие входы которого подключены к управляющим входам второго мультиплексора, о т л и ч а ю— щ е е с я тем, что, с целью упрощения, устройство содержит блок памяти, входы записи которого подключены к выходу второго мультиплексора, а входы управления — к дополнительным управляющим входам устрой,ства, выходы блока памяти подклочены к информационньм входам первого мультиплексора.

Источники информации, принятые во внимание при экспертизе

1. Якубайтис Э.A. Универсальные

l$ логические элементы. - "Автоматика и вычислительная техника", 9 5, 1973, с. 14.

2. Малев S.A. Структурная избыточность в логических устройствах. щ М., "Связь", 1978, с. 124, рис. 2.8 (прототип)..

962918

Составитель В. Кайданов

Техред С.Мигунова корректор А. Гриценко

Редактор А. Маковская

Филиал ЯГГ1. "Патент"1. г. Ужгород, ул. Нроектная, 4

Закаэ 7513/68 Тираж 731 Подписное

ВНИКНИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5