Усилитель считывания на дополняющих мдп-транзисторах

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Соцналнстнчесинх

Республни ()963087 (6l) Дополнительное к авт. свид-ву (22) Заявлено 30.03.81 (21) 3266642/18-24 с присоединением заявки М (51)М. Кл .

511 С 7/00

Впударствепый комитет

СССР пв делам иэобрвтеиий и открытий (23) П риорнтет—

Опубликовано 30.09.82. Бюллетень йа36 (53) УДК 681.327. .6(088.8) Дата опубликования описания 03.10.82. (72) Авторы изобретения

В. В. Баранов, Ю. М. Герасимов, H. Г. Григорь

А. Н. Кармазинский, П. Б. Поплевин и Э. П. С (7l ) Заявитель (54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ HA ДОПОЛНЯЮ1ЦИХ

МДП-ТРАНЗИСТОРАХ

Изобретение относится к вычислительной технике и может быть использовано при построении микромошных запоминаюших устройств на дополняюших МДП-транзисторахх.

Известны усилители считывания, содержашие триггер на МДП-транзисторах, в котором затворы нагрузочных транзисторов соединены с разрядными шинами(1)

Недостатки данных усилителей - низкая чувствительность и большая потребляемая мошность..

Наиболее близок к предлагаемому усилитель считывания на дополняюших

° МДП-транзисторах, содержаший первый и второй и-канальные транзисторы, соединенные по схеме с перекрестной связью, истоки которых соединены с шиной питания и истоками Р -канальных транзисто ров первого и второго инверторов, стокисоответственно со стоками первого и второго нагрузочных yt -канальных транзисторов, а также со входами соответственно первого и второго инверторов, выходы которых соединены соответственно с первым и вторым выходами усилителя считывания, причем затворы первого и второго нагрузочных VI --канальных транзис5 торов соединены соответственно с первой и второй разрядными шинами, истоки - co стоком ключевого -канального транзистора, затвор которого соединен с первой шиной управления, исток — с обшей шиной, истоки П --канальных транзисторов первого и второго инверторов соединены со стоком ключевого И-канального транзистора, к первой шине управления подключен зат вор симметрируюшего транзистора, исток которого связан с входом первого инвертора, а сток -. с входом второго инвер тора P2) .

Недостатками известного усилителя

20 считывания являются низкая чувствительность, обусловленная невозможностью изменения напряжением разрядных шин напряжения в точках, к которым подклю-.

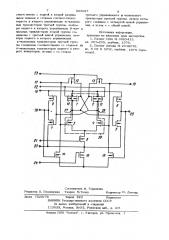

963087 чены стоки первого и второго р -каналь- И-канальных транзисторов первого и ных транзисторов, соединенных по схеме второго инверторов, истоки — со стбком с перекрестной связью, до момента вре- третьего управляющего и -канального мени, когда открывается стробирующий транзистора третьей группь:, затвор коl транзистор, а .также большая потребляе- S торого соединен с четвертой шиной упмая мощность, обусловленная медленным равления, а исток — с общей шиной. запиранием одного из нагрузочных И . На чертеже представлена схема усиканальных транзисторов. лителя считывания.

Бель изобретения — повышение чувст- Схема содержит ключевые первый 1 вительности и уменьшение потребляемой 10 и второй 2 И -канальные транзисторы, мощности усиителя считывания. первый 3 и второй 4 нагрузочные р-êàПоставленная цель достигается тем, нальные транзисторы, первый инвертор что усилитель считывания на дополняю- на транзисторах 5 и 6, второй инвертар них МДП-транзисторах, содержащий пер- на транзисторах 7 и 8, ключевой 9 -кавый и второй ключевые р -канальные трап 15 нальный транзистор 9, управляющие перзисторы, соединенные триггерной связью, вый 10 и второй 11 Р»канальные транистоки ключевых р -канальных транэисто-. эисторы первой группы, управляющие второв соединены с шиной питания и истока- рой 12 и первый 13 р -каанльные транми Р-канальных транзисторов первого и зисторы второй группы, управляющие втовторого инверторов, стоки ключевых р- 20 рой 14, первый 15 и третий 16 и -каканальных транзисторов соединены соот- нальные транзисторы третьей группы ветственно со стоками первого и второго первую 17 и вторую 18 разрядные шины, нагрузочных И -канальных транзисторов шину 19 питания общую шину 20 пер-. и эа тв орам и р канальных тра нэис торов вую 21, вторую 22, третью 23 и четверпервого и второго инверторов, стоки р- 25 тую 24 шины управления, первый 25 и канальных транзисторов которых являются второй 26 выходы усилителя считывания, соответственно первым и вторым выхода- узлы 27 и 28 триггера 29, образуемого . ми усилителя считывания, причем затворы транзисторами 1 — 4. первого и второго нагрузочных Q -каналь- В схеме усилителя считывания транных транзисторов соединены соответсч- щ зисторы 1 и .2 соединены по схеме с венно с первой и второй разрядными ши- перекрестной связью; причем стоки соотнами, истоки - co стоками третьего клю- ветственно подключены к стокам транзисчевого и-канального транзистора, затвор торов 3 и 4, а истоки - к шине 19, зат третьего ключевого И -чсанального тран- вор транзистора 1 связан со стоком транзистора соединен с первой шиной управ- зистора 4, а затвор транзистора 2 - со линия, а исток - с обшей шиной, содержит стоком транзистора 3, истоки транзистотри группы управляющих И -канальных ров 3, 4 объединены и подключены к стотранзисторов, при этом истоки И-канагп ку транзистора 9, исток которого связан ных транзисторов первого и второго ин-,. с шиной 20., a затвор - с шиной 21, затверторов соединены с обшей шиной, эа 0 аор транзистора 3 подключен к шине 17, воры первого и второго управляющих а затвор транзистора 4 - к шине 18, Р -канальных транзисторов первой группы затворы транзисторов 10 и 11 соединены соединены со второй шиной управлении, с шиной 22, истоки - с шиной .19, а стоистоки — c шиной питания, стоки - соот- ки — соответственно со стоками транзисветственно со стоками первого и второго торов 1 и 2; затворы транзисторов 12 и нагрузочных М -канальных транзисторов 13 подключены к шине 23, истоки - сои истоками первого и второго управляю- ответственно к шинам 17 и 18, а. стокиших р -канальных транзисторов второй соответственно к затворам транзисторов группы, стоки которых соединены соот- 1 и 2, затвор транзистора„1 подключен ветственно с первой и второй разрядными к затворам транзисторов 7 и 8, стоки

50 шинами и со стоками соответственно пер- которых соединены с выходом 26, исток вого и второго управляющих И -каналь транзистора 8 связан с шиной 19, а исных транзисторов третьей группы, затво- ток транзистора 7 - с шиной 20, затвор ры первого и второго управляющих Р -ка- транзистора 2 подключен к затворам нальных транзисторов второй группы со- транзисторов 5 и 6, стоки которых единены с третьей шиной управления, Я соединены с выходом 25;: исток транзисзатворы первого и второго управляющих тора 6 связан с шиной 19, а исток транП-канальных транзисторов третьей груп- зистора 5 - с шиной 20, исток транзиспы соединены соответственно со стоками тора 16 связан с шиной 20, затвор - с

5 963087 6 шиной 24, а сток - с истоками транзис- вие протекания сквозного тока через торов 14 и 15, стоки которых подклю- . триггер 29. чены соответственно к шинам 17 и 18, Режим записи отличается от режима а затворы связаны соответственно с вы- хранения тем, что напряжение на шине ходами 26 и 25. 24 соответствует уровню логического

Усилитель считывания работает следующим образом.

В режиме хранения. напряжение на шинах 17 - 19 и 24 соответствует уровню логической единицы, а на шинах 20 — 23-10 наковом разбросе параметров предлагаеуровню логического нуля. Транзисторы

1, 2, 6, 8, 9, 14 и 15 закрыты. Остальные транзисторы открыты. В узлах 27 и

28 поддерживается напряжение логической единицы, а на выходах 25 и 26 уси- 15 лителя считывания - напряжение логического нуля. Формула изобретении

В режиме считывания сначала подается сигнал логической единицы на шину 22.

Транзисторы 10 и 11 закрываются и 20 узлы 27 и 28 оказываются изолированными от шины питания. нуля, а на шине 23 - логической единиЦЫ.

Моделирование на ЭВМ схемы усилителя считывания показало, что при одимый усилитель считывания обладает на

20 «30% болье высокой чувствительностью и меньшей потребляемой мощностью по сравнению с базовым объектом.

При этом паразитная емкость одной иэ разрядных шин (предположим шины 17) 2з начинает заряжаться током считывания от выбранного элемента памяти, который в схеме ОЗУ подключен к разрядным шинам 17 и 18. Через открытые транзисторы 12 и 13 изменение напряжения раз- рядных шин передается в узлы 27и 28.

После того, как напряжения в узлах 27 и 28 и на разрядных шинах 17 и 18 станет достаточным, чтобы скомпенсиро» вать разбаланс усилителя считывания, подается напряжение логической единицы на шины 21 и 23. При этом транзисто-ры 12 и 13 закрываются, изолируя узлы

27 и 28 от разрядных шин 17 и 18.

Транзистор 9 открывается и в схеме развивается регенеративный процесс, после окончания которого триггер 29 оказывает ся в одном иэ устойчивых состояний, определяемом напряжением на разрядных

:шинах. В узле 28 формируется уровень

4э логического нуля. Инвертор на транзисторах 7 и 8 переключается, открывая транзистор 14. Через открытые транзис торы 14 и 16 ускоряется разряд емкости разрядной шины 17. После окончания переходного процесса в узлах 27 и 28

50 устанавливаются уровни напряжения, соответствующие логической единице и нулю, соответственно на разрядной шине 17 устанавливается уровень логического нуля, на выходах усилителя 25 и 26уровни, соответствующие логическому нулю и единице соответственно. Транзисторы 2 и 3 закрыты, обеспечивая отсутстУсилитель считывания на дополняющих

МДП-транзисторах, содержащий первый и второй ключевые р -канальные транзисторы, соединенные триггерной связью, истоки ключевых р -канальных транзисторов соединены с шиной питания и истоками P-канальных. транзисторов первого . и второго инверторов, стоки ключевых

Р --канальных транзисторов соединены соответственно со стоками первого и второго нагрузочных у -канальных транзисторов и затворами Р-канальных транзисторов первого и второго инверторов, стоки р --канальных транзисторов которых являются соответствейно первым и вторым выходами усилителя считывания, причем затворы первого и второго нагрузочных р-канальных транзисторов соединены соответственно с первой и второй разрядными шинами, истоки - co стоками третьего ключевого р -канального транзистора, затвор третьего ключевого р --канального транзистора соединен с первой шиной управления, а исток — с общей шиной, отличающийся тем, что, с целью повышения чувствительности и уменьшения потребляемоч мощности усилителя считывания, он содержит три группы управляющих р -канальных транзисторов, при этом истоки и-канальных транзисторов первого и второго инверторов соединены с обшей шиной, .затворы пер-вого и второго управляющих Р-канальных транзисторов первой группы соединены со второй шиной управления, истоки — с шиной питания, стоки — соответственно со стоками первого и второго нагрузочных

И -канальных транзисторов и соответст» венно с истоками первого и второго управляющих р -канальных транзисторов вто)зой группы, стоки которых соединены с о7 963087 8 ответственно с первой и второй разряд- третьего управляющего yI -канального ными шинами и стоками соответственно транзистора третьей группы, затвор кото« первого и второго управляющих И-каналь- рого соединен с четвертой шиной управленых транзисторов третьей группы, затво- ния, а исток - с общей шиной. ры первого и второго управляющих Р-канальных транзисторов второй группы со- Источники информации единены с третьей шиной управления, зат- принятые во внимание приэ экспертизе воры первого и второго управляющих 1. Патент США № 3983413, р-канальных транзисторов третьей груп- кл. 307-235; опублик. 1976. пы соединены соответственно со стоками to 2. Патент Англии N 2018076, р -канальных транзисторов первого и вто- KlI. Н 03 К 5/02, опублик. 1979 (про рого инверторов, истоки - со стоком тотип) .

Составитель l5. Гордонова

Редактор Л. Пчелинская . Техред М.Тенер Корректор <- немчик

Заказ 752 5/76 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР

bio делам изобретений и открытий

1 13 03 5, Москва, Ж 3 5, Раушская наб., д. 4! 5

Филиал ППП "Патент", г. Ужгород, ул. Проектная,