Устройство для умножения двух @ -разрядных чисел

Иллюстрации

Показать всеРеферат

А. М. Романкевич, В. А. Остафин, М. Г. Лукаш и. Ю. А. Яначков (72) Авторы изобретения

Киевский ордена Ленина политехнический инсти им. 50-летия Великой Октябрьской социалистич (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДВУХ

" -РАЗРЯДНЫХ ЧИСЕЛ

Изобретение относится к вычислитель ной технике и может быть использованр в арифметических устройствах UBM и устройствах обработки цифровой информации.

Известно устройство для умножения двух Vl-разрядных чисел, содержашее мат- рицу из элементов И, первый (2И -1)разрядный блок элементов ИЛИ, И -разрядный регистр множимого, (2.И- 1)-разрядный сумматор, И-разрядный! регистр

° 1О множителя, первый и второй И-разрядные блоки элементов И, второй И-разрядный блок алементов ИЛИ и И-разрядный блок элементов задержки 1) .

Недостатком укаэанного устройства 5 является низкое быстродействие.

Наиболее близким к изобретению по технической сущности является устройс1 во для умножения двух и -разрядных чисел, содержашее VI-разрядный регистр множимого, ln - разрядный регистр множителя, И элементов И, фч -разрядный сумматор, причем информационйые входы регист2 ра множимого и регистра множителя являются соответственно входами первого и второго операндов устройства, вход синхронизации регистра множителя является входом синкронизации устройства, разрядные выходы регистра множимого соединены соответственно с первыми входами элементов И, выходы которых соединены соответственно с входами сумматора (21.

Недостатком етого устройства является низкое быстродействие при большой разрядности сомножителей, так как задержка, вносимая сумматором в одном такте умножения, пропорциональна разрядности сомножителей.

Белью изобретения является повышение быстродейс твия.

Поставленная цель достигается тем; что в устройство введены два И -разрядных регистра, причем входы синхронизации первого и второго регистров соединены с входом синхронизации регистра множителя, входы сброса первого и второго 964632 регистров соединены с входом сброса уст» ройств, выход сумматора соединен .с информационным входом первого регистра, выход младшего разряда которого соединен с входом регистра множителя, выход S младшего разряда которого соединен с информационным входом второго регистра, разрядные выходы которого соединены соответственно с вторыми входами элементов И. 10

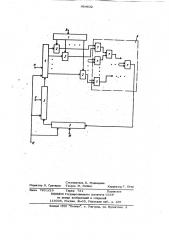

На чертеже приведена структурная схема устройства для умножения двух И -разрядных чисел.

Устройство содержит g-разрядный регистр 1 множимого и g -разрядный ре- 15 . гистр 2 множителя, .элементы И 3, регистры 4 и 5, И-разрядный сумматор 6, состоящий иэ пирамидально соединенных сумматоров 7 последовательного действия, входы 8 и 9 операндов устройства, входы щ

10 и 11 сбросе устройства, вход 12 синхронизации ус тройства.

В устройстве информационные входы, "регистра 1 множимого и регистра 2 множителя являются соответственно входами

8 и 9 операндов устройства, вход 12 синхронизации устройства, разрядные выходы регистра 1 множимого соединены соответственно с первыми входами элементов И3, выходы которых соединены соответствен- 36 но с входами сумматора 6, входы сйнхро- низации регистров 4 и 5 соединены с вхо дами 10 и 11 сброса устройства; выход сумматора 6 соединен с информационным входом регистра 5, выход младшего раз ряда которого соединен с информационным

35 .входом регистра 2 множителя, выход младшего разряда которого соединен с информационным входом регистра 4, разрядные выходы которого соединены соответствен.40 но с вторыми входами элементов И 3, входы. синхронизации регистров 4 и.5 соединены с входом синхронизации регистр ра 2 множителя.

Устройство работает следующим об43 разом.

Регистры 4 и 5 перед началом работы устройства устанавливаются в нулевое состояние. В регистр 1 множимого и регистр 2 множителя записываются соотг ветственно множимое (Ц,т,g ...,Е „,..., 50 аИ) и н ь(Ü„Ь ° ° ° Ъ3 ° ° ° ЬИ) °

В первом такте производится сдвиг на один разряд содержимого регистров 2, 4 и 5, и на вход регистра 4 поступает младший разряд множителя ф„.С выхода

И -го разряда регистра 4 на первый вход

И -го элемента И 3 поступает сигнал

0" или "1, соответствующий значению

4 . младшего множителя Ь . На второй вход

И -го элемента И поступает сигнал С( с выхода .9-го разряда регистра 1 множимого. С выхода<элемента И 3 сигнал, соответствующий коньюнкции 5> Ь, поступает на вход сумматора 6. С выхода сумматора 6 сигнал, соответствующий младшему разряду произведения, поступает на вход регистра 5.

Во втором такте производится сдвиг на один разряд содержимого регистров

2, 4 и 5, и на вход регистра 4 поступает второй младший разряд множителя

Ьу q . Соответственно на первый вход

-го элемента И 3 поступает второй младший разряд множителя Ь,, а на первый вход (:И - 1)-го элемента И 3 первый младший разряд множителя Ьп-На вторые входы (И - 1)-го и И-го элементов И 3 поступают соответственно разряды множимого (3>+ иЦ „. Сигналы, соответствующие коньюнкциям С „1д, и

С „ „Ь„, с выходов элементов И 3 поступают на входы сумматора 6. В сумматоре 6 производится суммирование по модулю два 6@5 <+O Q.Запоминание переноса в следующий разряд произведения происходит в одном из сумматоров 7 последовательного действия сумматора 6.

С выхода сумматора 6 на вход регистра

5 поступает (2 и - 1)-й разряд произведения.

В следующих тактах производится поразрядный сдвиг содержимого регистров

2, 4 и 5. С выходов элементов И 3 сигналы, соответствующие конъюнкциям 0t< b ., поступают на входы соответствующих разрядов сумматора 6. В сумматоре 6 производится суммирование по модулю два

6I< t)< c переносом из предыдущего разряда произведения. Запоминание переносов в . следующие разряды произведения происходит в сумматорах 7 последовательного действия сумматора 6. С выхода сумматора 6 на вход регистра 5 поступает соответствующий разряд произведения.

В (2М - 1)-м такте старший разряд множителя Ь с выхода регистра 4 поступает на первый вход первого элемента

И 3, на второй вход которого поступает старший разряд множимого 61. С выхода элемента И 3 сигнал поступает на вход сумматора 6. B сумматоре 6 производится сложение 0< Q< с перекосом из предыдущего разряда произведения. С выхода сумматора 6 эта сумма поступает на вход регистра 5. Перенос из (2И-1)-го разряда произведения поступает на выход

964632

5 сумматора 6 во 2-м такте, как самый старший разряд произведения.

Таким образом, после 2й-го такта в регистре 2 хранятся младшие разряды, а в регистре 5 - старшие разряды произведения.

Конец операции умножения фиксируется по нулевому состоянию регистра 4, что позволяет сократить число тактов умно жения при числе разрядов множителя, меньшем И

Предлагаемое устройство для умножения двух И -разрядных чисел является более быстродействуюшим по сравнению с известным устройством, время выполнения IS умножения Ф. в котором определяется. следующим обрааом:

А=1+1+И tñä . где - время сложения двух In-разрядных чисел; 26 Ь с в- время сдвига tl -разрядного числа.

Задержка, вносимая сумматором в одном такте умножения, пропорциональна разрядности сомножитеЛей, . т. е.

1„=ИЧ;„, . ц

+ где С - задержка, вносимая одним разрядом сумматора в извеотном устройстве.

Задержка, вносимая сумматором в одном такте; умножения, в устройстве За

+ определяется числом )Eaf и уровней сумматоров последовательного действия а «1ВЬ.РГ„ где С - задержка, вносимая одним раз.рядом сумматора в предлагаемому ус трой тве.

Время выполнения умножения в устрой стве Ьд. определяется следующим образом:

t «2и1+ =йище(щ и с .

Обычно величины +<, 1: и+ впр мерно равны. Тогда, так как функция >%+Mt ù И+ а ОЩС М(о С-: является возрастающей с увеличением и уже при И = 4 становится больше едини-; пы, то, следовательно, при большей разрядности сомножителей предлагаемое уст ройство является более быстродействую- © шим, чем известное устройство. При .И = 15.

К= 2.

Кроме того, в реальных синхронных устройствах умножения время суммирования и сдвига представляет собой один одинаковый. такт работы устройства управления, синхронизируюшего работу узлов операционной части.

В этом случае

Ы ф+=1, а К= сде 3Ео9 и и уже при И= 2 К> 1.

Формула изобретения

Устройство для умножения двух In-раз.рядных чисел, содержащее д-разрядный регистр множимого, И -разрядный регистр, множителя, In элементов И, И -разрядный сумматор, причем информационные входы регистра множимого и регистра множителя являются соответственно входами первого и второго. операндов устройства, вход синхронизации регистра множителя являет ся входом синхронизации устройства, разрядные выходы регистра множимого соединены соответственно с первыми .входами элементов И, выходы которых соединены соответственно с входами сумматора, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены два g-разрядных регистра, причем входы синхронизации первого и второго регист-. ров соединены с входом синхронизации регистра множителя, входы сброса первого и второго регистров соединены с входом сброса устройства, выход сумматора соединен с информационным входом первого регистра, выход младшего разряде которого соединен с входом регистра множителя, выход младшего разряда которого соединен с информационным входом второго регистра, разрядные выходы которого соеди-. нены соответственно с вторыми входами элементов И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 623204, кл. 606F 7/S2, 1977.

2. Папернов А. А. Логические основы пирровой вычислительной техники. М., "Советское радио, 1972, с. 195, р. 2 (прототип) .

964632

Составитель Д. Медведева

Редактор Л. Гратнлло Техред И. Рейвес Корректор Г. Orsp

Заказ 763 1/2 9 Тираж 73 1, Подписное

ВНИИПИ Государственного комитета СССР по деларе изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/,5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4