Дешифрирующее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски к

Сощиалисткнвскик

Рвслублнк (,98 2194 (61) Дополнительное к авт. санд-ву (22) Заявлено 20. 05. 81 {21) 3294073/18-21 с присоединением эаявки М (23 ) Приоритет (51)N. Кл.

Н 03 K 13/24

Ввударстеенный каннтет

СССР ао делан нзобретеннй и открытка

Опубликовано 15, 12. 82. Бюллетень М 46

Дата опубликования описания 15. 12. 82 (53) УДК 621.272 (088. 8) «у

1 (72) Авторы изобретения

Е. Н. Розенберг, В. В

И.А. Здоровцов, Д.Н

В.И. Любимов, В.А

Конструкторское баро и связи (7!) Заявитель (54 ) ДЕШИФРИРУЮЩЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и телемеханике и может быть использовано в устройствах железнодорожного транспорта.

Известен дешифратор, состоящий из двухканального входного каскада, содержащего в каждом из каналов входной транзистор, эмиттер которого подключен к входу дешифратора, коллектор соединен с базой переключающего тран- о зистора, а база входного транзистора соединена через резистор с шиной питания и выходного каскада, выполненного на транзисторах и диодах, коллек" тор переключающего транзистора входного каскада подключен к общей шине, эмиттеры через резистор — к шине питания, к катодам соответствующих диодов выходного каскада, а также к аноду диода, катод которого соединен с 2о базой инвертирующего транзистора, причем коллектор инвертирующего транзистора подключен к общей шине, эмиттер через резистор - к шине питания и каСапожников, М. М. Ле6едев, Хромушкин, Е. Г. Осташков, Коляда и l0.П, Супря ов, 1

Главного управления сигнализации

МПС тодам соответствующих диодов выходного каскада, при этом объединенные попарно аноды диодов выходного каскада подключены через резистор к шине питания и к анодам диодов, катоды которых подключены к базам соответствующих транзисторов выходного каскада, коллекторы последних соединены с общей шиной, а эмиттеры — с соответствующими выходами дешифратора 31).

Недостатком данного дешифратора является возможность появления болео одного выходного сигнала при отказе его элементов.

Наиболее близким к предлагаемому является дешифрирующее устройство, содержащее дешифратор, подключенный выходом к блоку выбора приоритетного сигнала, выполненному на однопереходных транзисторах и имеющему дополнительные входы (2 j.

Однако известное устройство недостаточно надежно.

Формула изобретения йешифрирующее устройство, содержащее дешифратор и блок приоритетного сигнала, имеющий дополнительные входы, первый вход которого соединен с выходом дешифратора, о т л и ч а ющ е е с я тем, что, с целью повышения надежности, в него введены инвертор, контрольный блок и селектор времени, вход которого соединен с выходом контрольного блока, подключенного входом к выходу дешифратора, выход селектора времени соединен с вторым входом блока выбора приоритетного сигнала и входом инвертора, выход которого соединен с третьим входом блока приоритетного сигнала.

Источники информации, принятые во внимание при экспертизе

Авторское свидетельство СССР

N 547968, кл. H 03 К 13/24, 08. 12. 75.

2. Авторское свидетельство СССР

N 762177, кл. H 03 K i3/24, 31.05.79 (прототип ), 3 9821

Цель изобретения - повышение надежности.

Для достижения указанной цели в дешифрирующее устройство, содержащее дешифратор и блок приоритетного сигнала,g имеющего дополнительные входы, первый вход которого соединен с выходом дешифратора, введены инвертор, контрольный блок и селектор времени, вход которого соединен с выходом контрольно- !О го блока, подключенного входом к выходу дешифратора, выход селектора времени соединен с вторым входом блока выбора приоритетного сигнала и входом инвертора, выход которого соединен с 15 третьим входом блока приоритетного сигнала.

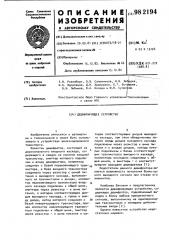

На чертеже представлена структурная схема устройства.

Устройство содержит дешифратор 1, 2Î подключенный выходом к блоку выбора приоритетного сигнала 2, с входами

2.2 и 2.3, выход которого является выходом устройства. Выход селектора времени 3 подключен непосредственно 25 к второму 2.2 .и через инвертор 4 к третьему 2.3 управляющим входам блока выбора приоритетного сигнала 2.

Выход контрольного блока 5 подключен к входу селектора времени 3, а вход - за к дешифратору 1.

Устройство работает следующим образом.

В нормальном режиме работы, т. е. при исправности элементов дешифратора 1 и контрольного блока 5, на выходе блока выбора приоритетного сигнала 2 присутствует сигнал управления объектом. При отказе дешифратора 1, фиксируемым контрольным блоком 5, под- о ключается селектор времени 3. Производится оценка длительности сигнала о неисправности дешифратора 1 на выходе контрольного блока 5. Если длительность о неисправности сигнала не пре- <5 вышает некоторого значения (определяемого по условиям области применения

94

4 ,дешифрирующего устройства ), то включается второй управляющий вход 2.2 блока выбора приоритетного сигнала 2.

При этом из двух и более сигналов на выходе дешифратора 1 выбирается один (например, старшего разряда ). Если длительность сигнала о неисправности превышает допустимую (постоянная неисправность ), то через инвертор 4 включается третий управляющий вход

2.3, а второй 2.2 выключается. Производится смена приоритета сигнала (выбирается младший разряд).

Таким образом, исключается появление на выходе предлагаемого дешифрирующего устройства многозначного выходного сигнала, что повышает надежность устройства, в котором предлагаемое дешифрирующее устройство используется.,982194

Составитель Б. Мельников

Редактор К. Волощук Техред Ж.Кастелевич Корректор И 1аРоши

Тираж. 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 9733/78

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4