Элемент памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. сеид-ву(22) Заявлено 020781 (21) 3313523/18-24 (S1} М. КП.

G 11 С 11/40 с присоединением заявки hK2— (23) Приоритет—

Государственный комитет

СССР но деяам изобретений н открытий (33} YQ(681, 327, 6 (088.8) Опубликовано 23.01.83, Бюллетень М 3

Дата опубликования описания 2501.83

В.В. Баринов, В.И. Кнмарский, Д.Е. Ковалдин, Ю.И. Куэовлев и И.В. Черняк (72) Авторы изобретения

Ф с

Г (Московский институт электронной техйицс

1 - (71) Заявитель,(54) ЭЛЕМЕНТ ПАЖИТИ

Изобретение относится к вычислительной технике и может быть использовано в полупроводниковых запоминающих устройствах. 5

Известен биполярный инжекционный элемент памяти, в котором для считывания информации используется фиктивный транзистор и фиктивная шина выборки. Структура элемента памяти еп содержит подложку р-типа проводимости, эпитаксиальный слой п-типа проводимости с сильнолегированной скрытой областью, разделенный на два сегмента изолирующей областью, причем каждый сегмент содержит по два. участка р-типа проводимости, один из котс рых служит инжектором, а другой - базой, в базах обоих сегментов созданы коллекторные области И -типа проводимости, скрытый слоЯ является об2 щим для двух сегментов и соединен с нижней адресной шиной, база одного сегмента соединена с коллектором другого и наоборот, один из инжекторов соединен с верхней адресной шиной, а другой - с разрядной шиной (1).

К недостаткам элемента памяти следует отнести малый. полезный сигнал считывания информации.и использование четырех шин выборки. 30

Наиболее близким по техническо1Г сущности к изобретению является элемент памяти, содержащий два и -p-й транзистора, включенных в триггерную структуру, и два р -и- р транэистбра, подключенные эмитторами к соответствующим разрядным шинам и базы которых соединены с эмиттерами n -р-и транзисторов и адресной шиной f2).

Недбстаток - малый полезный сигнал (разность потенциалов разрядных шин) 10-20 мВ в режиме считывания информации, что обуславливает низкую помехозащищенность элемента памяти.

Целью изобретения является повышение надежности элемента памяти за счет повьааения помехозащищенности элемента памяти.

Поставленная цель достигается тем, что элемент памяти, содержащий четы» ре транзистора, базы первого и второго Я -и- р транзисторов и эмиттеры третьего и четвертого у(--р-и транзисторов.соединены с адресной шиной, коллекторы первого и третьего транзисторов соединены и подключены к базе четвертого и -р-и транзистора, а коллекторы второго и четвертого транзисторов подключены к базе тре991508.тьего и --р-и транзистора, эмиттеры первого и второго И -p-И транзисторов соединены с первой и второй разрядными шинами соответственно, дополнительно содержит два р --и- р транзистора, эмиттери которых подключены 5 к соответствующим разрядным нинам, а базы и коллекторы - к коллектору и базе третьего и четвертого И -p -u транзисторов соответственно.

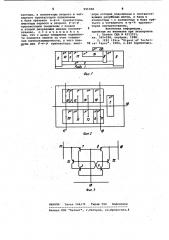

На фнг.1 представлена интеграль- 10 ная структура, поперечное сечение,, на фиг.2 - эскиз топологии, на фиг.3 - -принципиальная электрическая схема элемента памяти.

Структура биполярного инжекцион- 15 ного элемента памяти содержит подложку

1 р -òèïà проводимости, эпитаксиальный слой и-типа проводимосТи с сильнолегированной скрытой областью 2, являющейся эмиттерами Vt-p-и транзисто-2() ров 3 и 4, разделенный на два сегмента 5 и б, служащие базами инжекционных р -п -р. транзисторов 7 и 8, изолирующей областью 9, .причем каждый сегмент содержит по два участка р -типа 25 проводимости, один иэ которых служит инжектором 10 и 11, а другой - базой

12 и 13, в базах обоих сегментов созданы коллекторные области П +-типа провОдимОсти 14 и 15а Скрытый слОЙ Являс" у) ется общим для двух сегментов и соединен е адресной шиной 18. База одного, сегмента соединена с коллекторной областью другого и наоборот. Инжекторы соединены с разрядными шинами 17 и 18. 5

На коллекторных областях каждого сегмента сформированы высоколегированные поликремниевые области р -типа проводимости 19 и 20,.причем поликремниевая область одного сегмента соединена с инжектором противоположного и наоборот. Области 19, 14, 12 и 20, 15, 13 образуют "паразитные" р -М -p тран- эисторы .21 и 22 соответственно.

Элемент памяти работает следующюл образом. 45

В режиме считывания информации равные токи считывания 10 вытекают иэ разрядных шин 17 и 18 в элемент памяти. Предположим, что элемент 56 памяти находится в состоянии, когда транзистор 8 насыщен и коллекторным током насыщает транзистор 3. Тогда транзистор 4 работает в нормальном активном режиме, но ток через него практически отсутствует (1 -О), так как напряжение íà р-п-рпереходе эмиттер-база U9g этого транзистора равно напряжению лежду коллектором и эмиттером насыщенного транзистора

3 U 9,;, что меньше граиичного на- 4Е пряжения отпирания (-и-рперехода

Uy . Транзистор 7 практически работает в нормальном актиэном режиме (в режиме на границе насыщения напряженке на р-И-рпереходе база-коллектор З

0 этого транзистора равно 0 э с, U ). Транзистор 21 работает в режиме насыщения, а транзистор 22 работает в нормальном активном режиме, но ток через него отсутствует (ЪЭ=О) так как напряжение U9g этого транзистора равно напряжению U +>< насыщенного транзистора 8. Таким образом, практически весь ток считывания 1 О иэ разрядной шины 18 протекает через ., насыщенный транзистор 8, а ток,считывания из разрядной шины 17 распределяется между транзистором 7, работающим в нормальном активном режиме, и насыщенным транзистором 21. Полезный сигнал считывания информации (разность потенциалов разрядных шин ЬО ) возникает за счет разности токов эмиттерных диодов (модель типа Эберса-Молла) инжекционных р --п- р транзисторов

7 и 8 (эффект Эрли) и равен *

Рш т .(. (О где Я- - температурный потенциал; дИ вЂ” нормальный коэффициент ycul4 ления по току и-р-и транзисторов в схеме включения с общей базой; ,,(Р „(Р - нормальный и инверсный коэфй фициенты усиления по току -И-р транзисторов в схеме включения с общей базой, ток считывания, вытекающий из разрядной шины в элемент памяти, ! — часть тока считывания Т<, протекающая через транзистор

7, работающий в нормальном активном режиме.

Из приведенного выражения и анализа работы элемента памяти следует, что полезный сигнал считывания тем больше, чем меньший ток 1 протекает через транзистор.7, работающий в нормальном активном режиме. Соответственно, если весь ток считывания 1 протекает через транзистор 7 (трайзисторы 21 и 22 отсутствуют, как в известном}, то полезный сигнал считывания минимален. Введение двух транзисторов в элемент памяти позволяет увеличить полезный сигнал считывания и помехозащищенность в 510 раэ.

Формула изобретения

Элемент памяти, содержащий четы« ре транзистора, базы первого и второго Р -и- р транзисторов и эииттеры третьего и четвертого И -p-u транзисторов. соединены с адресной шиной, коллекторы первого и третьего транзисторов соединены и подключены к базе четвертого Q -р- И тран991508

ВНИИПИ Заказ 146/71 Тираж 592 Подписное

Филиал НПП "Патент", r.ужгород, ул.Проектная,4 зистора, а коллекторы второго и четвертого транзисторов подключены к базе третьего и-р"и транзистора, .эмиттеры первого и второго Р -п-р транзисторов соединены с первой и второй разрядники шинами соответ:ственно, о т л и ч .а ю шийся. тем, что с целыэ повышения надежности элемента памяти за счет повыше-. .ния помехоэащищенности, в него введены два Pw- р транзистора, эмит1теры которых подключены к соответст- вующим разрядным шинам, а базы и коллекторы -- к коллектору и базе третьего и четвертого и -р-И транзисторов соответственно.

Источники информации, принятые во внимание при экспертизе

1. Патент СШЪ Ф 4112511 кл. 365 188, опублик. 1980.

2. !ЕЕЕ ISSce "OIgest ef TechnI10 са1 Pepes". 1980, с.222 (прототип).