Одноразрядный четверичный сумматор

Иллюстрации

Показать всеРеферат

ОДНОРАЗРЯДННЙ ЧЕТВЕРИЧНЫЙ СУММАТОР, содержаний три элемента НЕ и один элемент ИЛИ, выход которого соединен с выходом переноса . одноразрядного четверичного сумматора , отличающийся тем, что, с делью упрощения конструкции, одноразрядный четверичный сумматор содержит одиннадцать элементов РАВНОЗНАЧНОСТЬ и четыре элемента И, причем первый вход первого элемента РАВНОЗНАЧНОСТЬ соединен с первьоли входами второго, третьего, четвертого и пятого элементов РАВНОЗНАЧНОСТЬ, с первым входе первогоэлемента И и с входом переноса одноразрядного четверичного сумматора, второй вход педвого элемента РАВНОЗНАЧНОСТЬ соединен с вторым входом третьего эле . мента РАВНОЗНАЧНОСТЬ и с 8ыходс 1 первого элемента НЕ, второй вход второго элемента РАВНОЗНАЧНОСТЬ соединён с BTOpfciM входсм четвертого и первым входом шестого элементов РАВНОЗНАЧНОСТЬ , с вторым входом первого элемента И,с входом первого элемента НЕ и входом младшего разряда первого операнда одноразрядного четверичного сумматора, третий вход четвертого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом седьмого элемента РАВНОЗНАЧНОСТЬ И ВЫХОДОМ второго элемента НЕ, второй вход пятого элемента РАВНОЗНАЧНОСТЬ подключён к выходу шестого элемента РАВНОЭНАЧ-. НОСТЬ, второй вход которого .соединен с первыми входами восы«эго элемента РАВНОЗНАЧНОСТЬ И второго элемента И,: с входом второго элемента НЕ и входом младаыего разряда второго-операнда одноразрядного четверичного сумматора, второй вход седьмого элемента РАВНОЗНАЧНОСТЬ соединен С вторым входом восьмого и первым входсм девятого элементов РТШНОЗНАЧНОСТЬ, с вторым входом второго и первым входа 1 TpeTbeFo элемента И и с входам старшего разряда второго операнда одноразрядного четверичного сумматора , второй вход девятого эл лента .| РАВНОЗНАЧНОСТЬ подключен К выходзу третьего элемента НЕ и к первому ,; десятого элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединён с шдходом одиннадцатого элемента РАВНОЗНАЧНОСТЬ , а выход соединен с выход | стардегр разряда суммы .однораз-. ,рядного четверичного сумматора, выход первого элемента РАВНОЗНАЧНОСТЬ подключен к третьему входу второго элемента И, выход второго элемента РАВНОЗНАЧНОСТЬ соединен с вторым входом третьего элемента И, выход третьего элемента РАВНОЗНАЧНОСТЬ соединен с первьг« входов четвертого элемента И, а выход четвертого - с первым входог.1 одиннадцатого злеменвыхрд niHToro элета РАВНОЗНАЧНОСТЬ, в мента РАВНОЗНАЧНОСТЬ ходу младшего разряда суммы одноразрядного четверичного сумматораj а выход седьмого - соединен с вторым входом четвертого эли 1ёнта И, . выход восьмого - с вторым входом одиннадцатого элемента РАВНОЗНАЧНОСТЬ , выход девятого элемента РАВНОЗНАЧНОСТЬ подключен к третьему входу первого элемента И, третий вход третьего элемента И соединен с третьим входом четвертого элемента И, с входом третьего элемента НЕ и с

СОЮЗ СОВЕТСКИХ СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3(5В 6 06F 7 50

ГОСУцАРСТВЕККЫЙ КОМИТЕТ СССР

Г

ГО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ I с

ОПИСАНИЕ ИЗОБРЕТЕНИЙ

Н АВТОРСНОМЪ СВИДЕТЕЛЬСТВУ (21) 3349983/18-24 (22) 21.10.81 (46) .15.06.83. Вюл. Р 22 (72) С.N.Tåðåøêî, A.È.Àñïèäoâ, В.А.Мищенко и Д.Е.Путеев (53) 681.325.5(088.8) (5á) 1. Гольцев Л.К. Структурная теория цифровых машин. М, "Энергия", 1971, с. 273.

2. Лысиков Б.Г. Арифметические и логические основы цифровых автоматов. NHHclc "Вышейшая школа", 1980, с. 169 (прототип}. (54) (57) ОДНОРАЗРЯДНЫЙ ЧЕТВЕРИЧНЫИ

СУММАТОР, содержащий три элемента

НЕ и один элемент ИЛИ, выход которого соединен с выходом переноса . одноразрядного четверичного сумматора, отличающийся тем,-что, с целью упрощения конструкции, одноразрядный четвернчнып сумматор содержит одиннадцать элементов РАВНОЗНАЧНОСТЬ и четыре элемента И, при. чем первый вход первого элемента

РАВНОЗНАЧНОСТЬ . соединен с первыми входами второго, третьего, четвертого и пятого элементов РАВНОЗНАЧНОСТЬ, с первым входом первого элемента И и с входом переноса одноразрядного четверичного сумматора, второй вход первого элемента РАВНОЗНАЧНОСТЬ соединен с вторым входом третьего эле, мента РАВНОЗНАЧНОСТЬ и с выходом пЕрвого элемента НЕ, второй вход вторОго элемента РАВНОЗНАЧНОСТЬ соединен с вторым входом четвертого и первым входом шестого элементов РАВНОЗНАЧНОСТЬ, с вторым входом первого элемента И,c входом первого элемента НЕ и входом младшего разряда первого операнда одноразрядного четверичного сумматора, третий вход четвертого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом седьмого элемента РАВНОЗНАЧНОСТЬ и выходом вто=- рого элемента НЕ, второй вход пятого,SU„„023322 A элемента РАВНОЗНАЧНОСТЬ подключЕн К

-выходу шестого элемента РАВНОЗНАЧ-.

НОСТЬ, второй вход которого .соединен с первыми входами восьмого элемента

РАВНОЗНАЧНОСТЬ и второго элемента И, с входом второго элемента НЕ и входом младшего разряда второго.операнда одноразрядного четверичного сумматора, второй вход седьмого элемента РАВЙОЗНАЧНОСТЬ соединен с втОрьм входом восьмого и первым входом девятого элементов РАВНОЗНАЧНОСТЬ, с вторым входом второго и первым входом третьего элемента И и с входом старшего разряда второго операнда одноразрядного четверичного сумматора, второй вход девятого элемента . Е

РАВНОЗНАЧНОСТЬ подключен к унходу тре тьего элемента НЕ и к первому входу, десятого элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с -выходом одиннадцатого элемента РАВНОЗНАЧНОСТЬ, а выход соедийен с выхо- д дом старшего разряда-суммы сщиораз-. рядного четверичного сумматора, выход первого элемента РАВНОЗНАЧНОСТЬ подключен к третьему входу второго элемента И, выход второго элемента

РАВНОЗНАЧНОСТЬ соединен с вторым входом третьего элемента И, выход третьЕго элемента РАВНОЭНАЧНОСТЬ соединен с первым входом четвертого элемента И, а выход четвертого — с первым входом одиннадцатого элемента РАВНОЗНАЧНОСТЬ, выход пятого эле-. мента РАВНОЗНАЧНОСТЬ подключен к выходу младшего разряда суммы одноразрядного четверичного сумматора; а выход седьмого — соединен с вторым входом .четвертого элемента И, . выход восьмого - c вторым входом одиннадцатого элемента РАВНОЗНАЧНОСТЬ, выход девятого элемента РАВ-.

НОЭНАЧНОСТЬ подключен к третьему входу первого элемента И, третий вход третьего .элемента И соединен с тре-. тьим входом четвертого элемента И, с входом третьего элемента НЕ и с

1023322 третьего и четвертого элементов И соединены с соответствующими входами элемента ИЛИ. входом старшего разряда первого операнда одноразрядйого четверичного сумматора, выходы первого, второго, Изобретение относится к вычисли-,шестого элемента РАВНОЗНАЧНОСТЬ,втотельной технике и может быть йсЪоль", рой вход которого соединен с первызовано в цифровых устройствах обра- ми входами восьмого элемента PABHOботки информации. ЗНАЧНОСТЬ и второго. элемента И, с

Известно построение четверичного 5 входом второго элемента НЕ и входом сумматора на основе описывающих его младшего разряда второго операнда логических функций с использованием одноразрядного четверичного суммаэлементов И, ИЛИ, НЕ(1 ). тора, второй вход седьмого элеменНедостатком его является слож- та РАВНОЗНАЧНОСТЬ соединен с вторым ность конструкции, выражающаяся в 10 входом восьмого и первым входом девябольшом числе используемых элемен- того элементов РАВНОЗНАЧНОСТЬ, с втотов. рым входом второго и первым входом треИзвестен также одноразрядный чет- тьего элемента H и с входом веричный сумматор, содержащий пять старшего разряда второго операнэлементов НЕ, тринадцать элементов )5 да одноразрядного четверичного суммаИ и пять элементов. ИЛИ, предназначен" тора, второй вход девятого элемента ный для суммирования двух четверич-. РАВНОЗНАЧНОСТЬ подключен к выходу ных операндовf.2). третьего элемента НЕ и к первому вхоНедостатком его является относи- ду десятого элемента РАВНОЗНАЧНОСТЬ, тельная сложность конструкции, при- второй вход которого соединен с выховодящая к снижению надежности сум- дом одиннадцатого элемента РАВНОЗНАЧма тора. НОСТЬ, а выход соединен с выходом цель изобретения - упрощение кон- старшего разряда суммы одноразряднострукции одноразрядного четверично- .го четверичного сумматора, выход перго сумматора., вого элемента РАВНОЗНАЧНОСТЬ подклюПоставленная цель достигается чен к третьему входу второго элементем, что одноразрядный четверичный та И, выход второго элемента РАВНОсумматор, содержащий три элемента НЕ ЗНАЧЙОСТЬ соединен с вторым входом и один элемент ИЛИ, выход которого третьего элемента И, выход третьесоединен с выходом переноса однораз- го элемента РАВНОЗНАЧНОСТЬ соединен рядного четверичного сумматора, со- 30 с первым входом четвертого элемендержит также одиннадцать элементов та И, выход четвертого — с первым

РАВНОЗНАЧНОСТЬ и четыре элемента И> входом одиннадцатого элемента РАВНОпричем первйй вход перВого элемента ЗНАЧНОСТЬ, выход пятого элемента

РАВНОЗНАЧНОСТЬ соединен с пеРвыми РАВНОЗНАЧЙОСТЬ подключен к выходу входами второго, третьего, четверто 35 младшего разряда суммы одноразрядного и пятого элементов РАВНОЗНАЧНОСТЬ. го четверичного сумматора, а выход с первым входом первого элемента И седьмого — соединен со вторым вхои с входом переноса одноразрядного дом четвертого элемента И, выход четверичного сумматора, второй вход восьмого со вторым входом одиннадцапервого элемента РАВНОЗНАЧНОСТЬ СоЕ 40 того элемента РАВНОЗНАЧНОСТЬ, выход динен с вторым входом третьего эле- ревятого элемента РАВИОзнАчйОсть мента РАВНОЗНАЧНОСТЬ и с выходом пер" подключен к третьему входу первого вого элемента НЕ, второй вход второго элемента И, третий вход третьего элемента РАВНОЗНАЧНОСТЬ соединен c . Элемента И соединен с третьим входом вторым входом четвертого и первым . четвертого элемента И, с входом тревходом шестого элементов РАВНОЗНАЧ- И тьего. элемента НЕ и с Входом старшего

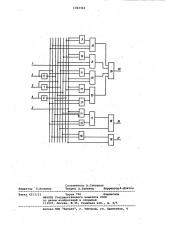

НОСТЬ, с вторым входом первого эле- разряда первого операнда одноразрядмента И, с входом первого элемента HE ного четверичного сумматора, выходы и входом младшего разряда первого опе- первого, .второго, третьего и четверранда одноразрядного четверичного того элементов И соединены с соотсумматора, третий вход четвертого 60 ветствующими входами элемента ИЛИ. элемента РАВНОЗНАЧНОСТЬ соединен с На чертеже представлена функциопервым входом седьмого элемента PAB- нальная схема одноразрядного четвеНОЗНАЧНОСТЬ и выходом второго эле- ричного сумматора. мента НЕ, второй вход пятого элемен- Одноразрядный четверичный сумта .РАВНОЗНАЧНОСТЬ подключен к выходу 55 матор содержит входы 1 и первого

1023322 операнда, причем на вход 1 поступа- ет старший разряд первого операнда, а на входы — младший разряд, входы 3 и 4 второго операнда, где на вход 3 поступает старший разряд, а на вход 4 — младший разряд второго операнда, вход 5 переноса из предыдущего четвернчного разряда,: элементы 6-8 НЕ, элементы 9-19 PASНОЗНАЧНОСТЬ, элементы 20-23 иэлемент, 34 ИЛИ. 10

Выходом переноса является выход

25, старшего разряда суммы выход 26, а младшего разряда-27.

Устройство работает следующим образом. 15

На входы 1 и 2 подаются старший и младший разряды четверичной цифры первого опеРанда, на входы 3 и 4старший и младший разряды четверичной цифры второго операнда, на вход 5 - цифра переноса из предыдущего четверичного разряда. На выходе 25 реализуется булева функция

Р .. =R(Х1 Х ) )(ф (Хф,Х ) Х4Х К(ХУ Х3Ъ ч Х„Хф(Х4,Х5)ч Х М Я(Хф, (5), соответствующая формированию переноса в следующий четверичный разряд, через время 4 Г, соответствующего времени задержки распространения сигнала схеме. На выходах 26 и 27, реалнэующнх соответственно булевй функции

R (® ((Х 4,Х5 ) Х )!1(Р1, Х1)),Х ), 4 „„- ММХ,Х4>,Х, ).

Через 4 снимаются сигналы стар- шего и младшего разрядов четверичной цифры суммы.

Таким образом, предлагаемое устройство позволяет производить суммирование двух четваричных цифр за время 4, обусловленное временем задержки на элементах схемы.

Сложность данного сумматора по количеству входов, что в общем случае соответствует количеству компонент при реализации устройства интегральной технологией, составляет

42 входа, в то время как сложность объекта — прототипа составляет 54 входа, при таком же времени задержки распространения сигнала на элементах схемы. Следовательно, предлагаемое устройство обладает повышенной надежностью за счет уменьшения его сложности. Структура предлагаемого ! устройства имеет лучшие характеристики по диагностируемости за счет использования элементов равнозначность, что позволяет уменьшить затраты времени на поиск и устранение неисправ.ностей.

1023322

Составитель A.Ñòåïàíîâ

Техред A,Áàáèíåö КорректорА.Дзятко

Редактор Н.Воловик

Тираж 706 Подписное

HHHHHH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рау иская наб., д. 4/5

Заказ 4213/33

° Ь

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4