Блок формирования сквозного переноса в сумматоре

Иллюстрации

Показать всеРеферат

БЛОК ФОРМИРОВАНИЯ СКВОЗНОГО ПЕРЕНОСА В СУММАТОРЕ, содержащий , в каяодом разряде четыре МДПтраиэистора , затвор из которых подключен к входу полусуммы данного разряда, исток - к входу переноса данного разряда, а сток - к вы-, ходу переноса данного разряда, затвор второго МДП-транзистора подключен к входу произведения данного, разряда, исток его - к шине нулевого потенциала блока, сток - к истоку третьего МДП-транзистора, сток третьего и исток четвертого МДП-транзисторов соединены с выходом переноса данного разряда, а их затёоры подключены к шинам первого и второго тактирующих сигналов блока соответственно , сток четвертого МДП-транзистора соединен с шиной напряжения питания блока, отличающийс я тем, что,- с целью увеличения быстродействия, каждый разряд блока, дополнительно содержит злемент ИЛИ- НЕ , элемент НЕ и пятый МДП-транзистор , сток которого подключен к исто .ку третьего МДП-транзиСтора, исток к шине нулевого потенциала блока, § затвор - к выходу элемента ИЛИ-НЕ, (Л первый вход которого соединен с входом переноса данного разряда блока, второй вход - с выходом элемента НЕ, вход которого подключен к входу полусуммы данного разряда блока.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

09) (П) А

:ЭСЮ .6 06 F 7

/ Ь " 1 с " а.

4F

ОПИСАНИЕ ИЗОБРЕТЕНИЯ: . ::,;:/

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ, "- 1 Р

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО. ДЕЛАМ ИЗОБРЕТЕНИЙ И QTHPbfNA (21) 2860041/18-24 (22).. 26.12.79 (46) 15.09.83. Бюл В 34 (72) В.Л. Дшхунян, С.С. Коваленко, В.Р. Науменков и П.P. Машевич . (53) 681.325.5(088.8) (56) 1. Патент США 9 3728532, кл.. 340-172.5, опублик. 1973.

2. Патент США В 4016546, кл. 340-172.5,.опублик. 1977 (про-: тотип). (54) (57) БЛОК ФОРМИРОВАНИЯ СКВОЗНОГО ПЕРЕНОСА В СУММАТОРЕ, соДержа.щий в каждом разряде четыре МДПтранзистора, затвор первого иэ кото-рых подключен к входу полусуммы данного разряда, исток - к входу пере-. носа данного разряда, а сток - к вы-.. ходу переноса .данного разряда, зат«вор второго МДП-транзистора подключен к входу произведения данного. разряда, исток его - к шине нулевого потенциала блока, сток — к истоку третьего МДП-транзистора, сток треть

его и исток четвертого МДП-транзисторов соединены с.выходом переноса данного разряда, а их затворы подключены к шинам первого и второго тактирующих сигналов блока соответственно, сток четвертого МДП-транзистора соединен с шиной напряжения питания блока, о т л и ч а ю щ и йс я тем, что с целью увеличения быстродействия, каждый разряд блока, дополнительно содержит элемент ИЛИНЕ, элемент НЕ и пятый МДД-транзистор, сток которого подключен к истоку третьего МДП-транзистора, исток к шине нулевого потенциала блока, O затвор — к выходу элемента ИЛИ-НЕ, первый вход которого соединен с входом переноса данного разряда блока, второй вход - с выходом элемента НЕ, вход которого подключен к входу полусуммы данного разряда блока. Я

ЪЮ

1042012

Изобретение относится к областй вычислительной техники, в частности, может быть использовано в многораз рядных арифметических устройствах, выполненных на МДП-транзисторах, входящих в состав БИС микропроцессоров . и микроЭВМ.

Известен блок формирования в сумматоре переноса с одношинной связью между разрядами сумматора, содержащий элементы И-ИЛИ-НЕ и НЕ (1) . 10

Недостатком такого блока является низкое быстродействие при построении многоразрядных арифметических устройств.

Наиболее близким к изобретению 15 является блок формирования Сквозно1о переноса в сумматоре, содержащий в каждом разряде четыре МДП-транзистора, затвор первого из которых подключен к входу полусуммы данного разряда блока, исток — к входу переноса данного разряда блока, а сток к выходу переноса данного разряда бло. ка, затвор второго МДП-транзистора подключен ко входу произведения дан. ного разряда блока, исток его — к общей шине блока, сток — к истоку третьего МДП-транзистора, сток третьего и исток четвертого МДП-транзисторов соединены с выходом переноса данного разряда блока, а их затворы подключены к шинам первого и второго тактирующих сигналов блока соответственно, сток четвертого МДП-транзистора соединен с шиной напряжения питания блока (2) .

Основным недостатком такого блока является значительное уменьшение быст родействия прн увеличении его разряд. ности, поскольку в худшем случае прохождения .переноса через все раз- 40 ряды сигнал проходит через последовательно включенные транзисторы, представляющие распределеннуюЙС -цепь задержка в которой увеличивается пропорционально разрядности блока. 45

Цель изобретения — увеличение быстродействия блока;

Для достижения поставленной цели в. блоке формирования сквозного переноса в сумматоре, содержащем в каждом разряде четыре МДП-транзистора,затвор первого из которых подклю- i чен к входу полусуммы данного разряда блока, исток — к.входу переноса дан-, ного разряда, а сток — к выходу переноса данного разряда, затвор второго МДП-транзистора подключен к входу произведения данного разряда, исток его — к шине нулевого потенциала блока, сток - к истоку третьего МДП- 60 транзистора, сток третьего и исток четвертого МДН-транзисторов соедйнены с выходом переноса данного разря. да, а их затворы подключены к шинам первого и второго тактирующих сигна- 65 лов блока соответственно, сток четвертого МДП-транзистора соединен с шиной напряжения питания блока, каждый разряд блока дополнительно содержит элемент ИЛИ-НЕ, элемент НЕ и пятый МДП-транзистор, сток которого подключен к истоку третьего МДП-. транзистора, ист9к — к шине нулевого потенциала блока, затвор — к выходу элемента ИЛИ-HE первый вход которого соединен с входом переноса данного разряда блока, второй вход с выходом элемента НЕ, вход которого подключен к входу полумассы данного разряда блока.

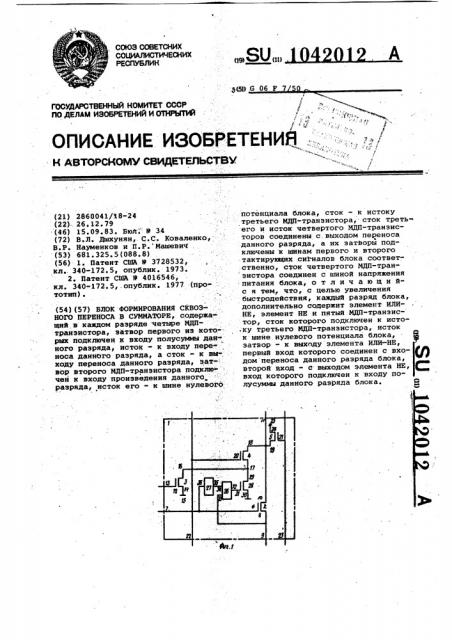

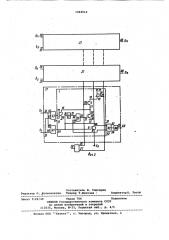

На фиг. 1 представлена структурная схема .блока формирования сквозного переноса; на фиг. 2 — пример исполнения многоразрядного сумматора с использованием данного блока формирования сквозного переноса.

Каждый разряд 1 блока содержит четыре МДП-транзистора 2-5, затвор

6 транзистора 2 подключен к входу 7 полусуммы,даиного разряда 1 блока, исток 8 — к входу 9 переноса данного разряда 1 блока, а сток 10 - к выходу 11 переноса данного разряда 1 блока. Затвор 12 транзистора 3 подключен к входу 13 произведения данного разряда 1 блока, исток 14 его к шине 15 нулевого потенциала, сток.

16 — к истоку 17 третьего транзистора 4, сток 18 транзистора 4 и исток

19 .трайзистора 5 соединены с выходами переноса 11, а их затворы 20.,21 подключены .к входам 22,23 первого и второго такТирующих сигналов блока соответственно, сток 24 транзистора

4 соединен с шиной питания 25. Каждый разряд 1 блока содержит также элемент ИЛИ-HE HE 27 и

МДП-транзистор 28, сток 29 которого подключен к истоку 17 транзистора 4, исток 30 - к шине 15.нулевого потенциала, затвор 31 — к выходу 32 элемента ИЛИ-НЕ 26, первый вход 33 которого подключен к входу переноса 9, второй 34 — к выходу 35 элемента

НЕ 27, вход 36 которого соединен с входом полусуммы 7.

Блок работает следующим образом.

На вход 7 полусуммы данного разряда 1 блока подают сумму по щой 2 операндов а,,1Ь1, на вход 13 произведения - логическое произведение операндов а. Ь„, на вход 9 переноса инверсию перейоса с1, на входы 22 и 23 первого и второго тактирующих сигналов подаются потенциалы логического нуля H единицы соответственно, затем переключают сигналы на входах 22 и 23 первого и второго тактирукицих сигналов на логическую еди- . ницу и логический нуль соответственно, на выходе 11 переноса формируется сигнал инверсии переноса с 1 =

l 04 .012

= а„ Ь,V с> (а; >Ь.;), причем, если а;Ь

1, а а; Ф Ь; = 1, то сигнал перейоса распространяется по двум цепям одновременно: через транзистор 2 и через элемент ИЛИ-НЕ 26 и транзисторы 28 и 4. Выигрыш в быстродействии получается за счет того, что транзистор 28 и транзистор 4 являются дополнительными цепями разряда монтажной емкости, сосредоточенной на выходе переноса 11.

На фиг. 2 приведен пример использования блока переноса для пострОения многоразрядного сумматора, каж-.. дый разряд 3.7 которого имеет входы операндов 38,39, выход 40 суммы и !5 содержит соответствующий разряд 1 блока переноса, два элемента ИСКЛЮ-ЧАЮЩЕЕ ИЛИ 41,42, элемент И 43 и . элемент НЕ 44, входы 45 и 46, элементов И и ИСКЛЮЧММЦЕЕ ИЛИ подкдючены к входу первого операнда 38, входы 47, 48 этих элементов — к входу второго операнда 39, выход 49 элемента И 43 подключен к входу 13. произведения разряда 1 блока перено- 5 са, выход 50 элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 41 подключен к входу 7 полус1(ммы разряда l блока переноса и к первому входу 51 элемента ИСКЛЮЧИОЩЕЕ..

ИЛИ 42, второй вход 52 которого coe - З0 дйнен .с входом 9 переноса разряда- бло ка переноса, выход 53 элемента ИСКЛЮ-:

ЧМОЩЕЕ ИЛИ. 42 соединен с входом 54 элемента НЕ 44,выход 55 которого сое ринен с выходом суммы 40.ВхОд ц :. реноса, выход 53 элемента ИСКЛЮЧЯ6.ЩЕЕ ИЛЙ 42 соединен с входом 54 эле-. мента НЕ 44, выход 55 которого соединен с выходом суммы 40. Вход перейоса 9 разряда 1 блока переноса aepsoro разряда соединен с шиной 25 на- 40 пряжения питания, входы 9 переноса остальных разрядов соединены с выходами .11 переноса предыдущих разрядов, входы 22 и 23 первого и второго тактирующих сигналов соединеми с .вы- 45 ходами 56,57 источника 58 тактирующих сигналов.

Подав на входы 38, 39 операнды. (a;), (ЬД, i = 1,2,...,n получаем на выходах 49,50 элемента И 43 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41 произведение операндов а,, b и полусуммы а; Ь

1,2,...,n, которые поступают на вход произведения 13 и вход 7 полусуммы разряда 1 блока переноса. Затем источник 58 тактирующих сигналов переключает первый и второй тактирующие сигналы из состояния логического нуля и логической .единицы в состояния логической единицы и логического нуля соответственно, на вход

9 подается напряжение питания, что соответствует отсутствию переноса,. на выходах. 11 формируется сигнал инверсии перейоса, который распространяется по цепи переноса. В худшем случае сигнал переноса распространяется от первого до последнего разряда, причем распространение сигнала идет двумя путями в каждом разряде: через транзистор 2 и через элемент ИЛИ-НЕ 26 и транзисторы 28 и 4, причем транзистор 2 является пассивным элементом, но имеет малую задержку распространения сигнала, а элемент ИЛИ-НЕ 26 и транзисторы 28 и 4 обладают усилительными свойствами, но имеют большую задержку распространения. При большой разрядности сумматора сигнал переноса, распространяясь через транзистор 2, проходит несколько разрядов (пока срабатывает элемент ИЛИ-НЕ 26. и транзисторы 4 и 28) и усиливается ими, тем самым устраняется затухание сигнала в цепи переноса, сигнал инверсии переноса с .с входа 9 переноса поступает на вход элемента ИСКЛЮЧА- >

ЮЩЕЕ ИЛИ 42 и на выходе сумматора формируется сумма S < = (а tb,) с4=

= a; a b;ac > где i = 1,2,...,n.

Как показал расчет и экспериментальные результа1ы на образцах СВИС микро 2 ЭВМ, предложенное решение позволяет уменьшить время суммирования 16-разрядных операндов до

150 нс, что в 8 - 10 раз превышает быстродействие прототипа.

1042012

Составитель Н. Слюсарев

Техред T.Ìàòî÷êà 1 КорректорО. Тигор

Редактор О. Колесникова

Филиал ППП Патент, г. ужгород, ул. Проектная, 4

Заказ 7129/49 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений к открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5