Устройство для задержки цифровой информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для задержки цифровой информации. Целью изобретения является снижение максимально возможной суммарной погрешности задерживаемого массива в случае отказа любого разряда накопителя. Устройство содержит входной коммутатор 1, накопитель 2, счетчик 3 адреса, регистр 4 сигналов задержки , регистр 5 информации и выходной коммутатор 6, выходы 9 которого являются выходами устройства, информационными входами 8 которого являются разрядные входы входного коммутатора 1. Цель достигается за счет того, что устройство располагает информационные разряды задерживаемого массива в накопителе 2 таким образом , что отказ любого из разрядов накопителя 2, независимо от его позиции, приводит к средней суммарной погрешности всего массива, которая значительно меньше максимально возможной, возникающей в случае потери старших разрядов слов массива информации . 4 ил., 1 табл. о (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1383322 A 1 (51) 4 G 06 F 1 04 G ll С 19 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, Q

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ фиг.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4131768/24-24 (22) 13.10.86 (46) 23.03.88. Бюл. № 11 (72) В. Н. Лацин, Е. Л. Полин, А. В. Дрозд, В. П. Карпенко и В. В. Шабадаш (53) 681.327 (088.8) (56) Авторское свидетельство СССР № 932566, кл. G 11 С 19/00, 1980.

Авторское свидетельство СССР № 1193653, кл. G 06 F 1/04, 1984. (54) УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ

ЦИФРОВОЙ ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике и может быть использовано для задержки цифровой информации. Целью изобретения является снижение максимально возможной суммарной погрешности задерживаемого массива в случае отказа любого разряда накопителя. Устройство содержит входной коммутатор 1, накопитель 2, счетчик 3 адреса, регистр 4 сигналов задержки, регистр 5 информации и выходной коммутатор 6, выходы 9 которого являются выходами устройства, информационными входами 8 которого являются разрядные входы входного коммутатора 1. Цель достигается за счет того, что устройство располагает информационные разряды задерживаемого массива в накопителе 2 таким образом, что отказ любого из разрядов накопителя 2, независимо от его позиции, приводит к средней суммарной погрешности всего массива, которая значительно меньше максимально возможной, возникающей в случае потери старших разрядов слов массива информации. 4 ил., 1 табл.

1383322

В начальный момент времени происходит обнуление регистров 4 и 5 устройства. Цепи обнуления условно не показаны.

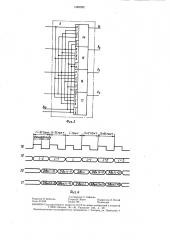

Затем на входы 8 начинают поступать

5 m-разрядные слова задерживаемого массива, сопровождаемые синхроимпульсами 18 типа меандр на входе 7 (фиг. 4). Причем каждый синхроимпульс соответствует одному такту, во время первой половины каждого такта происходит чтение информации из ячеек одного столбца накопителя 2, адрес которого выдается счетчиком 3, а во время второй половины такта — запись информации в этот же столбец ячеек накопителя 2. Счетчик 3 последовательно перебирает адреса

15 столбцов накопителя 2. Таким образом, число К тактов задержки слов массива опреляется коэффициентом пересчета счетчика 3.

Информация, считанная в данном такте, записывается в регистр 5 по отрицательному перепаду синхроимпульса на входе 7.

Коммутатор 1 осуществляет поразрядную коммутацию входной информации таким образом, что в каждом следующем такте старшие и последующие разряды, поступающие в накопитель 2, поочередно записываются в

25 различные разряды накопителя 2, циклически сдвигаясь на один разряд. Расположение разрядов задерживаемых слов а, в, с, d u так далее накопителей 2 для случая четырех разрядов показано в таблице.

Номер столбца накопителя

1 ) Разряды накопителя

1 2 3 4 5 6 7 8

d2 е1 f4 g3 h2

d3 е2 fi g4 h3

d4 еЗ К2 g1 h4

d1 е4 f3 g2 h1 а1 Ь1 сЗ а2 Ь1 с4 аЗ Ь2 с1 а4 b3 с2

Как видно из приведенного в таблице 45 примера старшие а, в и так далее и более млашие разряды задерживаемых слов последовательно оказываются в различных разрядах накопителя 2, вследствие чего отказ любого из разрядов накопителя 2 приводит к усреднению, т. е. некоторому снижению погрешности всего задерживаемого массива.

Управление входным коммутатором 1 осуществляется с помощью младших разрядов счетчика 3, задержанных на половину такта 55 на регистре 4, так как входная и выходная информации которого задерживаются на половину такта относительно адресных сигналов 19 на выходах счетчика 3 (фиг. 4).

Формула изобретения

Изобретение относится к вычислительной технике и может быть применено для задержки массива информации.

Цель изобретения — повышение достоверности передачи задерживаемого массива и н форм а ци и.

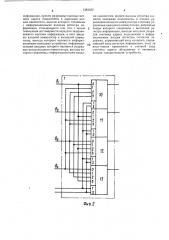

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 и 3 — функциональные схемы соответственно входного и выходного коммутаторов для случая задержки, например, четырех разрядных слов; на фиг. 4 — временные диаграммы, поясняющие работу устройства.

Устройство содержит (фиг. 1) входной коммутатор 1, накопитель 2, счетчик 3 адреса, регистр 4 кода задержки, регистр 5 информации, выходной коммутатор 6, вход 7 синхронизации устройства, информационные входы 8, информационные выходы 9. Входной коммутатор 1 содержит (фиг. 2) мультиплексоры 10 — 13. Выходной коммутатор 6 содержит (фиг. 3) мультиплексоры 14 — 17.

Кроме того, показаны синхроимпульсы 18 на входе 7 устройства, сигналы 19 на адресных выходах счетчика 3 адреса, информационные сигналы 20 и 21 соответственно на входах 8 и выходах 9 устройства (фиг. 4).

Устройство работает следующим образом.

Коммутатор 6 выполняет обратное преобразование считываемой информации для восстановления естественного расположения старших разрядов и управляется аналогично коммутатору 1.

Таким образом, предлагаемое устройство обеспечивает среднюю суммарную погрешность задерживаемого массива, независящую от позиции отказавшего разряда накопителя 2.

Устройство для задержки цифровой информации, содержащее накопитель, счетчик адреса, регистр кода задержки и регистр

1383322

Фиг,2 информации, причем разрядные выходы счетчика адреса подключены к адресным входам накопителя, выходы которого соединены с информационными входами регистра информации, отличающееся тем, что, с целью повышения достоверности передачи задерживаемого массива информации, в него введены входной коммутатор и выходной коммутатор, выходы которого являются информационными выходами устройства, информационными входами которого являются разрядные входы входного коммутатора, выходы которого соединены с информационными входами накопителя, причем выходы регистра сигналов задержки подключены к входам управления входного коммутатора и входам управления выходного коммутатора, разрядные

5 входы которого соединены с выходами регистра информации, выходы младших разрядов счетчика адреса подключены к информационным входам регистра сигналов задержки, управляющий вход которого, управляющий вход регистра информации, вход записи-чтения накопителя и счетный вход счетчика адреса объединены и являются входом синхронизации устройства.

1383322 с 2 г+г

Збх(-2) 3)Вх(-1) ЗРх с Эбх <+ ) Убх(а+Э

Мыхй-2 Мых(-7) Ъдыхi Зй хй / Р ix(i+2) Составитель Т. Зайцева

Редактор Н. Бобкова Техред И. Верес Корректор Л. Патай

Заказ 913/46 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4