Запоминающее устройство с диагональной адресацией

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в качестве оперативной памяти ортогональной ЭВМ. Целью изобретения является расширение функциональных возможностей устройства за счет варьирования кода начала считываемого разрядного столбца данных. Устройство содержит m блоков 3 памяти , m сумматоров 1, регистр 4 вводавывода и m коммутаторов адреса 2. Цель изобретения достигается введением коммутаторов адреса, причем выходы коммутатора адреса каждого предыдущего разряда устройства, начиная с первого, соединены с одними входами сумматора следующего разряда , выходы коммутатора адреса последнего разряда подключены к одним входам сумматора первого разряда устройства . 1 ил. с (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (19) ()1) (5)) 4 С 11 С 15/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ВСЕ"";

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 13, cr, t

БИ1ЛЫ. )," . у, К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4166714/24-24 (22) 24.12.86 (46) 30.05.88. Бюл. Ф 20 (72) Е.Л. Полин, В.В. Шабадаш, В.А. Минченко, А.В. Дрозд и В.Н; Лацин (53) 681.327.6(088.8) (56) Кохонен Т. Ассоциативные запоминающие устройства. — М.: Мир, 1982, с. 178, 179. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИАГОНАЛЬНОЙ АДРЕСАЦИЕЙ (57) Изобретение относится к вычислительной технике и может быть использовано в качестве оперативной памяти ортогональной ЭВМ. Целью иэобретения является расширение функциональных возможностей устройства эа счет варьирования кода начала считы» ваемого разрядного столбца данных.

Устройство содержит m блоков 3 памяти, m сумматоров 1, регистр 4 вводавывода и m коммутаторов адреса 2.

Цель изобретения достигается введением коммутаторов адреса, причем выходы коммутатора адреса каждого предыдущего разряда устройства, начиная с первого, соединены с одними входами сумматора следующего разряда, выходы коммутатора адреса последнего разряда подключены к одним входам сумматора первого разряда устройства. 1 ил.

1399819

Изобретение относится к вычислительной технике и может быть использовано в качестве оперативной памяти ортогональной ЭВМ.

Цель изобретения — расширение области применения устройства эа счет варьирования кода начала считываемого разрядного столбца данных.

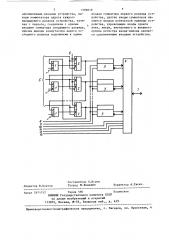

На чертеже представлена структурная схема запоминающего устройства с диагональной адресацией.

Устройство содержит m сумматоров

1, m коммутаторов адреса 2, выполненных в виде элементов 2И-2И-2ИЛИ, 15

m блоков памяти 3 с встроенными адресными дешифраторами, регистр вводавывода 4, входы кода начала разрядного столбца 5, адресные входы устройства 6, информационные входы-выходы устройства 7, вход 8 записи, вход 9 считывания, вход 10 сдвига вниз, вход 11 сдвига вверх, вход 12 внешнего приема, вход 13 внутреннего приема. 25

Устройство работает следующим образом.

Процедура записи в память. Данные, подлежащие записи в память, поступают на информационные входы-выходы устрой 30 ства 7 и при поступлении сигнала

"Прием внешний" 12 помещаются в сдвиговый регистр ввода-вывода 4, Затем при поступлении сигнала "Сдвиг вниз на е разрядов" 10, содержимое регист- 35 ра циклически сдвигается вниз на число разрядов е, определяемое младшими разрядами кода адреса. На входы кода начала разрядного столбца 5 поступает код 111- 11, таким образом 4р на входы адресных дешифраторов всех блоков памяти 3 через элементы

2И-2И-2ИЛИ 2 транслируется значение адреса, поданного на адресные входы устройства 6. Далее после поступле- 45 ния сигнала "Запись" 8 происходит этап записи, и информация из сдвигового регистра 4 заносится в соответствующие ячейки блоков памяти 3.

Процедура считывания горизонталь- 50 ного слова.

На входы задания кода начала разрядного столбца 5 поступает код

111-11. На адресные входы устройства

6 поступает код адреса считываемого слова. Далее после поступления сигнала "Чтение" 9 происходит этап считывания и информация из выбранных ячеек блоков памяти 3 по сигналу "Прием внутренний" 13 заносится в сдвиговый регистр ввода-вывода 4. Для восстановления первоначального порядка элементов слово по сигналу Сдвиг вверх на е разрядов циклически сдвигается вверх, аналогично сдвигу при процедуре записи.

Процедура считывания разрядного столбца.

На входы кода начального разрядного столбца 5 поступает унитарный код (все нули и одна единица), причем единица указывает блок памяти, в ячейке которого хранится первый разряд разрядного столбца ° На входы встроенного адресного дешифратора выбранного блока памяти 3 через элемент 2И-2И-2ИЛИ 2 транслируется код адреса, поданный на адресные входы устройства 6, а на модули памяти с последующими номерами - последовательно увеличенный на единицу. Далее происходит этап считывания, и информация иэ выбранных ячеек блоков памяти 3 заносится в сдвиговый регистр ввода-вывода 4. Для восстановления первоначального порядка элементов, слово циклически сдвигается вверх, аналогично сдвигу или процедуре считывания горизонтального слова.

Формула изобретения

Запоминающее устройство с диагональной адресацией, содержащее блоки памяти, информационные входы и выходы которых соединены с соответствующими выходами и входами регистра ввода-вывода, вход-выход которого является информационным входом-выходом устройства, сумматоры по числу блоков памяти, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства за счет варьирования кода начала считываемого разрядного столбца данных, в устройство введены коммутаторы адреса, управляющие входы и информационные входы первой группы которых являются соответственно входами кода начала разрядного столбца и адресными входами устройства, выходы сумматоров подключены к информационным входам второй группы соответствующих коммутаторов адреса, выходы которых соединены с адресными входами соответствующих блоков памяти, входы записи и считывания которых обьединены и являются з 139981 одноименными входами устройства, выходы коммутатора адреса каждого предыдущего разряда устройства, начиная с первого, соединены с одними входами сумматора следующего разряда, причем выходы коммутатора адреса последнего разряда подключены к одним

Составитель О.Исаев

Техред М.Ходанич

Корректор А,Тяско

Редактор В,Ковтун

Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35 ° Раушская наб., д. 4/5

Заказ 2Ь71/52

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектн я, ектная 4 д

9 ка 1

r2 а входам сумматора первого разряда устройства, другие входы сумматоров являются входом логической единицы устройства, управляющие входы сдвига вниз, вверх, внутреннего и внешнего приема регистра ввода-вывода являются одноименными входами устройства.