Безопасный логический элемент

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике ,в частности, к устройствам железнодорожной автоматики. Целью изобретения является повышение надежности работы за счет контроля динамических сигналов. Безопасный логический элемент содержит четыре конденсатора, четыре диода, ключ, шесть резисторов, транзистор и пороговое устройство. За счет нового включения транзистора и введения порогового устройства повышается надежность работы при отклонении параметров элементов. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) 4 Н 03 К 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ а

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГКНТ СССР

К АВТОРСКОМ .Ф СВИДЕТЕЛЬСТВУ (21) 4339733/24-21 (22) 07. 12. 87 (46) 07.08.89. Бюп. N - 29 . (71) Конструкторское бюро Главного управления сигнализации и связи MHC

СССР (72) Е.Н.Розенберг, В.И.Зорин, В.И.Любимов и И.И.Яблонский (53) 621.374(088.8) (56) Патент США Н 4320315, кл. H 03 К 19/007, 1982 °

Заявка Франции Р 2553605, кл. Н 03 К 19/007, 1985.

„„SU„„1499479 А 1

2 (54) БЕЗОПАСНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ (57) Изобретение отиосится к импульсной технике, в частности к устройствам железнодорожной автоматики. Целью изобретения является повышение надежности работы за счет контроля динамических сигналов. Безопасный логический элемент содержит четыре конденсатора, четыре диода, ключ, шесть резисторов, транзистор и пороговое устройство. За счет нового включения транзистора и введения порогового устройства повышается надежность работы при отклонении параметров элементов. 2 ил.

3 149947

Изобретение относится к импульсной технике, а именно к устройствам, применяемым в особо ответственных системах, например, железнодорожной автоматики, где должно соблюдаться требование, чтобы любой отказ элемента автоматики не приводил систему,в более опасное (аварийное) состояние, чем существовавшее до отказа. 10

Цель изобретения - повышение надежности безопасного логического элемента.

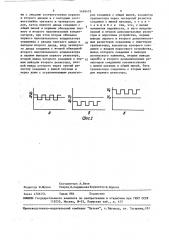

На фиг. 1 представлена принципиальная схема безопасного логического 15 элемента; на фиг. 2 - диаграммы напряжений на первом транзисторе.

Элемент содержит первый 1 и второй 2 разделительные конденсаторы, первые обкладки которых соединены 20 соответственно с первым 3 и вторым 4 входами устройства, а вторые обкладки - с анодами соответственно первого 5 и второго б диодов и с катодами соответственно третьего 7 и четверто- 25

ro 8 диодов, катод диода 5 соединен с общей шиной и первыми обкладками первого 9 и второго 10 накопительных конденсаторов, вторая обкладка конденсатора 9 соединена с анодом диода, 30

7 и катодом диода 6, анод диода 8 соединен с Второи обкладкой конден" сатора 10 и первым выводом первого резистора 11, второй вывод которого соединен с базой транзистора 12 и 35 первым выводом второго резистора 13, второй вывод которого через третий резистор 14 соединен с шиной питания, а через ключ 15 с ограничивающим резистором 16 — с общей шиной, коллек- 40 тор транзистора 12 соединен через четвертый резистор 17 с шиной 18 питания, а его эмиттер — с первыми выводами первого 19 и второго 20 до-. полнительных резисторов, коллектоР 45 транзистора 12 соединен с входом порогового устройства 21, выход которого соединен с выходом 22 устройства.

Вторые выводы резисторов 19 и 20 соединены соответственно с шиной 18 питания и общей шиной.

Безопасный логический элемент работает следующим образом.

При поступлении частотных сигналов на входы,3 и 4 через конденсатор 1 и диоды 5 и 7 осуществляется заряд конденсатора 9. Заряд конденсатора 10 осуществляется переменным сигналом с второго входа 4 через конденсатор 2

9 4 и диоды 6 и 8. Напряжение на конденсаторе 10 равно сумме напряжений на конденсаторе 9 и выпрямленного сигнала с второго входа ° Тем самым осуществляется реализация логической функции "И ° Уровень напряжения на конденсаторе 10 проверяется компаратором на транзисторе 12. На эмиттере этого транзистора потенциал определяется делителем напряжения на резисторах 19 и 20, а на базе потенциал при закрытом ключе 15 — делителем напряжения на резисторах 11,13 и 14 так, что транзистор 12 закрыт, а при бткрытии ключа 15 за счет падения напряжения на резисторе 16 потенциал эмиттера транзистора 12 понижается и, следовательно, транзистор 12 открывается.

Таким образом, частота контрольного сигнала с входа ключа 15 поступает на коллектор транзистора 12 и оттуда через пороговое устройство 21 на выход 22. Этим обеспечивается работа порогового устройства 21 при сниженном потенциале входа. С выхода порогового устройства 21 снимается выходной сигнал. На фиг. 2а показаны потенциалы базы и эмиттера транзистора 12 при наличии двух входных частотных сигналов и исправных элементах схемы.

Если присутствует только один сигнал, то потенциал эмиттера выше потенциала базы и транзистор 12 закрыт, следовательно, частотный сигнал на выходе порогового устройства 21 отсутствует, Выбором величины ограничивающего резистора 16 обеспечивается зона контроля параметров элементов устройства, так как для транзистора 12 в случае отказов элементов устройства не выполняется условие периодическаго изменения потенциала базы относительно эмиттера, а следовательно, отсутствует частотный сигнал на его выходе.

Возможные варианты потенциалов базы приведены на фиг. 2б,в.

Таким образом, обеспечивается повьппение надежности при отклонении параметров элементов устройства.

Формула и з о б р е т е н и я

Безопасный логический элемент, содержащий первый и второй разделительные конденсаторы, первые обкладки которых соединены соответственно с первым и вторым входами логического элемента а вторые обкладки соепинег

Э ф

Составитель А.Янов

Техред Л. Сердюкова Корректор Н. Король

Редактор И.Шулла

Заказ 4706/54 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина, 101

5 149947 ны с анодами соответственно первого и второго диодов и с катодами соответствейно третьего и четвертого диодов, катод первого, диода соединен с общей шиной и первыми обкладками пер5

sего и второго накопительных конденсаторов, при этом вторая обкладка первого накопительного конденсатора соединена с анодом третьего диода и 10 катодом второго диода, анод четвертого диода соединен с второй обкладкой второго накопительного конденсатора и первым выводом первого резистора, второй вывод которого соединен с пер- 15 вым выводом второго резистора, вто- рой вывод которого через третий резистор соединен с шиной питания и через ключ с ограничивающим реэисто-;

9 6 ром соединен с общей шиной, коллектор транзистора через четвертый резистор соединен с шиной питания, о т л и— ч а ю шийся тем, что, с целью повышения надежности, в него введены первый и второй дополнительные резисторы и пороговое устройство, первые выводы первого и второго дополнительных резисторов соединены с эмиттером транзистора, коллектор которого соединен с входом порогового устройства, выход которого соединен с выходом логического элемента, вторые выводы первого и второго дополнительных резисторов соединены соответственно с шиной питания и общей шиной, база транзистора соединена с вторым выводом первого резистора.