Тестопригодный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Цель изобретения - повышение быстродействия, обеспечение тестопригодности. Цель достигается тем, что тестопригодный сумматор, содержащий в каждом разряде входы первого и второго операндов, вход переноса, два элемента РАВНОЗНАЧНОСТЬ, причем входы первого элемента соединены со входами первого и второго операндов, выход соединен с первым входом второго элемента РАЗНОЗНАЧНОСТЬ, второй вход которого соединен со входом переноса из предыдущего разряда, а выход является выходом суммы, сумматор в каждом разряде имеет первый и второй элементы МАЖОРИТАРНОСТЬ, причем первый и второй входы первого элемента соединены со входами первого и второго операндов, третий входсо входом переноса из предыдущего разряда, а выход является выходом переноса в следующий разряд, первый вход второго элемента МАЖОРИТАРНОСТЬ соединен с выходом суммы, второй вход соединен с выходом второго элемента МАЖОРИТАРНОСТЬ предыдущего разряда, а третий вход соединен со входом управления устройства. 1 ил., 1 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

1 у 4 6 06 F 11/26, 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

S; А;9В;®Р;;

Р; А,Р; ЧА;В;МВ;Р;.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР t (21) 4363849/24-24 (22) 17.11.87 (46) 15.11.89. Бюл.Р 42 (72) M.Ì.Татур, С.Н.Изотов, В.П.Якуш и А.В.Драенков (53) 68).3(088.8) (56) Саофалов К.Г. и др. Цифровые электронные вычислительные машины.

К.: Вища школа, 1983, с.146.

Авторское свидетельство СССР .

Р 1251070, кл. С 06 F ll/26, 1986. (54) ТЕСТОПРИГОДНЫИ СУММАТОР (57) Изобретение относится к вычислительной технике. Цель изобретенияповышение быстродействия, обеспечение тестопригодности. Цель достигает-. ся тем, что тестопригодный сумматор, содержащий в каждом разряде входы первого и второго операндов, вход переноса, два элемента РАВНОЗНАЧНОСТЬ, Изобретение относится к вычислительной технике и может быть использовано для построения арифметических устройств.

Целью изобретения является повышение быстродействия и обеспечение тестопригодности.

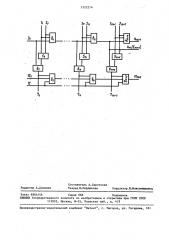

На чертеже представлена функциональная схема тестопригодного сумматора.

Сумматор содержит информационные входы операндов А, В - 1;, 2;, переноса P — 3;, выход переноса в следующий разряд P, - 4;, элементы РАВНОЗНАЧНОСТЬ 5,, 6,, выход суммы причем входы первого элемента соединены со входами первого и второго операндов, выход соединен с первым входом второго элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен со входом переноса из предыдущего разряда, а выход является выходом суммы, сумматор в каждом разрезе имеет первый и второй элементы МАЖОРИТАРНОСТЪ, причем первый и второй; входы первого элемента соединены со входами первого и второго операндов, третий вход - со входом переноса из предыдущего разряда, а выход является выходом переноса в следующий разряд, первый вход второго элемента МАЖОРИТАРНОСТЬ соединен с выходом суммы, второй вход соединен с выходом второго элемента

МАЖОРИТАРНОСТЬ предыдущего разряда, а третий вход соединен со входом управления устройства. 1 нл., 1 табл.

S, — 71, элементы МАЖОРИТАРНОСТЬ

8;,9;, вход контроля 10;, выход контроля 11;, вход управления 12.

Сумматор функционирует следующим образом.

При подаче на информационные входы операндов А, В и переноса P каждый разряд выполняет функции

Для построения и-разрядного тестопригодного сумматора необходимо со1522214

Проверяющий тест

° ме ыыыеееы

1(А) 2(В) 3, (Р, ) 7(S) 10, 12 11„, Все 0

Все 1

Все 0

Все 0

Все 1

Все 1

Все 0

Все 1

Все 0

Все 1

Все 1

Все 1

Все О

Все О

Все О

Все. 1

1

0 .1

О

О

Все 0

Все 1

Все 1 .Все 0

Все 1

Все 0

Все О

Все 1

О 1 О

1 .О l

1 0 1

0 1 0

1 0 1

О 1 0

1 1 1

0 0 0 единить по цепям переноса и контроля

n + l одноразрядный сумматор. Дополнительный разряд предназначен для обеспечения проверки элемента МАЖОРИТАРНОСТЬ 8„. Элемент MAROPHTAPHOCTb

8 +,, входы 1 „+, и 2„+,, выходы

4 „„и 7„+, не задействованы, а предназначены для возможности слайсового увеличения разрядности. Выход переноса и-разрядного сумматора

4„(3 „,). При разрядности п сумматора на входы 1 „+ и 2 n+< подают сигналы операндов одного из разрядов,; например, -ro. На чертеже указанное условие показано пунктиром.

Тестовое диагностирование осуществляется проверяющим тестом, приведенным в таблице, диагноз снимается с выхода .Контроля 11..1 n+1-разряда

Первые шесть наборов теста осуществляют проверку константных неисправностей логических элементов, за исключением неисправностей входов логических элементов ИАЖОРИТАРНОСТЬ 9;, соединенных со входом управления 12, проверяемых дополнительными седьмым и восьмым наборами.

Устройство позволяет проверять работоспособность по одному контроль" ному выходу, причем наращивание разрядности не влияет на порядок включения дополнительных средств и алгоритм проверки, Формула и з обретения

Тестопригодный сумматор, содержащий в каждом разряде входы первого и второго операндов, вход переноса, два элемента РАВНОЗНАЧНОСТЬ, причем первый и второй входы первого элемента РАВНОЗНАЧНОСТЬ соединены с входами первого и второго операндов соответственно, выход первого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом второго элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с входом переноса предыдущего разряда, выход второго элемента РАВНОЗНАЧНОСТЬ является соответствующим разрядным выходом суммы сумматора, о т л и ч а ю щ и йс я тем, что, целью повышения быстро» действия и обеспечения тестопригодности, сумматор содержит в каждом разРЯде Два элемента ИАЖОРИТАРНОСТЬ, причем в каждом разряде первый и второй, входы первого элемента МАЖОРИТАРНОСТЬ соединены с входами первого и второго

25 операндов, третий вход - c входом переноса предыдущего разряда, выход первого элемента:MNKOPHTAPHOCTb является выходом переноса в следующий разряд, первый вход второго элемента

ИАЖОРИТАРНОСТЬ соединен с выходом суммы соответствующего разряда, второй вход второго элемента ИАЖОРИТАРНОСТЬ соединен с выходом второго элемента

ИАЖОРИТАРНОСТЬ предыдущего разряда, третий вход второго элемента ИАЖОРИ-.

TAPH0CTb соединен с входом режима .работы сумматора.

I сумматора

1522214

11 gf

1а+ 7ки

Ь 2

Ь+1

Составитель А.Сиротская

Техред Л. Сердюкова

Редактор А.Долинич

Корректор, М.Максимишннец

Заказ 6964/46 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101