Ячейка матричного процессора

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для построения однородных матричных процессоров. Цель изобретения - повышение однородности структуры матричных процессоров и расширение функциональных возможностей за счет вычисления полиномов произвольных степеней. С этой целью в ячейке матричного процессора, содержащей три сумматора и сумматор-вычитатель, изменены соответствующие связи. 2 ил.

СОЮЗ СОВЕТСНИХ

СО11ИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

У1

К- (3 при х хх1;

-1 при х =0

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГННТ СССР

1 (21) 4145210/24-24 (22) 08.09.86 (46) 30.12.89. Бюл. ¹ 48 (71) Киевский институт инженеров гражданской авиации им. 60-летия

СССР и Институт проблем моделирова- ния в энергетике АН УССР (72) А.И.Стасюк, А.Г.Корченко, Н.И.Паламаренко, И.К.Жига, С.Ф.Кучугурный и И.Ф.Зубенко (53) 681.325(088.8) (56) Авторское свидетельство СССР № 1288692, кл. G 06 F 7/50, 15/30, 1985.

Авторское свидетельство СССР № 1291978, кл. G 06 F 7/544, 1985.

Изобретение относится к вычислительной технике и может быть исполь- зовано для построения однородных матричных процессоров.

Цель изобретения — повышение однородности структуры матричных процессоров и расширения функциональных возможностей за счет вычисления полиномов произвольных степеней.

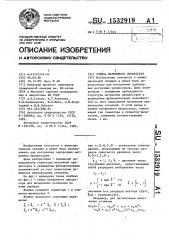

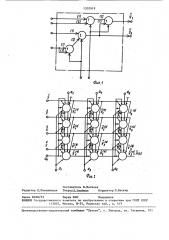

На фиг.1 приведена схема ячейки; на фиг.2 — схема матричного процессора для вычисления полиномов на этих ячейках.

Ячейка содержит сумматоры 1 и сумматор-вычитатель 2.

Ячейка реализует следующие выражения ч у -)ч к ч к у1 а1 + 2 а х+у»х

- ),у -) у у 2 а + 2 а р, ÄÄSUÄÄ 1532919 А1

2 (54) ЯЧЕЙКА МАТРИЧНОГО ПРОЦЕССОРА (57) Изобретение относится к вычислительной технике и может быть использовано для построения однородных матричных процессоров. Цель изобретения — повьппение однородности структуры матричных процессоров и расширение функциональных возможнос=

I тей эа свет вычисления полиномов произвольных степеней. С этой целью в ячейке матричного процессора, содержащей три сумматора и сумматор-вычитатель, изменены соответствующие связи. 2 ил. где п;(» d,2,3) — показатели степени двойки, указывающие на сколько разрядов сдвигается двоичное число

Х;(i=1,2,3); у,. = 1, 2; а; - двоичные числа .

) (раз рядные векторы), представляющие собой разрядное изображение чисел значения k-x разрядов вектора х(К=1;

m, m — разрядность) .

Например, для организации вычисления полинома

p(x)= (... (а xа + а,x + аа)х +

+а х + а ) х +а(,».,)х +aÄ< x+a„, 1532919 и m=4 имеет вид:

Ч (t) -1 1 -.< <) < -e, И <-0

У, ay+2 а, х +2 $ z 2 f, =2 а,+2 a p/z, <) -e г - () 1) <о

У У + 2 а,х+2 х; 2 =2 +2 а,р/х

Р(х)-У y » + 2 а х + 2 $ x"

2 Фм(ъ) 2 Ф ()) 2 В ()) 1 э у4 у ь + У p/õ

Система разрядных уравнений при и 6

), Ячейки в параллельном устройстве 15 я вычисления полинома работают слеующим образом.

В исходном состоянии на разряды

ыхода аргумента подаются разряды начений х, а на вход коэффициентов 20 оответственно коэффициенты а,.- а6, а- вход нулевого коэффициента подаетя коэффициент а . После этого в стройстве протекает переходный проесс по.окончании которого на выходе стройства образуется, искомый реультат у р(х).

v +) ч з

Формула иэ обретения

Ячейка матричного процессора, соержащая три сумматора и сумматорычитатель, выход которого соединен входами первого слагаемого первого умматора, выход которого является ервым информационным входом ячейки, ервый управляющий вход которой сое-:: динен с входом режима сумматора-выЧитателя, первый информационный вход которого является первым информацион-. 40 ным входом ячейки, второй информа-. ционный вход которой соединен с входом первого слагаемого второго сумматора, выход которого соединен с вторым информационным входом сумматора-вычитателя, выход которого является вторым информационным выходом ячейки, второй управляющий вход которой соединен с входом режима третьего сумматора, входы первого и второго слагаемого которого являются третьим и четвертым информационными входами ячейки, о т л и ч а ю щ а яс я тем, что, с.целью повышения однородности структуры матричных процессов и расширения функциональных возможностей за счет вычисления полиномов производных степеней, выход третьего сумматора соединен с входом второго слагаемого первого сумматора,. второй информационный вход ячейки соединен с входом второго слагаемого второго сумматора, первый и вто« рой управляющие входы ячейки соединены с входами режима первого и второ- го сумматоров соответственно.

1532919

Р(х)

Составитель Н.Матвеев

Редактор Л.Пчолинская Техред Л Олийнык Корректор Л.Бескид

Заказ 8100/53 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r, Ужгород, ул. Гагарина, 101