Устройство для операций с комплексными числами

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и позволяет вычислить произведение комплексных чисел A и B, описываемых тремя составляющими A<SB POS="POST">1</SB>, A<SB POS="POST">2</SB>, A<SB POS="POST">3</SB> и B<SB POS="POST">1</SB>, B<SB POS="POST">2</SB>, B<SB POS="POST">3</SB> соответственно. Результат умножения C также описывается тремя составляющими C<SB POS="POST">1</SB>, C<SB POS="POST">2</SB>, C<SB POS="POST">3</SB> : C<SB POS="POST">1</SB> = A<SB POS="POST">1</SB>B<SB POS="POST">1</SB>+A<SB POS="POST">2</SB>B<SB POS="POST">3</SB>+A<SB POS="POST">3</SB>B<SB POS="POST">2</SB>, C<SB POS="POST">2</SB> = A<SB POS="POST">1</SB>B<SB POS="POST">2</SB>+A<SB POS="POST">2</SB>B<SB POS="POST">1</SB>+A<SB POS="POST">3</SB>B<SB POS="POST">3</SB>, C<SB POS="POST">3</SB> = A<SB POS="POST">1</SB>B<SB POS="POST">3</SB>+A<SB POS="POST">2</SB>B<SB POS="POST">2</SB>+A<SB POS="POST">3</SB>B<SB POS="POST">1</SB>. Устройство содержит элементы задержки 1.1 - 1.3, 2.1 - 2.3, коммутаторы 3.1 - 3.3, которые обеспечивают изменение порядка поступления операндов на умножители 4.1 - 4.3, которые вычисляют слагаемые составляющих результата, элементы задержки 5.1 - 5.3 и 6.1 - 6.3, выравнивающие моменты поступления произведений, являющихся слагаемыми составляющих результата, сумматоры 7.1 - 7.3, 9.1 - 9.3, которые определяют составляющие результата. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н.ABTOPCKOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4622302/24 (22) 19.12.88 (46) 30.12.90. Бюл. М 48 (71) Специальное проектно-конструк.торское бюро "Дискрет" Одесского политехнического института (72) Ю.А. Богомолов, А.R.Äðoçä, В.Н.Лацин, В.А.Минченко и В.В.Шабадаш (53) 681.32(088„8) (56) Каляев A .Â.Ìíîãoïðoöåññoðíûå системы с программируемой архитектурой.—

M. Радио и связь, 1984, с,178.

Авторское свидетельство СССР

У 399859, кл. G 06 F 7/38, 1971. (54) УСТРОЙСТВО ДЛЯ ОПЕРАЦИЙ С КОМПЛЕКСНЬ1МИ ЧИСЛАМИ (57) Изобретение относится к вычислительной технике и позволяет вычислить произведение комплексных чисел, 80 617436 А1 (51) 5 G 06 F 7/49

А и В, описываемых тремя составляющими а, а, а з и Ь!, bz b соответственно. Результат умножения с также описывается тремя составляющими с, су, сз - с1= а,Ь + а Ьg+ .+ азЬ, cz = а,Ъ + а Ь, + а Ьз, с з = а,Ь + а Ь + а Ь,. Устройство содержит элементы задержки 1.1

1, Э, 2, 1-2. 3 коммутаторы 3. 1-3. 3, которые обеспечивают изменение порядка поступления операндов на умножители 4.1-4.3, которые вычисляют слагаемые составляющих результата, элементы задержки 5.1-5.3 и

6.1-6.3, выравнивающие моменты поступления произведений, являющихся слагаемыми составляющих результата, сумматоры 7. 1-7.3, 9. 1-9.3, которые определяют составляющие результата.

1 ил., 1 табл.

1617436

Составляющие результат 2к > !4и!3

С=АВ= с+се +се"

I вычисляются по формулам: а1b, + а2Ь + а Ь2, с, с2 = с>

+ а Ь, а,Ь,+ а Ь, a+ а Ь2 + а Ь

Изобретение относится к автомати- и вычислительнгй технике и может быть использовано в арифметических устройствах специализированных 38M.

Цель изобретения — расширение области применения устройства за счет выполнения операции умножения комплек HbIx чисел, представленных в трехфазной Форме.

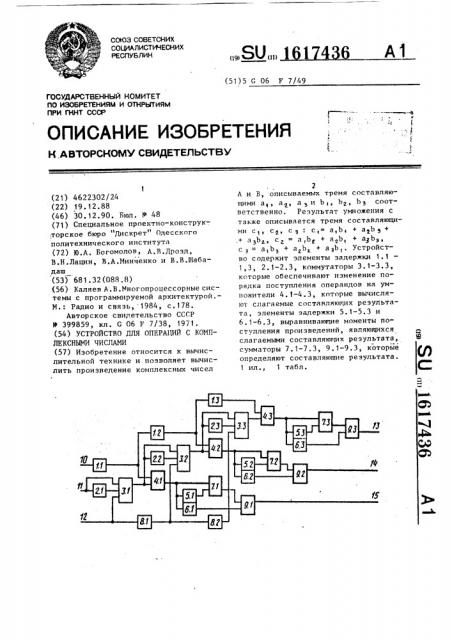

На чертеже представлена структурная с-.хема устройства.

У<:тройство содержит первый — третий 1.1 — 1.3 и четвертый — шестой

2.1 — 2.3 элементы задержки, первый — третий коммутаторы 3 ° 1 — 3.3, первый — третий умножители 4,1 — 4 .3, седьмой — девятый 5.1 — 5.2 и десятый — двенадцатый 6.1 — 6.3 элементы задержки, четвертый — шестой сумматоры 7.1 — 7.3, тринадцатый 8.1 и .четырнадцатый 8.2 элементы задержки, первый — третий сумматоры 9.1 — 9.3, первый 10 и второй 11 информационные входы устройства, вход 12 управления устройства, третий 13, второй 14 и первый 15 выходы устройства.

Работа устройства синхронизируется тактовьм генератором (не показан).

Элементы 6.1 — 6.3 задерживают информацию на два такта, элементы

2.1 — 2.3 — на три такта, остальные элементы задержки — на один такт.

При составлении таблицы, отражаю-, щей ход вычислений в предлагаемом устройстве принято, что задержки срабатывания коммутатора и получения произведения на выходе умножителя равны нулю; нижний индекс числа обозначает номер составляющей сомножителя, а верхний — порядковый номер сомножителя.

Устройство выполняет умножение комплексных чисел, представленных в трехфазной форме: ди(3 i 4н)3

А = а + а е1 + а е" (2 з 1

12к! 40JS

B = b + b2e + b e1

Это соотношение положено в основу работы устройства.

Устройство работает следующим образом.

На первый и второй информационные входы устройства поступают последовательно составляющие нулевой пары сомножителей (a, а, а,) и (Ь,, b2, Ьз), затем первой (а а У 2 Ф а, и Ь,, Ь b )è т.д.

На первый вход умножителя поступает задержанная на один такт последовательность составляющих первого

15 сомножителя, а на второй — последовательность сост являющих второго со множителя, в которой при помощи коммутатора произведена перестановка данных, поэтому »а выходе первого умножителя в моменты времени 1, 4, 7, ЗК+1 (К = О, 1,...) получается произведение а Ь2, в моменты времек к ни 2, 5, 8,..., ЗК + 2 — произведек к, ние а Ь, в моменты времени 3, 6, 9,..., ЗК + 3-произведение à, b1 кок к торые являются слагаемыми первой составляющей результата. Перед сложением этих произведений необходимо произвести выравнивание моментов их

30 поступления на сумматоры для чего служат элементы 5.1-и 6.1 задержки..

Аналогично происходят вычисления второй и третьей составляющих результата.

Формула изобретения

Устройство для операций с комплексными числами, содержащее первый и второй сумматоры, выходы которых являются соответственно первым и вторым выходами устройства, о т л и— ч а ю щ е е с я тем, что, с целью расширения области применения уст4 ройства за счет умножения комплексных чисел, представленных в трехфаэной форме, в устройство введены четыре сумматора, три умножителя, три коммутатора и четырнадцать элементов задержки, причем выход третьего сумматора является третьим выходом устройства, первый информационный вход которого подключен к входу первого элемента задержки, выход которого подключен к первому входу первого

55 умножителя и входу второго элемента задержки, выход которого подключен к первому входу второго умножителя и входу третьего элемента задержки, Тактг Э

Умновитель илн Вход/выход коммутатор

0 1 2 Э 4 5 6 7 8 9

1 1 < 1 1 г а> аг а, а! аг а, e o аэ аг ао

Умновитель Вход первого сомн.

Вход второго сомн. о < < г г г

bt Ь, Ьг Ь Ь, Ь Ь

Ь, be

1 0

0 1

1 1 0 1

Управление коммутатором

Второй вход

Первый вход

Второй вход

Выход

Управление коммутатором

Второй вход

Первый вход

Второй вход

Выход

Управление коммутатором

Второй вход

Первый вход

Второй вход

Выход о

Ьэ

1 а2 ь

< агьэ ь

1 а .1

Ь, a Ь

1 ь а ь

atÔbt ! 1

bi ао1

b4 р а,b ьэ аг ь, at Ь2 г % р ьг

< аэ ь ! а Ь

i ьг

bk г аэ

3.1 р а аг

ЬУ аэьг а,Ьэ

4.1

1 1 ь ь, аа аг аг ь1 ьг э агЬг a bt э 2 i

0 1

Ьг а, 1

be а,Ьг

1

bei

i аг ь, ait bI

Ьг ар

Ьг р о а, Ь.г

ЬЗ аэ

ЬЗ

a3b3

1 1

3.2. о аг ь, о агь, 1 о аг ьэ о о аэьэ

4.2 ь, ь, 1 1

Ф г а, а ь, ьг а,Ьэ а Ь!

Э ь, ао

i ь

a, Ьэ

i аа ь, 4 аь, о

Ь2 ад

b, 1 агъг

3.3 о

Ь3

aob0 р ао

b> аг Ьг

4.3

5 161743 выход которого подключен к первому входу третьего умножителя, выход которого подключен к первому входу шестого сумматора и входам девятого и двенадцатого элементов задержки, выходы которых подключены соответственно к второму входу шестого сумматора и первому входу третьего сумматора, второй вход которого подключен к выходу шестого сумматора, второй информационный вход устройства подключен к первому информационному входу первого коммутатора и входу четвертого элемента задержки, выход которого подключен к второму информационному входу первого коммутатора, выход которого подключен к второму входу первого умножителя, первому информационному входу второго комму- 29 татора и входу пятого элемента задержки, выход которого подключен к второму информационному входу второго коммутатора, выход которого подключен к второму входу второго умножите- g5 ля, первому информационному входу третьего коммутатора и входу шестого элемента задержки, выход которого подключен к второму информационному вхо6 6 ду третьего коммутатора, выход которого подключен к второму входу третьего умножителя, выход первого умножителя подключен к первому входу четвертого сумматора и входам седьмого и десятого элементов задержки, выходы которых подключены соответственно к второму входу четвертого сумматора и первому входу первого сумматора, второй вход которого подклЮчен к выходу четвертого сумматора, выход второго умножителя подключен к первому входу пятого сумматора и входам восьмого и одиннадцатого элеменI тов задержки, выходы которых подключены к второму входу пятого сумматора и первому входу второго сумматора, второй вход которого подключен к выходу пятого сумматора, вход управления устройства подключен к управляющему зходу первого коммутатора и входу тринадцатого элемента задержки, выход которого подключен к управляющему входу второго коммутатора и входу четырнадцатого элемента задержки, выход

I которого подключен к управляющему входу третьего коммутатора °