Матричный накопитель для постоянного запоминающего устройства

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в постоянном технологически программируемом запоминающем устройстве на МДП-транзнсторах. Целью изобретения является упрощение и сокращение длительности изготовления матричного накопителя для ПЗУ. Поставленная цель достигается размещением в приповерхностном слое полупроводниковой подложки 1 под вторым диэлектрическим слоем 4 и одним краем адресной поликремниевой тины Ъ третьего диффузионного слоя 9 первого типа проводимости. Наличие слоя 9 уменьшает эффективную ширину канала запоминающего транзистора. Транзисторы с разной шириной канала соответствуют различной информации, хранимой накопителем. В результате один элемент памяти может хранить два или четыре бита информации. 1 з.п. ф-лы. 17 ил. § (Л

СВОЗ СО ЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„.,SU„„ I669Ä07 А1 (51) 5 С 11 С 17/00

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

„. (46) 23.09.92. Вюл. Н 35 (21) 4741288/24 (22) 1 07.89 (71) Нау но-исследовательский институт "Восток" (72) В.И.Овчаренко, В.П.Серебрянникова, В,Г.штыров и М.A.Ïoðòíÿãèí (53) 68 1.327.66 (088.8) (56) Патент США Р 423Р504, кл. G 11 С 11/40,. 1980.

Электроника, Р 6, 1983, с, 48"51. изобретения является упрощение и сокращение длительности изготовления матричного накопителя для ПЗУ. Поставленная цель достигается размещением в приповерхностном слое полупроводниковой подложки 1 под вторым диэлектрическим слоем 4 и одним краем адресной поликремниевой шины 5 третьего диффузионного слоя 9 первого типа проводимости. Наличие слоя 9 уменьшает эффективную ширину канала запоминающего транзистора. Транзисторы с разной шириной канала соответствуют различной информации, хранимой накопителем . В результате один элемент памяти может хранить два ини че тыре бита информации. 1 э.п. ф-лы.

17 ил. (54) ИАТРИЧНЬЙ НАЕОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОИИНАКЦЕГО УСТРОЙСТВА (57) Изобретение относится к области вычислительной техники и может быть использовано в постоянном технологически программируемом запоминающем устройстве на ИДП-транзисторах. Целью

=-Г

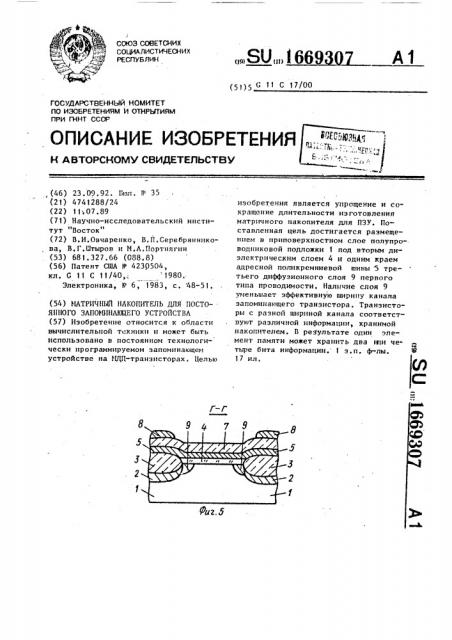

Риг. 5

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1669307

Третий диффузионный слой 9 предот™ вращает образование инверсного слоя под адресными шинами 5.

Длина канала МДП-транзисторов определяется зазором ие:кду вторым диффузионным слоем 6 под адресной шиной

Изобретение относится к оГ>пасти вычислптельной техники и мокет быть использовано в постоянном запоминающем устройстве на МДП-транзисторах, программируемых технологически, Целью изобретения является упроще" ние накопителя.

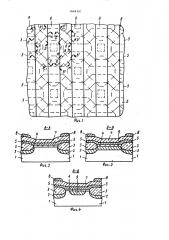

На фиг. 1 приведен фрагмент матричного накопителя, на фиг.2-8 - сечения 10 по А-А, Б-Б, В-В, Г-Г, Д-Д, Е"F. Ж-Ж соответственно для элементов памяти, находящихся в одном иэ четырех устойчивых состояний, на фиг.9 приведены вольт-амперные характеристики двух5 битных элементов памяти матричного накопителя, на фиг. 10-17 - сечения и вольт-амперные характеристики четырехбитных элементов матричйого йако пителя.

Матричньй.накопитель содеркит полупроводниковую подлошку 1 первого» типа проводимости с углублениями в ней, первый диффузионный слой 2 пер" вого типа проводнмости, первый.диэлектрический слой 3 йз двуокиси кремния, второй диэлектрический слой

4 из двуокиси кремния, адресные шины

5 иэ поликремния, второй диффузионный слой 6 второго типе проводимости, тре тий диэлектрический слой 7 из фосфорб-силикатного стекла, разрядные шины 8 иэ металла, третий диффузионный слой 9 первого типа проводимости.

В местах пересечения адресных шия

5 и разрядных шин 8 образОваны двух-, Ьитиые элементы памяти матричного накопителя (фиг.1).

Адресные шины 5 являются затворами

Щ(П-транзисторов элементов памяти этого матричного накопителя, програм- 40 мируемых технологически, второй диэлектрический слой 4 - их подзатворным диэлектриком.

Второй диффузионный слой 6 являет ся стоками и истоками МДП-транзисто- 45 ров, первый диффузионный слой 2 - ан типараэитньи. Первый диэлектрический слой 3 изолирует адресные шины 5 от полупроводниковой подлокки 1, третий диэлектрический слой 7 изолирует раэ- 50 рядные шины 8 от адресных шин 5.

5, зазор пропорционален ширине адресной шины 5.

Зазор в первом диффузионном слое

2 под адресной шиной 5 определяет ширину канала HfgI-транзистора двухбитного элемента памяти с состояниями

"f,1" (отсутствие перекрытия этого зазора третьим диффузионным слоем 9).

Полное перекрытие третьим диффузионным слоем Э зазора мекду первыч диффузиснным слоем 2 под адресной шиной 5 предотвращает образование инверсного слоя под адресной шиной

5 (при низком считывающем напряь пии), Что эквивалентно нулевой ширине канала, определяющей состояния

0,0 двухбитного элемента памяти.

Перекрытие третьим диффузионньи слоем 9 1О-ЗОХ или 40-70Z зазора в первом диффузионном слое 2 под адресной шиной 5 позволяет уменьшить относительное.значение эффективной ширины канала на 0,1-0,3 и 0,4-0,7 соответственно для элементов памяти с состояниями "1,0" и "0,1".

Таким образом, для двухбитных эле ментов памятй с состояниями 1,1 1;

"1,О"; "0, 1"; "0,0" получены следующие соотношения проводимостей каналов относмтельно нелегированного элемента памяти с состояниями "1.,t" с максимальной проводимостью: t,О, 0,7"

0,9) 0,3-0,6, О.

Работа матричного накопителя заключается в следующем.

В режиме..считывания информации на выбранную поликремниевую адресную цв1" ну 5 подают низкое полокительное напряжение (3-5 В), на остальные адресные шины 5 - нулевое напряжение. На выбранные металлические разрядные ши- ны 8, к которым подключены истоки

МДП-транзисторов, в которых, размещен или отсутствует третий диффузионный слой 9 подают нулевое напряпение, на остальные разрядные шины 8 — низкое положительное напряжение.

В зависимости от перекрытия зазора третьим диффузионным слоем 9 uepes выбранный элемент памяти протека6т ток 10.-12 (фиг.9) или не протекает ток 13. Такая величийа тока регистрируется усилителем считывания как соответствующие состояния "1,1", "1,0", 0, 1",. "0,0" двухбитного элемента памяти.

1 1

Через выбранные разрядные тины ток от остальных элементов памяти не проб9307 г

5

16 текает иэ-за нулевого напряже ня на адресных шинах 5, в результате ч го

ИДИ-транзисторы находятся I! 3BKpblToH состоянии

Для увеличения информационной емкости я дна раза матричный накопитель может быть выполнен на четь.рехбитных элементах памяти вместо двухбитных.

Для этого третий диффузионный слой 9 с соответствующими перекрытиями зазора между первым диффузионным слоем 2 под поликремниевой адресной шиной 5 размещен с раэньм сторон поликремниевой адресной шины 5 с большим перекрытием, чем вторым диффузионным слоем Ь.

При считывании информации из таких элементов памяти величина тока определяется зазором третьего диффузионного слоя 9, находящегося в истоке выбранного ИДП"транзистора. Поэтому первые два бита информации считываются при прямом включении элемента памяти, другие два бита - в инверсном включении этого же элемента памяти.

Формула изобретения

1. Матричный накопитель для постоянного запоминающего устройства, содержащий полупроводниковую подложку первого типа проводимости, в которой выполнены углубления, первый диэлектрический слой из двуокиси кремния, расположенный в углублениях в полупроводниковой подложке, первый диффузионный слой первого типа проводимости, расположенный в приповерхностном слое полупроводниковой подложки под первым диэлектрическим слоем, второй диэлектрический слой иэ двуокиси кремния, расположенный на поверхности полупроводниковой подложки, адресные шины иэ поликремния, расйоложенные

40 на поверхности первого н нтс р,лго диэлектрических слоев, второй диффузионный слой второго типа проводимосTll расположенный в приповерхностном слое полупроводниковой подложки под вторым диэлектрическим слоем с частичным перекрытием краев адресных шин, третий диэлектрический слой иэ фосфоросиликатного стекла, расположенный на поверхностях первого и второго диэлектрических слоев и адресных шин, во втором и третьем диэлектрических слоях над вторым диффуэионньм слоем второго типа проводимости выполнены отверстия, разрядные шины иэ металла, расположенные на поверхности третьего диэлектрического слоя и на поверхности полупроводниковой подложки в отверстиях во втором и третьем диэлектрических слоях, о тл и ч а ю шийся тем, что, с целью упрощения накопителя, он содержит третий диффузионный слой первого типа проводимости, расположенный в приповерхностном слое полупроводниковой подложки с примыканием к краю второго диффузионного слоя со стороны первых краев адресных шин с перекрытием 10-30Х, 40-707, илн 1003 расстояния между соседними углублениями в полупроводниковой подложке в соответствии с хранимой информацией.

2. Накопитель по п.1, о т л и— чающий с я тем, что, с целью увеличения информационной емкости, третий диффузионный слой расположен с примыканием к краю второго диффузионного слоя со стороны вторых краев адресных шин с перекрытием 10-303, 40-70Х или 100Х расстояния между соседними углублениями в полупроводниковой подложке в соответствии с хранимой информацией.

166) 9307

Фиг,1

А-4

3

Фиг,2

A-Л

Я .б

Ж-Ж

Фиъ, В

Я-Я

s - К г

В -д в в

2

1 д

3

Фиг. 1Ю

Фиъ. 12

1669301

Я

5 S

2 2

1 1

Е-Е

9 у

oui. 7

Vg

Фиг.Я

ФИ2. 11

Г -/

Рих. O

1669307

А-А

16 0

Фиь. t7

Составитель Л.Лмусьева

Редактор И.Шубина Текред Л,Сердюкова Корректор Jl. Ïèëèïåíêî

Заказ 40бО Тираж Подписное

ВНИИПИ Государстненного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, Ж"35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 101