Устройство для сложения четырех чисел в последовательном коде

Иллюстрации

Показать всеРеферат

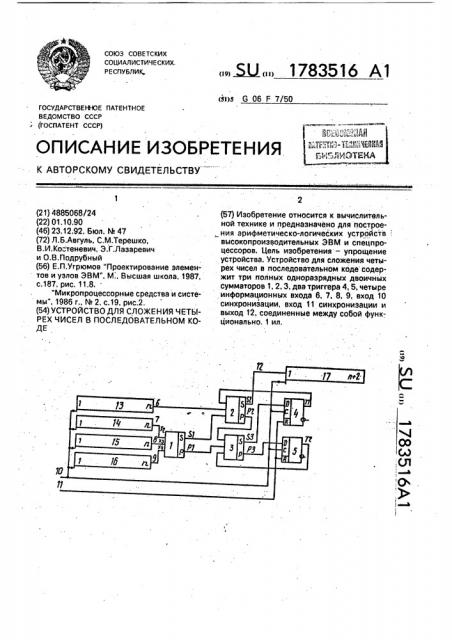

Изобретение относится к вычислительной технике и предназначено для построе- .ния арифметическо-логических устройств высокопроизводительных ЭВМ и спецпроцессоров . Цель изобретения - упрощение устройства. Устройство для сложения четырех чисел в последовательном коде содержит три полных одноразрядных двоичных сумматоров 1,2,3, два триггера 4,5, четыре информационных входа 6, 7, 8, 9, вход 10 синхронизации, вход 11 синхронизации и выход 12. соединенные между собой функционально . 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ.

РЕСПУБЛИК„ (я)э G 06 F 7/50

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

00 (л) :(Л аЪ

t c

1 (21) 4885068/24 (22) 01.10.90 (46) 23,12.92. Бюл. Q 47 (72) Л.Б.Авгуль, С.М.Терешко, В,И.Ко" теневич, Э.Г.Лазаревич и О.В.Подрубный (56) Е.П.Угрюмов "Проектирование элементов и узлов ЭВМ", M.. Высшая школа, 1987, с.187, рис. 11,8.

"Микропроцессорные средства и системы", 1986 r., М 2, с.19, рис.2. (54) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ЧЕТЫРЕХ ЧИСЕЛ В ПОСЛЕДОВАТЕЛЬНОМ КОДЕ

«Ы2,, 1783516 А1 (57) Изобретение относится к вычислительной технике и предназначено для построения арифметическо-логических устройств высокопроизводительных ЭВМ и спецпроцессоров. Цель изобретения — упрощение . устройства, Устройство для сложения четырех чисел в последовательном коде содержит три полных одноразрядных двоичных сумматоров 1, 2, 3, два триггера 4, 5, четыре информационных входа 6, 7, 8, 9, вход 10 синхронизации, вход 11 синхронизации и выход 12. соединенные между собой функционально. 1 ил.

1783516

Изобретение относится к вычислительной технике и предназначено для построения арифметико-логических устройств высокопроизводительных ЭВМ и спецпроцессоров.

Известен сумматор последовательного действия, содержащий комбинационный одноразрядный двоичный сумматор и триг гер для запоминания переноса(1).

Недостатком сумматора являются низкие фрикционные возможности, поскольку он не обеспечивает одновременное сложение трех и более операндов.

Наиболее близким по функциональным воэможностям и конструкции техническим решением к предлагаемому является устройство для сложения N чисел, представленных в последовательном коде, которое содержит дерево одноразрядных двоичных сумматоров с триггерами для запоминания переносов(2).

Недостатком известного устройства является. высокая конструктивная сложность, Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что в устройстве для сложения четырех чисел в последовательном коде, содержащем два триггера и три одноразрядных двоичных сумматора, 1-й (i = 1, 2);.вход первого из которых соединен с i-м информационным входом устройства, третий информационный вход которого соединен с первым входом второго одноразрядного сумматора, второй вход которого соединен с выходом

hep8oro триггера, вход синхронизации которого соединен с входом синхронизации второго триггера и входом синхронизации устройства, вход начальной установки которого соединен с входом обнуления первого триггера и входом обнуления второго триггера, выход которого соединен с первым входом третьего одноразрядного двоичного сумматора, выход переноса которого соединен с информационным входом второго триггера, четвертый информационный вход устройства соединен с третьим входом первого одноразрядного двоичного сумматора, выход суммы которого соединен с третьим входом второго одноразрядного двоичного сумматора, выход переноса соединен со вторым входом третьего одноразрядного двоичного сумматора, выход суммы которого соединен с информационным входом первого триггера, а третий вход соединен с выходом переноса второго однораЗрядного двоичного сумматора, выход суммы которого соединен с выходом устройства. синхронизации устройства соединен с синхровходами триггеров 4 и 5. Вход 11 начальной установки устройства соединен с входами обнуления триггеров 4 и 5.

35 В заявляемом устройстве для хранения переносов используются синхронные двухступенчатые триггеры с входом обнуления, например D- u lK-триггеры.

Устройство для сложения четырех чисел

40 в последовательном коде работает следующим образом. ka вход 11 начальной установки подается импульс, обнуляющий триггеры 4 и 5. К этому времени регистры 13, 14, 15 и 16 загружены двоичными и-разрядными числами Х1, Х2, Хэ и Х4 соответственно, которые участвуют в сложении. Причем в первых разрядах хранятся старшие разряды, в и-x младшие разряды операндов X> Х4. Затем на вход 10 синхронизации подает50 ся серия иэ (и+2) тактовых импульсов, по заднему фронту которых осуществляется синхронный сдвиг информации в регистрах

13-17. После окончания (и+2)-ro импульса в регистре 17 оказывается результат $ = Х1 +

55 Х2 + Хз+ Х4.

Формула изобретения

Устройство для сложения четырех чисел в последовательном коде, содержащее первый и второй триггеры и первый, второй и третий полные одноразрядные двоичные

На чертеже представлена схема предлагаемого устройства для сложения четырех чисел в последовательном коде.

Устройство содержит двоичные сумматоры 1, 2 и 3, триггеры 4 и 5, информационные входы 6, 7, 8 и 9, вход 10 синхронизации, вход 11 начальной установки, выход 12. Кроме того на чертеже показаны не входящие в состав предлагаемого устройства, но обеспечивающие его работу сдвигающие и-разрядные регистры 13, 14, 15 и 16 для хранения и-разрядных операндов, участвующие в сложении и сдвигающий (и+2)-разрядн ый регистр результата.

Информационные входы устройства 7, 8 и 9 соединены с входами сумматора 1. Информационный вход 6 соединен с первым входом сумматора 2, вход переноса которого соединен с выходом первого триггера 4, второй вход сумматора 2 соединен с выходом суммы сумматора 1. Выход триггера 5 соединен с первым входом сумматора 3, второй вход которого соединен с выходом переноса первого сумматора 1, вход переноса сумматора 3 соединен с выходом переноса сумматора 2, выход суммы которого соединен с выходом 12 устройства. Выходы суммы и переноса сумматора 3 соединены соответственно с информационными входами первого и второго триггеров 4, 5. Вход 10

1783516

Составитель 8.Гусев

Техред M.Ìoðãåíòàë Корректор H.Áó÷åê

Редактор

Заказ 4516 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 сумматоры, причем первый и второй входы полного одноразрядного двоичного сумматора соединены соответственно с первым и вторым информационными входами устройства, третий информационный вход которого соединен с первым входом второго полного одноразрядного двоичного сумматора, вход переноса которого соединен с прямым выходом первого триггера, вход синхронизации которого соединен с входом синхронизации второго триггера и входом синхронизации устройства, вход начальной установки которого соединен с входами установки в "0" первого и второго триггеров, прямой выход второго триггера соединен с первым входом третьего полного одноразрядного двоичного сумматора, выход переноса которого соединен с информационным входом второго триггера. о т л и ч а ю щ е ес я тем, что, с целью упрощения устройства, его четвертый информационный вход соединен с входом переноса первого полного од5 норазрядного двоичного сумматора, выход суммы которого соединей с вторым входом второго полного одноразрядного двоичного сумматора, выход переноса первого полного одноразрядного сумматора соединен с

10 вторым входом третьего полного одноразрядного двоичного сумматора, выход суммы которого соединен с информационным входом первого триггера, вход переноса третьего полного одноразрядного двоичного

15 сумматора соединен с выходом переноса второго полного одноразрядного двоичного сумматора, выход суммы которого является выходом устройства.