Устройство памяти и способ изготовления

Иллюстрации

Показать всеИзобретение относится к области электрически записываемых и стираемых энергонезависимых флэш-ЗУ. Сущность изобретения: устройство памяти выполнено из запоминающих ячеек с запоминающим транзистором, в котором на верхней стороне полупроводниковой подложки между областями истока и стока расположен электрод затвора, отделенный от полупроводникового материала диэлектриком, имеющим запоминающий слой между ограничительными слоями. Электрод затвора расположен в канавке, выполненной в полупроводниковом материале между областью истока и областью стока, а запоминающий слой расположен по меньшей мере между областью истока и электродом затвора и между областью стока и электродом затвора. Каждый из электродов затворов находится в электропроводящем соединении с предусмотренной в качестве шины слов проводящей дорожкой. Область истока и область стока одной запоминающей ячейки одновременно служат в качестве соответственно области стока и области истока соседней запоминающей ячейки. Шины слов проходят поперек канавок. Техническим результатом изобретения является создание устройства памяти из запоминающих ячеек с предельно малой потребностью в площади. 2 н. и 9 з.п. ф-лы, 13 ил.

Реферат

Изобретение относится к области электрически записываемых и стираемых энергонезависимых флэш-ЗУ. Оно описывает выполненную по схеме SONOS (Semiconductor-Oxide-Nitride-Oxide-Semi-conductor) энергонезависимую запоминающую ячейку, которая может быть использована в виртуальной базовой архитектуре ИЛИ НЕ.

Мельчайшие энергонезависимые запоминающие ячейки необходимы для максимальной плотности упаковки при мультимедийном применении. Дальнейшее развитие полупроводниковой техники обеспечивает все более возрастающую емкость памяти, которая очень скоро достигнет гигабитового диапазона. В то время как, однако, определяемая литографией минимальная величина структуры продолжает уменьшаться, другие параметры, например толщина туннельного оксида, не могут быть соответственно масштабированы. Уменьшение длины канала, сопровождающее в планарных транзисторах уменьшение структуры, требует увеличения легирования канала во избежание возникновения называемого как "Punch-through" пробоя напряжения между истоком и стоком. Это приводит к повышению пускового напряжения, которое обычно компенсируется уменьшением плотности толщины подзатворного оксида.

Программируемые канальными горячими электронами, стираемые горячими дырками планарные запоминающие ячейки SONOS (см. US 5768192, US 6011725, WO 99/60631) требуют, однако, управляющего диэлектрика равноценной подзатворному оксиду толщины. Эту толщину нельзя, однако, произвольно уменьшить, не уменьшая недопустимым образом числа выполняемых циклов программирования ("срок службы" запоминающей ячейки). Требуется поэтому достаточно большая длина канала с тем, чтобы концентрацию легирующей примеси в канале не пришлось выбирать слишком высокой, поскольку иначе пусковое напряжение слишком возрастет.

В публикации J.Tanaka et al. "A Sub-0,1-μm Grocved Gate MOSFET with High Immunity to Shot-Channel-Effects" in IEDM 93, стр. 537-540 (1993 г.) описан транзистор на подложке р+-типа, у которого электрод затвора расположен в канавке между n+-областью истока и n+-областью стока, и таким образом в подложке выполнена искривленная канальная область.

В публикации К.Nakagawa et al. "A Flash EEPROM Cell with Self-Aligned Trench Transistor & Isolation Structure" in 2000 IEEE Symposium on VLSI Technology Digest of Technical Papers описан транзистор в качестве запоминающей ячейки с электродом плавающего затвора, который расположен между n+-областью истока и n+-областью стока, доходя до кармана р-типа подложки. Между электродами плавающего и управляющего затворов находится слой диэлектрика из последовательности слоев оксид-нитрид-оксид.

В публикации К.Nakagawa et al. "A Flash EEPROM Cell with Self-Aligned Trench Transistor & Isolation Structure" in 2000 IEEE Symposium on VLSI Technology Digest of Technical Papers описан транзистор в качестве запоминающей ячейки с электродом плавающего затвора, который расположен между n+-областью истока и n+-областью стока, доходя до кармана р-типа подложки. Между электродами плавающего и управляющего затворов находится слой диэлектрика из последовательности слоев оксид-нитрид-оксид.

В DE 19545903 А1 описано устройство из постоянных запоминающих ячеек, у которого планарные МОП-транзисторы расположены проходящими параллельно рядами. Соседние ряды проходят попеременно по дну продольных канавок и между соседними продольными канавками. Разрядные шины проходят поперек продольных канавок, а шины слов - параллельно продольным канавкам.

В DE 19600422 С1 описано электрически программируемое устройство из запоминающих ячеек, у которого имеется множество запоминающих ячеек, включающих в себя каждая МОП-транзистор с подзатворным диэлектриком с ловушками и расположенных проходящими параллельно рядами. Соседние ряды проходят при этом попеременно по дну продольных канавок и между соседними продольными канавками и изолированы друг от друга.

В DE 19603810 С1 описано устройство из запоминающих ячеек, включающее в себя первые запоминающие ячейки с планарными МОП-транзисторами и вторые запоминающие ячейки с вертикальными МОП-транзисторами. Планарные МОП-транзисторы расположены при этом на дне и вершине параллельных полосообразных канавок. Вертикальные МОП-транзисторы расположены на боковых стенках канавок.

Задачей данного изобретения является создание запоминающей ячейки для устройства из запоминающих ячеек с предельно малой потребностью в площади и соответствующего способа изготовления.

Эта задача решается посредством запоминающей ячейки с признаками п.1 формулы, устройства из запоминающих ячеек с признаками п.15 формулы и способа с признаками п.21 формулы. Различные выполнения приведены в зависимых пунктах.

Запоминающая ячейка, согласно изобретению, содержит запоминающий транзистор, который на верхней стороне полупроводникового тела или полупроводникового слоя снабжен электродом затвора, расположенным между областью истока и областью стека, выполненными в полупроводниковом материале. Электрод затвора отделен от полупроводникового материала диэлектрическим материалом. По меньшей мере, между областью истока и электродом затвора и между областью стока и электродом затвора имеется последовательность слоев, которая включает себя предусмотренный для захвата носителей заряда на истоке и стоке запоминающий слой между ограничительными слоями. Материал ограничительных слоев обладает большей запрещенной энергетической зоной, чем материал запоминающего слоя, так что носители заряда, захваченные в запоминающем слое между ограничительными слоями, остаются там локализованными.

В качестве материала для запоминающего слоя рассматривается преимущественно нитрид; в качестве окружающего материала пригоден в первую очередь оксид. У запоминающей ячейки в материальной системе кремнийзапоминающий слой в этом примере представляет собой нитрид кремния с запрещенной энергетической зоной около 5 эВ, а окружающие ограничительные слои представляют собой оксид кремния с запрещенной энергетической зоной около 9 эВ. Запоминающим слоем может быть другой материал с меньшей запрещенной энергетической зоной, чем у ограничительных слоев, причем разность запрещенных энергетических зон должна быть как можно большой для хорошего электрического блокирования носителей заряда (confinement). Преимущественно в запоминающем слое предусмотрены ловушки или центры захвата, которые образуют заполняемые носителями заряда энергетические уровни в пределах запрещенной энергетической зоны запоминающего слоя.

Нижний ограничительный слой, обращенный к полупроводниковому материалу, следует выполнять настолько толстым, чтобы избежать прямого туннелирования носителей заряда.

При применении SiO2 нижний ограничительный слой имеет поэтому толщину преимущественно, по меньшей мере, 6-7 нм. Верхний ограничительный слой, обращенный к электроду затвора, обычно преимущественно приблизительно вдвое толще нижнего ограничительного слоя с тем, чтобы избежать прямого туннелирования и туннелирования по Фаулеру-Нордхайму из затвора в процессе стирания.

Последовательность из запоминающего и ограничительных слоев выполняют преимущественно небольшой, эквивалентной оксиду толщины с тем, чтобы толщина чистого оксидного слоя подразумевалась как диэлектрик для получения той же емкости. Для этой цели материалы слоев выбирают так, чтобы средняя относительная диэлектрическая проницаемость последовательности слоев составляла более 4. Это происходит преимущественно за счет того, что материал нижнего ограничительного слоя, обращенный к полупроводниковому материалу, выполняют с относительной диэлектрической проницаемостью, по меньшей мере, 3,9, что соответствует SiO2. Еще лучше выбрать относительную диэлектрическую проницаемость выше, по меньшей мере, около 7,8, поскольку этим достигается лучшее управление затвором и возможно более быстрое программирование. Электрически активная толщина подзатворного диэлектрика за счет этого уменьшается, а более тонкий нижний ограничительный слой обеспечивает более высокие скорости и/или меньшие напряжения программирования.

При этом необходимо учесть, что высота барьера между полупроводниковым материалом и запоминающим слоем должна оставаться достаточно высокой. Эта высота барьера по мере возрастания относительной диэлектрической проницаемости материала нижнего ограничительного слоя обычно уменьшается. У SiO2 на Si высота барьера около 3,1 эВ; это - расстояние Ферми-уровня электронов в кремнии от нижней кромки зоны проводимости в слое SiO2. Эта высота барьера не должна быть ниже значения 2 эВ. С другой стороны, малая высота барьера предпочтительна, поскольку скорость программирования в этом случае резко возрастает, и открывается возможность уменьшить напряжение исток/сток и тем самым снизить опасность пробоя в канале. Если это реализуется в соответствии с требованиями, то материал нижнего ограничительного слоя может также предпочтительно иметь относительную диэлектрическую проницаемость, по меньшей мере, 20.

Поскольку граница раздела между кремнием и диоксидом кремния хорошо управляется, нижний ограничительный слой из SiO2 предпочтителен. В сочетании с оксидом кремния может применяться, например, оксид тантала, силикат гафния, оксид титана (в случае стехиометрического состава ТiO2), титанат, оксид тантала (в случае стехиометрического состава Та2O5), танталат, оксид циркония (в случае стехиометрического состава ZrO2), оксид алюминия в случае стехиометрического состава Аl2O3) или кремний с собственной проводимостью (нелегированный) в качестве материала запоминающего слоя. Нитрид кремния имеет относительную диэлектрическую проницаемость около 7,9. Применение альтернативного материала с большей относительной диэлектрической проницаемостью (например, 15-18) позволяет уменьшить эквивалентную оксиду толщину предусмотренной для запоминания системы слоев и потому предпочтительно. С другой стороны, нитрид кремния может также предпочтительно применяться в качестве нижнего ограничительного слоя. Вместо чисто нитрида кремния здесь может применяться также оксинитрид кремния; при этом содержание кислорода и азота непрерывно или ступенчато может изменяться от полупроводникового материала к запоминающему слою.

Указанные материалы оксид тантала, силикат гафния, оксид титана, оксид циркония и оксид алюминия, а также оксид тантала (при стехиометрическом составе Та2О5), титанат и танталат также пригодны в качестве материалов ограничительных слоев. Особо следует выделить применение силикатов в ограничительных слоях. Предпочтительно может применяться, например, силикат гафния, здесь преимущественно без ловушек. Таким образом, достигается также непрерывно изменяющийся состав нижнего ограничительного слоя, у которого для достижения хорошей границы раздела до кремния подложки или полупроводникового тела в самом низу имеется SiO2, который вверх, т.е. в направлении запоминающего слоя, в возрастающей степени смешивается с гафнием, так что при случае достигается стехиометрический состав силиката гафния. В направлении запоминающего слоя содержание кремния в материале может уменьшаться, пока наконец на границе с запоминающим слоем не останется только HfO2. Так достигают высоты барьера между полупроводниковым материалом и запоминающим слоем, пониженной с 3,1 примерно до 2 эВ по сравнению с применением исключительно SiO2. Соответствующее непрерывное варьирование состава нижнего ограничительного слоя на основе SiО2 возможно вместо гафния также с другими химическими элементами, преимущественно металлами, в качестве добавок, например, с титаном, цирконием или лантаном. Для верхнего ограничительного слоя интерес помимо силикатов представляют, в частности, Al2О3 и Ta2O5, причем в запоминающем слое предпочтительно пригодной является комбинация с титанатом, диоксидом титана, танталатом или пятиоксидом тантала.

Последовательность из ограничительного слоя, запоминающего слоя и дополнительного ограничительного слоя может быть нанесена на всю поверхность верхней стороны полупроводникового тела, так что и на горизонтальных по отношению к этой верхней стороне участках этой поверхности и на дне заполненных электродами затворов канавок имеются участки запоминающего слоя. В качестве альтернативы запоминающий слой может быть ограничен за счет того, что включающая в себя запоминающий слой последовательность слоев присутствует соответственно на стенках имеющейся в полупроводниковом материале канавки, в которой расположены соответствующие электроды затворов, а в промежутках прервана.

Запоминающие ячейки, согласно изобретению, могут быть в качестве устройства из запоминающих ячеек соединены в виртуальной базовой архитектуре ИЛИ НЕ, причем может быть реализована свободно выбираемая в широких пределах длина канала. Это достигается за счет выполнения канавок в полупроводниковом теле. Канавки могут быть вытравлены, например, в уже предварительно образованной n+-области, так что канальные области на дне этих канавок имеют направленную к полупроводниковому телу кривизну или по сравнению с областями истока и стока проходят глубже. Преимущества этого устройства заключаются, в частности, в возможности нагружения таким образом минимальной поверхности в плоскости верхней стороны полупроводникового тела (cross point cell), причем поверхность с литографически достигаемой тонкостью структуры усаживается (это касается критерия "shrinkability"). Кроме того, длину канала запоминающих транзисторов можно оптимизировать за счет глубины канавок и формы дна канавок. Возможны низкие пусковые напряжения менее 1 В и более высокие напряжения исток/сток, чем у планарных транзисторов такого же масштаба (design rule).

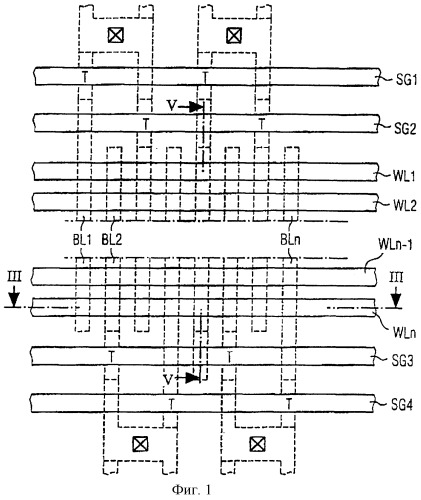

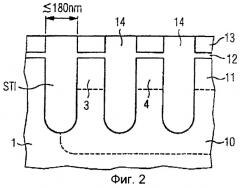

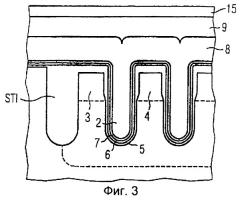

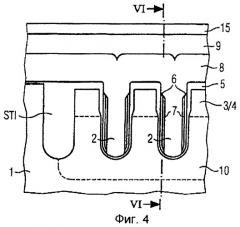

Ниже с помощью фиг.1-13 следует более подробное описание примеров запоминающих ячеек, согласно изобретению, и способа изготовления. Фиг.1 показывает устройство из запоминающих ячеек при виде сверху. Фиг.2 и 3 показывают отмеченное на фиг.1 сечение после различных этапов изготовления. Фиг.4 показывает альтернативное выполнение в сечении из фиг.3. Фиг.5 и 6 показывают формы выполнения из фиг.3 и 4 в отмеченных на фиг.1 и 4 сечениях. Фиг.7 показывает другой пример выполнения в сечении из фиг.3. Фиг.8 и 9 показывают сечения из фиг.5 и 3 для другой формы выполнения. Фиг.10, 12 и 13 показывают виды сверху, а фиг.11 показывает сечение для пояснения альтернативного способа изготовления.

На фиг.1 изображена типичная топология предусмотренного в качестве памяти расположения запоминающих ячеек при cxeматичном виде сверху. В области, занимаемой утопленными разрядными шинами BL1, BL2,...,DLn и шинами WL1, WL2,...,WLn слов, расположенными над ними в большей близости к поверхности содержащего эту память чипа, находится предусмотренная в качестве памяти последовательность слоев, которая в описанных ниже примерах для упрощенного обозначения принимается как последовательность слоев оксид-нитрид-оксид или ОНО-структура. Эта ОНО-структура может быть прервана между разрядными шинами и шинами слов или иметь место на всей поверхности. На периферии памяти расположены управляющие элементы, которые включают в себя преимущественно выполненную по КМОП-технологии схемную логику для адресации памяти. Для выбора разрядных шин, которые ведут к областям истока и областям стока отдельных запоминающих ячеек, в этом примере имеются селективные транзисторы Т. Электроды затворов селективных транзисторов, например, для двоичной адресации поблочно соединены с шинами SG1, SG2,...,SGn селективных затворов. Такая архитектура памяти сама по себе известна.

На фиг.2 в сечении изображен первый промежуточный продукт предпочтительного способа изготовления для примера фрагмента памяти. Изготовление осуществляется преимущественно в рамках КМОП-процесса, с помощью которого изготовляют и управляющую электронику. При этом принято верхнюю сторону полупроводникового тела или наращенного на подложку полупроводникового слоя покрывать сначала оксидом 12 и нитридом 13 контактных площадок. С применением подходящей техники масок вытравливают предусмотренные для памяти и STI-изоляции (shallow trench isolation) канавки преимущественно минимальной ширины (расстояние между областями истока и стока одной и той же запоминающей ячейки самое большее 180 нм) и заполняют диэлектрическим материалом, например оксидом.

Карманы р-тила и n-типа в соответствии с известным сам по себе КМОП-процессом выполняют за счет имплантации легирующей примеси в полупроводниковый материал. В зоне памяти изготовляют преимущественно карман р-типа 10. Тройной карман (triple well) с тремя расположенными друг в друге областями переменного знака электрической проводимости изготовляют для тех транзисторов, через которые шины слов памяти должны соединяться с отрицательным потенциалом с тем, чтобы методом горячих дырок (НH) с отрицательным потенциалом затвора можно было стирать содержимое запоминающих ячеек. Разрядные шины с содержащимися в них областями 3, 4 истока и стока отдельных запоминающих транзисторов изготовляют за счет дополнительной имплантации 11, в этом примере для проводимости n-типа. Область 4 стока действует каждый раз как область истока для последовательно граничащего транзистора. С помощью упомянутого выше способа программирования канальными горячими электронами (СНЕ) каждая запоминающая ячейка может хранить над областями истока и стока один бит информации, для чего при программировании исток и сток в принципиально симметричной структуре транзисторов меняются ролями.

СНЕ-программирование и НН-стирание требуют жесткого перехода между проводимостями истока или стока и карманом. Поэтому преимущественно вместе с имплантацией легирующих примесей для истока и стока (в этом примере для проводимости n+-типа) легирующую примесь для электрической проводимости с противоположным знаком (в этом примере проводимость p+-типа за счет глубже проникающей имплантации вводят в граничащую с истоком или стоком долю слоя кармана (в этом примере легирование примесью р--типа) в большей концентрации.

Канавки 14, предусмотренные для электродов затворов запоминающих транзисторов, вытравливают, нитрид и оксид контактных площадок удаляют и на всю поверхность наносят ОНО-структуру. ОНО-структура представляет собой преимущественно нижний ограничительный слой 5 из оксида толщиной 2,5-8 нм (bottom oxide, полученный преимущественно термически), запоминающий слой 6 из нитрида толщиной 1-5 нм (осажденный преимущественно посредством LPCVD [low-pressure chemical vapor deposition]) и верхний ограничительный слой 7 из оксида толщиной 3-12 нм (top oxide, осажденный). Канавки заполняют электропроводящим материалом, преимущественно нанесенным на всю поверхность проводящим легированным поликремнием, для изготовления электродов 2 затворов и слоя для образующих шины WL слов проводящих дорожек 8. Изготовляют еще уменьшающий сопротивление выводов слой 9, например, из силицида вольфрама или металлического слоя из вольфрама.

На фиг.3, изображающей в виде фрагмента отмеченное на фиг.1 сечение устройства из запоминающих ячеек, обозначен еще структурированный в виде полосы маскирующий слой 15, например износоустойчивая маска из нитрида, с помощью которого структурируют электроды затворов и шины слов за счет того, что не покрытый маской поликремний удаляют, например, посредством RIE (reactive ion etching).

На фиг.4 изображено альтернативное выполнение, у которого перед нанесением слоя поликремния ОНО-структура анизотропно вытравлена до нижнего ограничительного слоя. Остатки ОНО-структуры имеются только на предусмотренных для хранения захваченных носителей заряда участках на стенках канавок. В остальном этот пример выполнения аналогичен примеру выполнения на фиг.3.

На фиг.5 в виде фрагмента изображено проходящее поперек шин слов сечение устройства из запоминающих ячеек. Форма выполнения соответствует фиг.3 с имеющейся на всей поверхности ОНО-структурой. После структурирования в виде полосы шин слов, причем ОНО-структура между шинами слов может быть удалена, по меньшей мере, частично, например, до нижнего ограничительного слоя 5, или также полностью до полупроводникового материала, изготовляют элементы-разделители 16 (spacer), являющиеся частью процесса изготовления управляющей КМОП-периферии. В случае удаления обозначенной на фиг.5 сплошной линией ОНО-структуры между шинами слов распорные элементы доходят соответственно до ограничительного слоя или полупроводникового материала. Нитридный слой 17 на всей поверхности покрывают планаризующим слоем 18, которым заполняют остаточные участки канавок между шинами слов. Перед нанесением планаризующего слоя 18 можно еще осуществить p+-имплантацию между шинами слов, с помощью которой можно улучшить изоляцию между отдельными запоминающими ячейками.

На фиг.6 изображен в соответствии с фиг.5 разрез формы выполнения на фиг.4. В указанном на фиг.4 направлении рассмотрения верхняя граница раздела нижнего ограничительного слоя 5 над областями 3, 4 истока и стока обозначена штриховой линией 50 в виде скрытого контура. Выше долей OHO-структуры, имеющихся в виде остатков наподобие распорок, имеется доля электрода 2 затвора. Нижний ограничительный слой 5 имеется на всей поверхности. Запоминающий слой 6 и верхний ограничительный слой 7 имеются только на боковых стенках канавок между электродом затвора и областями истока и стока. Граница между обозначенными поверхностями разреза этих слоев зависит от точного положения сечения, а также наклона стенок канавок и равномерности толщины слоев. Изображение на фиг.6 лишь поясняет принципиальную структуру, которая в остальном соответствует структуре на фиг.5.

На фиг.7 изображен другой пример выполнения, у которого канавки выполнены V-образными. Соответствующие выполнению на фиг.3 подробности здесь обозначены теми же ссылочными позициями. Другое предпочтительное выполнение предусматривает выполнение V-образного наклона стенок канавок только в средней части канавок, тогда как стенки канавок сбоку от областей истока и стока проходят в основном круто вертикально. За счет этого посредством анизотропного вертикального травления ОНО-структуры можно удалить все, за исключением долей, оставшихся в верхней части стенок канавок, т.е. именно между изготовляемыми электродами затворов и областями истока и стока. Улучшенная изоляция электрода затвора от полупроводникового материала в нижней части канавок может быть достигнута тогда, когда после удаления запоминающего слоя нижний ограничительный слой (bottom oxide) оксидируют до большей толщины.

На фиг.8 и 9 другая форма выполнения изображена в сечениях, проходящих поперек шин слов и параллельно шинам слов. У этого выполнения диэлектрический материал предусмотренных для электродов затворов канавок 14 удаляют только на предусмотренных для шин слов участках. Предусмотренный для шин слов поликремний помещают только в освобожденные участки канавок. Поэтому можно отказаться от повторного заполнения открытых между шинами слов канавок. Для получения планарной поверхности перед открыванием заполненных диэлектрическим материалом (преимущественно оксидом) канавок 14 на всю поверхность наносят слой 19 из диэлектрического материала (преимущественно также оксида). Полосообразная маска, закрывающая поверхность слоя 19, имеющуюся между предусмотренными для шин слов участками, позволяет вытравить полосообразные отверстия для шин слов, а именно в канавках глубоко, а между канавками плоско в слое 19. В эти отверстия осаждают слои ОНО-структуры 5/6/7.

Одно преимущество этого варианта состоит в том, что после осаждения поликремния для электродов 2 затворов и для предусмотренных для шин слов проводящих дорожек 8 канавки полностью заполнены. Поэтому уменьшающий сопротивление выводов слой 9 в рамках применяемого для компонентов управляющей схемы процесса силицирования (salicide) можно изготовить из силицида кобальта или силицида титана за счет того, что этот слой 9 сначала наносят из кобальта, который затем силицируют.

На фиг.9, кроме того, видно, что нанесенный сначала нитрид 13 контактной площадки между предусмотренными для электродов затворов канавками был оставлен над разрядными шинами (в изображенном на фиг.9 разрезе из разрядных шин видно по одной области истока и области стока). Нитрид контактной площадки, если его не удаляют перед травлением канавок, может быть еще использован в качестве маски (травильный стоп-слой) для вытравливания канавок. При изготовлении изображенного на фиг.8 и 9 примера выполнения это имеет то особое преимущество, что при применении полосообразных масок для открывания участков, предусмотренных для шин слов и электродов затворов, имеющиеся еще между канавками доли нитрида 13 контактной площадки образуют целесообразный травильный стоп-слой, так что между разрядными шинами происходит травление в глубину, а области истока и стока остаются.

Альтернативный вариант описанного способа изготовления независимо от данного выполнения собственно запоминающей среды предусматривает нанесение и структурирование шин слов только после помещения электродов затворов в отверстия канавок. Это поясняется с помощью фиг.10-13. На фиг.10 изображена верхняя сторона подложки или полупроводникового тела, например кармана 10 р-типа, с предусмотренной ориентацией разрядных шин BLn-1, BLn, BLn+1. Преимущественно на эту сторону наносят оксид и нитрид контактных площадок. В полупроводниковом материале с применением полосообразной маски вытравливают канавки и заполняют их диэлектриком 21, что осуществляют преимущественно по типу STI с оксидом.

На фиг.11 изображено отмеченное на фиг.10 сечение, в котором видны оксид 22 и нитрид 23 контактных площадок в качестве слоев между заполненными канавками. Верхнюю сторону снабжают дополнительной полосообразной маской, которая ориентирована поперек, преимущественно перпендикулярно ориентации использованной до этого полосообразной маски. С применением этой дополнительной маски изготовляют отверстия в диэлектрике 21.

Фиг.12 показывает полученное на основе этого устройство. Полосообразные части 24 дополнительной маски, изображенные здесь кусками с штриховыми краями, проходят перпендикулярно вытравленным и заполненным канавкам. На участках верхней стороны, не закрытых дополнительной маской, диэлектрик 21 заполненных канавок удаляют, так что здесь образуются отверстия 25. Диэлектрик 21 в этих отверстиях удаляют до дна канавок.

Электроды затворов и расположенные с самосовмещением с ними шины слов могут быть выполнены на следующем этапе способа, как описано выше, с применением полосообразно структурированного слоя 19 из диэлектрического материала. Можно также снабдить сначала подзатворным диэлектриком отверстия 25 на соответствующих стенках и заполнить материалом электродов затворов и лишь после этого изготовить шины слов. У этого варианта изготовления слой предусмотренного для шин слов материала (например, W, WSi, поликремний) осаждают на всей поверхности, т.е. также на помещенные в отверстия электроды затворов. Если для электродов затворов и шин слов применяют один и тот же материал, то отверстия 25 могут быть заполнены также вместе с осаждением этого материала на всей поверхности верхней стороны. С применением третьей полосообразной маски шины слов структурируют из осажденного на всей поверхности слоя. С помощью третьей маски могут быть предпочтительно структурированы также электроды затворов транзисторов, расположенных на примыкающем к полю памяти участке управляющей схемы или в других логических областях интегрированной на том же чипе схемы. Так простым образом обеспечивается контактирование шин слов в шаге матрицы, т.е. на расстоянии соседних шин друг от друга, с компонентами управляющей схемы в целях управления запоминающими транзисторами с необходимыми напряжениями. Поскольку, однако, третью полосообразную маску не обязательно изготовлять точно в соответствии с предварительно использованной маской, при помощи которой были образованы отверстия 25, может произойти так, что шины слов будут немного смещены поперек своего продольного направления относительно электродов затворов, т.е. будут расположены не с полным совмещением с электродами затворов.

На фиг.13 также изображена верхняя сторона устройства в соответствии с фиг.12, после заполнения отверстий 25 электродами 26 затворов и структурирования шин 27 слов. Шины слов здесь обозначены преувеличенно четкими так, что они смещены вбок относительно электродов 26 затворов. Поэтому шины 27 слов перекрывают квадратные здесь при виде сверху электроды 26 затворов лишь частично, а именно на скрытом участке, обозначенном штриховыми линиями.

В другом варианте способа изготовления сначала вытравливают и заполняют диэлектрическим материалом только те канавки, которые предусмотрены в качестве STI-канавок для окружающей устройство из запоминающих ячеек изоляции от управляющей периферии. Только с изготовлением легированных областей для разрядных шин, а также истока и стока в полупроводниковом материале вытравливают канавки для электродов затворов. Описанное выше выполнение обладает, однако, тем преимуществом, что канавки ориентируются с самосовмещением относительно внешней STI.

Вслед за структурированием шин слов осуществляют обычные и сами по себе известные этапы изготовления управляющих элементов. К ним относится, в частности, осуществляемая независимо от структуры запоминающих ячеек имплантация для областей истока и стока управляющих транзисторов, включая LDD- и Pocket-имплантаты. Разводка осуществляется посредством подходящего числа структурированных слоев металлизации, расположенных в промежуточных металлических диэлектриках. Из описания изготовления устройства из запоминающих ячеек, согласно изобретению, следует ее структура и, в частности, конструкция отдельной запоминающей ячейки, как она заявлена также отдельно.

1. Устройство памяти из запоминающих ячеек с запоминающим транзистором, содержащим на верхней стороне полупроводниковой подложки (1) или полупроводникового слоя электрод (2) затвора, расположенный между выполненными в полупроводниковом материале областью (3) истока и областью (4) стока и отделенный от полупроводникового материала диэлектрическим материалом, имеющим предусмотренный для захвата носителей заряда запоминающий слой (6) между ограничительными слоями (5, 7), причем электрод (2) затвора расположен в канавке, выполненной в полупроводниковом материале между областью (3) истока и областью (4) стока, а запоминающий слой (6) расположен по меньшей мере между областью (3) истока и электродом (2) затвора и между областью (4) стока и электродом (2) затвора, при этом в упомянутом устройстве каждый из электродов (2) затворов находится в электропроводящем соединении с предусмотренной в качестве шины слов проводящей дорожкой (8), а область (3) истока и область (4) стока одной запоминающей ячейки одновременно служат в качестве соответственно области стока и области истока соседней запоминающей ячейки, при этом а) области истока и стока представляют собой части проходящих вдоль канавок разрядных шин; b) шины слов проходят поперек канавок; с) пространства между смежными электродами затворов в той же самой канавке заполнены диэлектрическим материалом.

2. Устройство по п.1, в котором включающая в себя запоминающий слой (6) последовательность слоев нанесена на всю поверхность полупроводникового материала между электродами (2) затворов и полупроводниковым материалом и между проводящими дорожками (8) и полупроводниковым материалом.

3. Устройство по п.1, в котором запоминающий слой (6) прерван между стенками канавки и/или между двумя соседними между собой канавками.

4. Устройство по п.1, в котором электроды (2) затворов расположены в V-образных или по меньшей мере имеющих косо ориентированные стенки канавках в полупроводниковом материале.

5. Устройство по п.1, в котором расстояние между областью (3) истока и областью (4) стока одной и той же запоминающей ячейки составляет самое большее 180 нм.

6. Устройство по п.5, в котором расстояние между областью (3) истока и областью (4) стока одной и той же запоминающей ячейки составляет самое большее 150 нм.

7. Способ изготовления устройства памяти по любому из пп.1-6, согласно которому на первом этапе в полупроводниковой подложке (1) или полупроводниковом слое изготовляют множество проходящих параллельно друг другу канавок (14) и граничащие с ними сбоку легированные области, служащие в качестве истока (3), стока (4) и разрядной шины; на втором этапе в канавках изготовляют запоминающую среду путем последовательного нанесения нижнего ограничительного слоя (5), запоминающего слоя (6), выполненного из диэлектрического материала, и верхнего ограничительного слоя (7); на третьем этапе в канавки помещают предусмотренный для соответствующего электрода (2) затвора электропроводящий материал, после чего структурируют служащие шинами слов проводящие дорожки (8), причем шины слов располагают поперек канавок для соединения с электродами затворов.

8. Способ по п.7, в котором на первом этапе вытравливают множество канавок, эти канавки заполняют оксидом, осуществляют имплантацию легирующей примеси для образования легированных областей и с применением маски, закрывающей предусмотренную в качестве STI-канавок для электрической изоляции часть канавок, удаляют оксид на по меньшей мере участках, предусмотренных для электрода затвора.

9. Способ по п.7, в котором между вторым и третьим этапами удаляют по меньшей мере до нижнего ограничительного слоя верхний ограничительный слой и запоминающий слой по меньшей мере между стенками выполненной в полупроводниковом материале канавки, предусмотренной для по меньшей мере одного электрода затвора, и/или между двумя соседними между собой канавками.

10. Способ по п.7, в котором на первом этапе канавки заполняют диэлектрическим материалом и с применением маски изготовляют отверстия (25) в диэлектрическом материале, а на третьем этапе в каждое такое отверстие помещают электропроводящий материал.

11. Способ по п.7, в котором на первом этапе канавки заполняют диэлектрическим материалом, наносят слой (19) из диэлектрического материала, перед вторым этапом поперек канавок в диэлектрическом материале изготовляют несколько ориентированных параллельно друг другу полосообразных отверстий, а на третьем этапе в каждое такое отверстие помещают электропроводящий материал.