Электродная решетка, способ ее изготовления и устройство обработки и/или хранения данных

Иллюстрации

Показать всеНастоящее изобретение относится к устройствам, содержащим функциональные элементы, образующие планарный набор. В электродной решетке, содержащей первый и второй тонкопленочные электродные слои (L1, L2) с электродами (ε) в форме полосковых электрических проводников в каждом слое, электроды (ε) отделены друг от друга только тонкой пленкой (6) из электрически изолирующего материала, толщина которой составляет небольшую долю ширины электродов и которая проходит, по меньшей мере, вдоль боковых краев электродов, образуя изолирующие стенки (6а) между ними. Электродные слои (L1, L2) подвергают планаризации для того, чтобы обеспечить высокую степень плоскостности слоев. В устройстве, содержащем одну или более электродных решеток (ЕМ), электродные слои (L1, L2) каждой решетки взаимно ориентированы таким образом, что их электроды (1, 2) скрещиваются или располагаются взаимно перпендикулярно. Между электродами (1, 2) заключена в виде цельного слоя функциональная среда (3), в результате чего формируется устройство с матричной адресацией (предпочтительно пассивной), которое может быть использовано, например, в качестве устройства обработки или хранения данных с матричной адресацией, содержащего индивидуально адресуемые функциональные элементы (5), соответственно в форме логических ячеек или ячеек памяти. При этом коэффициент заполнения цельного слоя функциональной среды (3) указанными ячейками близок к 1, а максимальное количество ячеек в устройстве приближается к А/f2, где А - площадь поверхности функциональной среды, заключенной между электродными слоями (L1, L2), a f - минимальный технологически достижимый размер. Техническим результатом является обеспечение более эффективной адресации и обеспечение более высокой плотности записи сохраняемых данных. 3 н. и 19 з.п. ф-лы, 12 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к электродной решетке, содержащей первый и второй тонкопленочные электродные слои с электродами в форме полосковых электрических проводников в каждом слое, причем электроды второго электродного слоя скрещены или ориентированы, по существу, перпендикулярно по отношению к электродам первого электродного слоя. По меньшей мере, один из электродных слоев расположен на изолирующей поверхности подложки или объединительной платы. При этом электродные слои расположены в параллельных взаимно смещенных плоскостях, контактирующих с цельным слоем функциональной среды, находящейся между указанными слоями.

Настоящее изобретение относится также к устройству, содержащему, по меньшей мере, одну электродную решетку, содержащую первый и второй тонкопленочные электродные слои с электродами в форме полосковых электрических проводников в каждом слое. Электроды второго электродного слоя скрещены или ориентированы, по существу, перпендикулярно по отношению к электродам первого электродного слоя. По меньшей мере, один из электродных слоев расположен на изолирующей поверхности подложки или объединительной платы, при этом первый и второй электродные слои расположены в параллельных взаимно смещенных плоскостях, контактирующих с цельным слоем функциональной среды, находящейся между указанными слоями.

Устройство по изобретению содержит также функциональные элементы, образованные в объеме функциональной среды и определяемые зонами взаимного наложения электродов первого электродного слоя и электродов второго электродного слоя с формированием набора с матричной адресацией. Каждый такой функциональный элемент может быть активирован путем подачи напряжения на скрещивающиеся электроды, задающие этот функциональный элемент. Физическое состояние данного функционального элемента под действием приложенного к нему электрического потенциала может быть изменено на временной или постоянной основе или переключено между двумя различимыми физическими состояниями. При этом подача напряжения соответствует адресации указанного функционального элемента с целью осуществления операции записи или считывания.

В зависимости от свойств используемой функциональной среды функциональные элементы способны функционировать в качестве переключаемых логических элементов в устройстве обработки данных, ячеек памяти в устройстве хранения данных или пикселов в устройстве отображения информации с адресацией функциональных элементов по схеме матричной адресации.

Уровень техники

Настоящее изобретение, в первую очередь, касается электродных решеток для использования в устройствах, содержащих функциональные элементы, образующие планарный набор, в котором адресация элементов осуществляется посредством первой электродной решетки с параллельными полосковыми электродами, расположенными по одну сторону от функциональных элементов в контакте с ними, и второй электродной решетки с аналогичными электродами, которые ориентированы, однако, перпендикулярно электродам первой электродной решетки и расположены по другую сторону от функциональных элементов в контакте с ними. В совокупности названные элементы образуют так называемое устройство с матричной адресацией. Устройства подобного типа могут, например, содержать функциональные элементы в виде логических ячеек или ячеек памяти. При этом функциональные элементы могут содержать одно или более активных переключающих средств. В таком случае устройство с матричной адресацией называется устройством с активной матричной адресацией. Альтернативно, функциональные элементы могут содержать только пассивные средства, например, резистивные или емкостные. В таком случае устройство с матричной адресацией называется устройством с пассивной матричной адресацией.

Последнее из названных устройств рассматривается как обеспечивающее более эффективный вариант адресации, например, в случае запоминающих устройств, поскольку в составе ячейки памяти не требуется иметь никаких переключающих элементов, в частности, транзисторов. Одновременно представляется желательным обеспечить как можно более высокую плотность записи сохраняемых данных. Однако существующие правила конструирования накладывают ограничения на минимальный размер ячейки и одновременно ограничивают коэффициент заполнения, т.е. площадь поверхности запоминающего материала, которая реально может быть использована для целей хранения информации в устройстве с матричной адресацией.

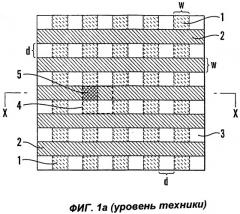

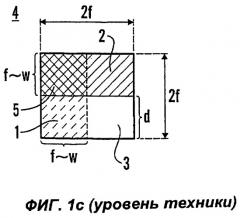

На фиг.1а изображено известное устройство с матричной адресацией, которое содержит цельный планарный слой функциональной среды 3, расположенный между первой электродной решеткой, содержащей параллельные полосковые электроды 1, имеющие ширину w и отстоящие друг от друга на расстояние d, и схожей второй электродной решеткой, содержащей параллельные полосковые электроды 2, имеющие такую же ширину. При этом электроды 2 ориентированы перпендикулярно электродам 1. Взаимное наложение электродов 1, 2 соответствующих электродных решеток задает в цельном слое функциональной среды 3 функциональные элементы 5. Посредством подачи напряжения на электроды, скрещивающиеся в зоне расположения функционального элемента (который может представлять собой, например, логическую ячейку или ячейку памяти), его функциональное состояние может быть изменено или переключено.

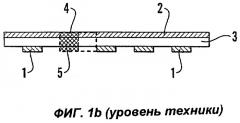

Фиг.1b, на котором известное устройство по фиг.1а показано в сечении плоскостью Х-Х, поясняет взаимное расположение электродов 1, 2 и цельного слоя функциональной среды 3, расположенного между ними, а также положение функционального элемента 5. Как правило, свойства функциональной среды 3 подбираются таким образом, что подача напряжения на скрещенные электроды 1, 2 оказывает влияние только на функциональный элемент 5, расположенный в зоне скрещивания этих электродов, т.е. в непосредственной близости от функционального элемента 5. Если функциональная среда 3, образующая цельный слой, является электропроводной, указанное условие может быть выполнено за счет придания ей свойств анизотропной электропроводности. Другими словами, проводимость будет иметь место только в вертикальном направлении, при отсутствии какого-либо тока через слой функциональной среды к другим функциональным элементам.

Однако во многих приложениях функциональная среда, образующая цельный слой, может не обладать электропроводностью, т.е. представлять собой диэлектрик. Следовательно, функциональный элемент может рассматриваться, как обладающий высоким сопротивлением или являющийся диэлектриком, т.е. как конденсатор. При этом диэлектрическая функциональная среда может представлять собой поляризуемый неорганический или органический материал, обладающий гистерезисными свойствами. К числу подобных материалов относятся как ферроэлектрические, так и электретные материалы. Поляризационные и гистерезисные свойства подобных материалов могут быть использованы для создания, например, ферроэлектрических или электретных матричных запоминающих устройств, имеющих конфигурацию, подобную представленной на фиг.1а. В устройствах такого типа состояние поляризации ячейки памяти, т.е. функционального элемента 5, может быть задано подачей соответствующего напряжения на электроды, задающие ячейку памяти, лежащую в зоне их взаимного скрещивания. При этом поляризацию ячейки можно переключать; альтернативно, ячейка может быть возвращена в свое исходное состояние посредством операций, соответствующих записи и считыванию данных в эту ячейку.

Функциональные характеристики подобных матричных устройств, естественно, зависят не только от свойств выбранной функциональной среды, но также от архитектурных и структурных ограничений, накладываемых при создании запоминающего устройства. Емкость запоминающей среды 3, выполненной в виде цельного слоя, зависит от размера и плотности расположения ячеек 5 памяти. В свою очередь, данные параметры зависят от минимального технологически достижимого размера, который может быть реализован в процессе изготовления устройства. Например, когда электроды формируются посредством металлизации, т.е. путем нанесения слоя металла, которому затем придается заданный рисунок с использованием фотомикролитографического процесса с применением фотолитографических масок в сочетании, например, с травлением, минимальный технологически достижимый размер f определяется свойствами маски. В свою очередь, свойства маски будут зависеть от длины волны используемого излучения. Другими словами, на современном уровне развития технологии указанный размер f будет составлять 0,15-0,2 мкм. Как следствие, ширина w электродов 1, 2 и расстояние между ними будут примерно того же порядка.

В этой связи можно отметить, что параметр 2f обычно называется шагом, а максимальное количество разрешаемых линий на единицу длины, достигаемое с применением известной технологии изготовления, задается параметром 0,5f. Соответственно, максимальное количество элементов на единицу площади задается коэффициентом 0,25f2. Следовательно, если рассмотреть участок 4, показанный на фиг.1, площадь ячейки, как это видно из фиг.1с (на которой участок 4 изображен более детально), составит f2. При этом становится понятно, что для каждой ячейки требуется пространство, соответствующее участку 4, площадь которого составляет 4f2, т.е. в 4 раза превышает площадь f2 поверхности ячейки. Из проведенного анализа ясно, что матрица, представленная на фиг.1а, имеет коэффициент заполнения, равный 0,25 (т.е. f2/4f2). Следовательно, степень использования поверхности, сформированной слоем функциональной среды 3, является низкой. Для того чтобы достичь более высокого коэффициента заполнения или более высокой плотности расположения ячеек 5 в слое функциональной среды 3, представляется желательным либо увеличить коэффициент заполнения, либо добиться более высокого разрешения в процессе изготовления матрицы, т.е. перейти к размерам, меньшим чем 0,1 мкм. Однако во втором случае, хотя и появится возможность увеличить общее количество ячеек на той же площади, возможность повышения коэффициента заполнения не будет гарантирована.

В случае матричных устройств активного типа, которые содержат, по меньшей мере, один активный переключающий элемент, ассоциированный с каждым функциональным элементом (т.е. с ячейкой), коэффициент заполнения имеет еще меньшее значение и в типичном случае составляет только 1/6, т.е. 16,7%.

Из патента США №5017515 известен процесс, обеспечивающий получение сублитографических расстояний между элементами интегральной схемы. Как показано на фиг.1 названного документа, известный процесс применим для формирования плотно расположенных параллельных полосковых электродов 13, 19, изолированных друг от друга посредством изолирующего элемента 14. Данный элемент свободен от каких-либо ограничений на размер, налагаемых использованием фотомикролитографического процесса. Как следствие, данный элемент может быть выполнен очень тонким по сравнению с размерами проводников, т.е. электродов. В указанном патентном документе описано, каким образом электродные решетки, изготовленные предлагаемым способом, могут быть применены для формирования полосковых электродов для элементов с плавающим затвором в интегральной схеме, например, в полупроводниковом запоминающем устройстве, ячейки памяти которого содержат переключающую и запоминающую транзисторные структуры. При этом разрядные шины (шины данных) образованы соответствующим допированием подложки, очевидно, с применением для допирования той же фотомаски, которая применяется при формировании электродного слоя высокой плотности. Управляющие электроды 42 для разрядных шин и для числовых (управляющих) шин изолированы с помощью соответствующего изолятора от полосковых электродов 13, 19 плавающих затворов. Результирующая структура представляет собой полупроводниковое запоминающее устройство с набором мультитерминальных ячеек памяти, содержащих транзисторы.

Однако в данном патенте США №5017515 не содержится никаких указаний по формированию электродных решеток с двумя электродными слоями, каждый из которых содержит электроды, расположенные с высокой плотностью и ориентированные таким образом, что электроды двух указанных слоев совместно образуют электродную матрицу, пригодную для адресации функциональных элементов в составе цельного слоя функциональной среды, расположенной между электродными слоями и находящейся в контакте с этими слоями. Эффективное использование матричной адресации к функциональным элементам в составе цельного слоя функциональной среды предполагает также высокую степень планаризации, которой должны обладать слои устройства с матричной адресацией описанного типа. Однако это требование является труднодостижимым с использованием известной технологии, поскольку создание топографических структур, ориентированных в ортогональном направлении над подложкой, подразумевает, что дополнительные электродные слои будут воспроизводить контуры данной структуры в своих поверхностных элементах. Кроме того, известные решения оказались бы непригодными в случае, когда множество наборов с матричной адресацией должны быть собраны в стопу с образованием объемных (трехмерных) устройств типа стопы из множества запоминающих устройств с матричной адресацией, известных из уровня техники.

Пример устройства с матричной адресацией, выполненного в виде устройства обработки данных или запоминающего устройства, содержащего электронные слои, расположенные по обе стороны от цельного слоя функциональной среды таким образом, что электроды данных слоев образуют ортогональную электродную матрицу, описан, например, в международной заявке WO 98/58383. Разумеется, устройства подобного типа выиграют от повышения плотности расположения функциональных элементов в составе матрицы независимо от конкретного вида функциональных элементов, в частности, когда эти элементы представляют собой ячейки памяти, при условии, что данные элементы соответствуют зоне взаимного наложения скрещивающихся электродов первого и второго электродных слоев.

Раскрытие изобретения

С учетом изложенного главная задача, на решение которой направлено настоящее изобретение, состоит в том, чтобы обеспечить возможность повышения коэффициента заполнения в матричных устройствах вышеописанного типа до значений, приближающихся к 1, и тем самым достичь максимального использования площади цельного слоя функциональной среды 3 в подобных устройствах. При этом на это использование не должны влиять ограничения, связанные с реальным или практичным значением минимального технологически достижимого размера f. Действительно, коэффициент заполнения не будет изменяться при уменьшении размера f, хотя подобное уменьшение, разумеется, будет приводить к дальнейшему увеличению количества функциональных элементов, которые можно сформировать в цельном слое функциональной среды 3.

Матричные устройства типа представленного на фиг.1а могут быть собраны в стопу, с установкой устройств друг на друга для формирования объемных устройств. В таком случае каждое единичное устройство отделяется от следующего устройства в стопе посредством разделительного или изолирующего слоя для того, чтобы подача напряжений на электроды одного из таких устройств и переключение функциональных элементов этого устройства не влияли на смежные устройства в стопе. Подобные объемные устройства, разумеется, обеспечивают возможность создания объемных запоминающих устройств большой емкости. Однако нетрудно понять, что за счет повышения коэффициента заполнения до значений близких к 1 (т.е. к 100%), суммарная емкость единичного матричного устройства может приблизиться к емкости четырех аналогичных матричных устройств обычного типа, собранных в стопу для формирования объемного устройства.

Хотя не существует теоретического предела для количества устройств, образующих стопу, можно рассматривать как недостаток такой стопы появление нежелательных электрических, физических и тепловых связей, которые могут возникать между устройствами, собираемыми в стопу, например, в случае широкомасштабной параллельной адресации к функциональным элементам входящих в стопу устройств. Еще одним недостатком является наличие отклонений от плоскостности, присущее каждому из устройств, составляющих стопу. Хотя такое устройство может рассматриваться как, по существу, планарное, отклонения от плоскостности будут накапливаться по мере добавления очередных устройств к стопе. В результате, по мере увеличения количества устройств в стопе, она будет содержать все большее количество неровностей. Наличие подобных неровностей будет также весьма нежелательным при реализации технологии изготовления, по существу, планарных контуров.

С учетом данного обстоятельства дополнительная задача, решаемая настоящим изобретением, заключается в увеличении суммарной емкости, определяемой общим количеством функциональных элементов, которые могут быть реализованы в матричном устройстве, и в снижении за счет этого необходимости разработки многослойных или объемных устройств в виде многослойной стопы в тех случаях, когда сопоставимая емкость может быть достигнута с использованием стопы, содержащей только четверть от количества устройств или слоев, необходимых при использовании известной технологии.

Кроме того, изобретение решает задачу создания электродной решетки, которая легко может быть реализована с достижением очень высокой степени плоскостности, т.е. с устранением поверхностных неровностей. Тем самым электродная решетка становится более приспособленной для использования в объемных устройствах типа стопы.

Перечисленные задачи, а также дополнительные преимущества и свойства реализуются в соответствии с настоящим изобретением за счет создания электродной решетки. Электродная решетка по изобретению характеризуется тем, что каждый из тонкопленочных электродных слоев содержит первый набор указанных электродов с шириной wa и высотой ha, отстоящих друг от друга на расстояние d, равное их ширине wа или превышающее ее, второй набор указанных электродов с шириной wb и высотой hb, находящихся в промежутках между электродами первого набора и электрически изолированных от них посредством тонкой пленки из электрически изолирующего материала толщиной δ, расположенной, по меньшей мере, вдоль боковых краев параллельных электродов первого и второго наборов с формированием между указанными электродами изолирующей стенки толщиной δ, существенно меньшей ширины wa или ширины wb, причем расстояние d между электродами первого набора составляет wb+2δ, а электродные слои с электродами и с тонкой изолирующей пленкой образуют цельные планарные слои в составе электродной решетки.

Электропроводный материал электродов, по меньшей мере, одного из электродных слоев предпочтительно нанесен непосредственно на поверхность подложки.

Кроме того, желательно, чтобы электроды одного из электродных слоев были открыты на наружную сторону указанного слоя, противоположную по отношению к другому электродному слою. Альтернативно, поверхность одного из электродных слоев, противоположная по отношению к другому электродному слою, может быть закрыта подложкой.

В одном из предпочтительных вариантов осуществления изобретения площади поперечных сечений электродов обоих наборов электродов могут быть равными, т.е. выполняется соотношение waha=wbhb.

В другом предпочтительном варианте площадь поперечного сечения электродов первого набора электродов выбрана отличной от площади поперечного сечения электродов второго набора, т.е. waha≠wbhb.

Согласно еще одному предпочтительному варианту электроды обоих наборов выполнены из одного электропроводного материала.

В следующем предпочтительном варианте осуществления изобретения электроды второго набора электродов выполнены из электропроводного материала, отличного от электропроводного материала, из которого выполнены электроды первого набора электродов.

Применительно к данному варианту представляется желательным, чтобы электропроводные материалы, из которых выполнены электроды первого и второго наборов электродов, обладали электрическими проводимостями σа и σb соответственно, удовлетворяющими соотношению:

обеспечивающему одинаковость электропроводных свойств электродов первого и второго наборов электродов.

При этом предпочтительно, чтобы в электродной решетке по изобретению изолирующие стенки между электродами первого набора электродов и электродами второго набора электродов составляли части тонкой пленки изолирующего материала, нанесенной в виде протяженного слоя, покрывающего электроды первого набора электродов, а также подложку в промежутках между электродами первого набора электродов. В данном случае электроды второго набора электродов образованы в углублениях между указанными стенками и расположены над частями тонкой пленки, покрывающими подложку. В то же время верхние поверхности электродов второго набора электродов находятся в одной плоскости с поверхностью части изолирующей тонкой пленки, покрывающей верхнюю поверхность электродов первого набора. Электроды первого и второго наборов электродов имеют равные высоты hb=ha, a электродные слои, содержащие электроды и изолирующую тонкую пленку, образуют цельный планарный слой в составе электродной решетки.

Согласно еще одному предпочтительному варианту выполнения электродной решетки изолирующие стенки между электродами первого набора электродов и электродами второго набора электродов составляют части тонкой пленки изолирующего материала, нанесенной в виде слоя, покрывающего боковые края электродов первого набора электродов вплоть до их верхних поверхностей, а также подложку в промежутках между электродами первого набора электродов. Электроды второго набора электродов образованы в углублениях между указанными стенками и расположены над частями тонкой пленки, покрывающими подложку. При этом верхние поверхности электродов второго набора электродов находятся в одной плоскости с верхними кромками изолирующих стенок и с верхними поверхностями электродов первого набора электродов. Электроды второго набора электродов в данном случае имеют высоту hb=ha-δ, а электродные слои, содержащие электроды и изолирующую тонкую пленку, образуют цельный планарный слой толщиной ha в составе электродной решетки.

В следующем предпочтительном варианте выполнения электродной решетки изолирующие стенки между электродами первого набора электродов и электродами второго набора электродов составляют части тонкой пленки изолирующего материала, нанесенной в виде слоя, покрывающего электроды первого набора электродов, вплоть до подложки. Электроды второго набора электродов образованы в углублениях между указанными стенками и расположены непосредственно на подложке, причем верхние поверхности электродов второго набора электродов находятся в одной плоскости с поверхностью части изолирующей тонкой пленки, покрывающей верхнюю поверхность электродов первого набора электродов. В данном случае электроды первого набора электродов имеют высоту ha=hb-δ, а электродные слои, содержащие электроды и изолирующую тонкую пленку, образуют цельный планарный слой толщиной hb в составе электродной решетки.

Вышеперечисленные задачи, а также дополнительные преимущества и свойства реализуются в соответствии с настоящим изобретением также за счет разработки способа изготовления электродного слоя в составе электродной решетки. Способ по изобретению характеризуется тем, что включает операции нанесения на подложку планарного слоя электропроводного материала толщиной ha и профилирования планарного слоя электропроводного материала с формированием первого набора полосковых электродов шириной wa и высотой ha, пространственно отделенных друг от друга углублениями, образованными при осуществлении профилирования. Операция профилирования в этом случае включает удаление частей электропроводного материала, делая тем самым открытой поверхность подложки между полосковыми электродами первого набора электродов. В результате электроды первого набора электродов оказываются расположенными друг от друга на расстоянии а, равном ширине углублений между указанными электродами, а также равном или превышающем значение wa.

Далее способ по изобретению включает операцию формирования тонкой пленки изолирующего материала, покрывающей, по меньшей мере, боковые края электродов первого набора электродов, а также операцию нанесения электропроводного материала в углубления между частями тонкой пленки, покрывающими боковые края электродов первого набора электродов. При этом имеет место формирование второго набора электродов, имеющих ширину wb и высоту hb, с образованием электродного слоя в виде цельного планарного слоя в составе электродной решетки.

Предпочтительный вариант осуществления способа по изобретению включает формирование изолирующей тонкой пленки в виде цельного слоя, покрывающего как электроды первого набора электродов, так и открытую поверхность подложки. Данный вариант включает также нанесение электропроводного материала для образования второго набора электродов в углубления между электродами первого набора электродов и поверх изолирующей тонкой пленки и осуществление планаризации электродного слоя таким образом, чтобы верхняя поверхность электродов второго набора электродов находилась на одном уровне с изолирующей тонкой пленкой, покрывающей электроды первого набора электродов.

Согласно другому предпочтительному варианту способ по изобретению включает формирование изолирующей тонкой пленки в виде цельного слоя, покрывающего электроды первого набора электродов и открытую поверхность подложки, а также нанесение электропроводного материала для образования второго набора электродов в углубления между электродами первого набора электродов и поверх изолирующей тонкой пленки. Способ включает далее осуществление планаризации электродного слоя таким образом, чтобы удалить изолирующую тонкую пленку с верхней поверхности электродов обоих наборов, открыв тем самым верхнюю поверхность электродов и обеспечив расположение верхних поверхностей электродов обоих наборов и верхних кромок изолирующей тонкой пленки на одном уровне, соответствующем верхней поверхности электродного слоя.

Согласно еще одному предпочтительному варианту способ по изобретению включает формирование изолирующей тонкой пленки в виде цельного слоя, покрывающего электроды первого набора электродов и открытую поверхность подложки, и удаление изолирующей тонкой пленки со дна углублений, открывая тем самым поверхность дна, но оставляя части изолирующей тонкой пленки, покрывающие электроды первого набора электродов вплоть до подложки. Предусматриваются также нанесение электропроводного материала для образования второго набора электродов в указанные углубления и осуществление планаризации электродного слоя. Планаризация проводится таким образом, чтобы обеспечить расположение верхних поверхностей электродов второго набора и поверхности изолирующей тонкой пленки, покрывающей электроды первого набора, на одном уровне, соответствующем верхней поверхности электродного слоя.

В соответствии с другим вариантом осуществления способ по изобретению включает нанесение цельного слоя функциональной среды, покрывающего один электродный слой, сформированный на подложке, и контактирующего с электродами данного электродного слоя, и последующее формирование второго электродного слоя непосредственно на цельном слое функциональной среды посредством операций, аналогичных операциям, использованным при формировании электродного слоя на подложке. Желательно после этого покрыть электродный слой, сформированный на цельном слое функциональной среды, подложкой или объединительной платой.

Далее, при осуществлении способа по изобретению в качестве материала электродов первого набора и/или подложки предпочтительно выбирают материал, пригодный для осуществления поверхностного оксидирования, и формируют изолирующую тонкую пленку посредством оксидирования поверхности, по меньшей мере, материала электродов или подложки посредством, по меньшей мере, одной операции оксидирования.

Вышеперечисленные задачи, а также дополнительные преимущества и свойства реализуются в рамках настоящего изобретения, кроме того, за счет создания устройства обработки и/или хранения данных, характеризующегося прежде всего тем, что электроды в составе электродной решетки расположены в соответствующих электродных слоях, имеют примерно одинаковую ширину w и изолированы друг от друга посредством изолирующей тонкой пленки толщиной δ, составляющей долю от ширины w. При этом минимальное значение w сопоставимо с минимальным технологически достижимым размером f. Коэффициент заполнения функциональной среды функциональными элементами близок к 1 при общем количестве функциональных элементов, близком к максимальному пределу, составляющему A/f2, т.е. определяемому общей площадью А поверхности функциональной среды, заключенной между электродными слоями, и указанным размером f.

Краткое описание чертежей

Настоящее изобретение станет лучше понятно из изучения, совместно с прилагаемыми чертежами, нижеследующего описания некоторых вариантов осуществления устройства и электродной решетки, а также способа ее изготовления.

Фиг.1а-1с иллюстрируют известное устройство с пассивной матричной адресацией, обладающее типичным коэффициентом заполнения, присущим устройством подобного типа, описанным выше.

На фиг.2a-2f схематично иллюстрируются операции способа изготовления первого варианта электродного слоя согласно изобретению.

Фиг.3а и 3b схематично иллюстрируют операции, используемые при изготовлении второго варианта электродного слоя согласно изобретению после выполнения операции, соответствующей фиг.2с.

Фиг.4а и 4b схематично иллюстрируют операции, используемые при изготовлении третьего варианта электродного слоя согласно изобретению после выполнения операции, соответствующей фиг.2с.

Фиг.5а и 5b схематично иллюстрируют операции, используемые при изготовлении четвертого варианта электродного слоя после выполнения операции, соответствующей фиг.2b или 2с.

На фиг.6а, на виде сверху, схематично представлен вариант выполнения электродного слоя в электродной решетке согласно изобретению.

На фиг.6b вариант электродного слоя по фиг.6а схематично изображен в сечении.

На фиг.7 схематично, в сечении, изображен другой вариант выполнения электродного слоя в электродной решетке согласно изобретению.

На фиг.8 схематично, в сечении, изображен третий вариант выполнения электродного слоя в электродной решетке согласно изобретению.

На фиг.9а, на виде сверху, схематично представлен четвертый вариант выполнения электродного слоя в электродной решетке согласно изобретению.

На фиг.9b вариант электродного слоя по фиг.9а схематично изображен в сечении.

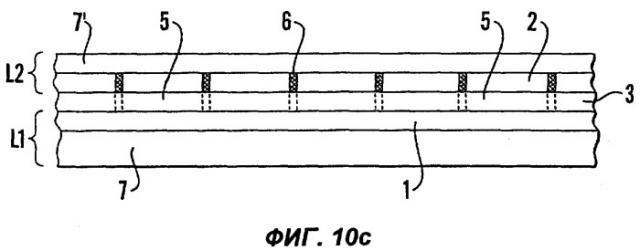

На фиг.10а в сечении представлен вариант выполнения первого электродного слоя, который покрыт цельным слоем функциональной среды, в составе электродной решетки согласно изобретению.

На фиг.10b показан второй электродный слой, выполненный аналогично первому электродному слою, и установленный в положение, соответствующее формированию электродной решетки по изобретению.

На фиг.10с представлен предпочтительный вариант электродной решетки по изобретению.

На фиг.10d показано, как множество электродных решеток может быть собрано в стопу с образованием объемного устройства.

Фиг.11a-11d схематично иллюстрируют операции, используемые при изготовлении еще одного варианта электродной решетки согласно изобретению.

На фиг.11е показано, как множество электродных решеток согласно данному варианту может быть собрано в стопу с образованием объемного устройства.

На фиг.12а, на виде сверху, изображено устройство с матричной адресацией, соответствующее настоящему изобретению, снабженное электродной решеткой по изобретению.

Фиг.12b соответствует сечению устройства по фиг.12а плоскостью Х-Х.

На фиг.12с представлена часть устройства по фиг.12а, иллюстрирующая коэффициент заполнения, достижимый с помощью настоящего изобретения.

Осуществление изобретения

Далее будет подробно описана электродная решетка по настоящему изобретению. При этом будут даны ссылки на фиг.2-5, иллюстрирующие различные варианты изготовления электродного слоя в данной электродной решетке. Необходимо учитывать, что названные фигуры являются весьма схематичными: в частности, на них показано лишь минимальное количество электродов, достаточное для пояснения производственных операций и структуры электродного слоя в электродной решетке по изобретению.

В соответствии с изобретением электродная решетка содержит два однотипных электродных слоя L1, L2, электроды ε которых обращены к цельному (единому) слою 3 функциональной среды, расположенной между электродными слоями и находящейся в контакте с электродами этих слоев. Второй электродный слой L2, разумеется, может быть сформирован путем аналогичных операций. При этом должен быть соответствующим образом расположен относительно первого электродного слоя L1 и слоя 3 функциональной среды, как это будет более подробно объяснено далее со ссылками на предпочтительные примеры выполнения электродной решетки ЕМ. Далее будет описано также, каким образом электродные решетки могут быть собраны в стопу с целью создания объемной (трехмерной) структуры, содержащей множество электродных решеток по настоящему изобретению.

На фиг.2а показано, что на подложку 7 (которая может быть выполнена из любого подходящего материала при обязательном условии, что он должен иметь, по меньшей мере, одну поверхность с изоляционными свойствами) наносится слой электропроводного материала εm. В рассматриваемом случае слой материала εm наносится на поверхность подложки 7, обладающую изоляционными свойствами. На второй операции, которая иллюстрируется фиг.2b, из слоя электропроводного материала εm в соответствии с заданным рисунком посредством операции профилирования формируются электроды εa, образующие первый набор Еа электродов, расположенных на расстоянии d друг от друга. При этом между электродами εa образуются углубления 8. Должно быть понятно, что ширина w электродов εа, обеспечиваемая на операции профилирования, ограничивается минимальным размером f, достижимым в используемой технологии. Например, при использовании обычной технологии фотомикролитографии с применением фотомасок и с последующим травлением значение f может быть доведено до 0,15 мкм или даже менее. При этом данный размер будет предельным как для минимальной ширины электродов εа, так и для расстояния d между ними.

На третьей производственной операции, которая иллюстрируется фиг.2с, полосковые электроды εa и открытые части подложки 7 покрывают тонкой пленкой 6 изолирующего материала, напыленной или сформированной с использованием любого иного подходящего процесса, например, путем химического осаждения из паров, распыления и т.д. Как это хорошо известно специалистам в данной отрасли, изолирующий слой на основе пленки 6 может быть сделан предельно тонким, например, составляющим несколько нанометров, т.е. его толщина δ будет очень малой по сравнению с шириной wa электродов εа.

На четвертой производственной операции, которая иллюстрируется фиг.2d, производят удаление изолирующего слоя 6, покрывающег