Магниторезистивная оперативная память с передачей спинового вращательного момента и способы разработки

Иллюстрации

Показать всеИзобретение относится к разработке памяти в области магниторезистивной оперативной памяти с передачей спинового вращательного момента. Техническим результатом является уменьшение времени отклика (считывания/записи). Раскрыты системы, схемы и способы для определения напряжений считывания и записи для заданного транзистора числовой шины в магниторезистивной RAM с передачей спинового вращательного момента (STT-MRAM). Для операций записи может быть подано первое напряжение так, чтобы операции записи происходили в области насыщения транзистора числовой шины. Для операций считывания может быть подано второе напряжение, меньшее, чем первое напряжение, так чтобы операции считывания происходили в линейной области транзистора числовой шины. 3 н. и 17 з.п. ф-лы, 15 ил.

Реферат

Испрашивание приоритета

Настоящая заявка на патент испрашивает приоритет предварительной заявки на патент США за номером 60/910255, называемой "Spin Transfer Torque Magnetoresistive Random Access Memory with Reduced Read Voltage", поданной 5 апреля 2007 г., принадлежащей заявителю настоящей заявки и вследствие этого явно включенной в это описание в качестве ссылки.

Область техники, к которой относится изобретение

Варианты осуществления изобретения относятся к оперативной памяти (RAM). Более конкретно варианты осуществления изобретения относятся к разработке памяти в области магниторезистивной оперативной памяти с передачей спинового вращательного момента (STT-MRAM).

Уровень техники

Оперативная память (RAM) является универсальным компонентом современной цифровой архитектуры. Как очевидно специалистам в данной области техники, оперативная память может быть автономными устройствами или может быть интегрирована или встроена внутрь устройств, которые используют RAM, таких как микропроцессоры, микроконтроллеры, специализированные интегральные микросхемы (ASIC), однокристальная система (SoC) и другие подобные устройства. RAM может быть энергозависимой или энергонезависимой. Энергозависимая RAM теряет сохраненную в ней информацию при выключении питания. Энергонезависимая RAM может поддерживать свое содержимое памяти, даже при выключении питания памяти. Хотя энергонезависимая RAM имеет свои преимущества, состоящие в обеспечении возможности поддержания сохранности ее содержимого при отсутствии питания, обычная энергонезависимая RAM осуществляет считывание/запись более медленно, чем энергозависимая RAM.

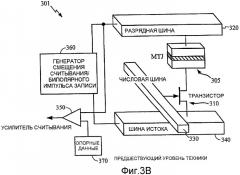

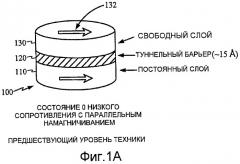

Магниторезистивная оперативная память (MRAM) является технологией энергонезависимой памяти, которая имеет время отклика (считывания/записи), сопоставимое с энергозависимой памятью. В отличие от обычных технологий RAM, при которых данные хранят в виде электрических зарядов или электрического тока, в MRAM используют магнитные элементы. Как иллюстрируют фиг.1A и 1B, элемент памяти 100 с магнитным туннельным переходом (MTJ) может быть сформирован из двух магнитных слоев 110 и 130, каждый из которых может иметь магнитное поле, разделенное изолирующим слоем 120 (туннельным барьером). Один из двух указанных слоев (например, постоянный слой 110) устанавливают в определенную полярность. Полярность 132 другого слоя (например, свободного слоя 130) является свободной для изменения в соответствии с полярностью внешнего поля, которое может быть применено. Изменение в полярности 132 свободного слоя 130 должно изменять сопротивление элемента 100 памяти MTJ. Например, когда полярности соориентированы, фиг.1A, существует состояние низкого сопротивления. Когда полярности не соориентированы, фиг.1B, то существует состояние высокого сопротивления. Иллюстрация MTJ 100 была упрощена, и специалисту в данной области техники будет очевидно, что каждый иллюстрируемый слой может содержать один или большее количество слоев материалов, как известно в технике.

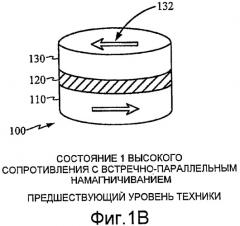

Согласно фиг.2A иллюстрируют ячейку 200 памяти обычной MRAM для операции считывания. Ячейка 200 содержит транзистор 210, разрядную шину 220, цифровую шину 230 и числовую шину 240. Ячейка 200 может быть считана посредством измерения электрического сопротивления MTJ 100. Например, определенный MTJ 100 может быть выбран посредством активизации соответствующего транзистора 210, который может переключать электрический ток с разрядной шины 220 через MTJ 100. Как описано выше, электрическое сопротивление MTJ 100 изменяется на основе ориентации полярностей в двух магнитных слоях (например, 110, 130), что обусловлено туннельным магниторезистивным эффектом. Сопротивление внутри любого определенного MTJ 100 может быть определено из электрического тока, результирующего из полярности свободного слоя. Обычно, если постоянный слой 110 и свободный слой 130 имеют одинаковую полярность, то сопротивление является низким, и считывают "0". Если постоянный слой 110 и свободный слой 130 имеют противоположную полярность, то сопротивление является более высоким, и считывают "1".

Согласно фиг.2B иллюстрируют ячейку 200 памяти обычной MRAM для операции записи. Операция записи MRAM является магнитной операцией. Соответственно, в продолжение операции записи транзистор 210 выключен. Электрический ток распространяется через разрядную шину 220 и цифровую шину 230 для установления магнитных полей 250 и 260, которые могут воздействовать на полярность свободного слоя MTJ 100 и, следовательно, на логическое состояние ячейки 200. Соответственно, данные могут быть записаны и сохранены в MTJ 100.

MRAM имеет несколько предпочтительных характеристик, которые делают ее кандидатом на универсальную память, такие как высокая скорость, высокая плотность (то есть, малый размер однобитовой ячейки), малое энергопотребление и малое снижение эффективности во времени. Однако у MRAM существуют проблемы в отношении масштабируемости. В частности, так как уменьшаются однобитовые ячейки, повышаются магнитные поля, используемые для переключения состояния памяти. Соответственно, вырастают плотность тока и энергопотребление для обеспечения более высоких магнитных полей, соответственно, ограничивая масштабируемость MRAM.

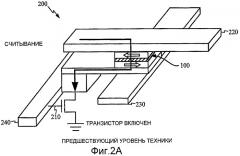

В отличие от обычной MRAM, в магниторезистивной оперативной памяти с передачей спинового вращательного момента (STT-MRAM) используют электроны, которые становятся поляризованными по спину при прохождении электронов через тонкую пленку (спиновой фильтр). STT-MRAM также известна, как RAM с передачей спинового вращательного момента (STT-RAM), RAM с Переключением Намагничивания с использованием передачи спинового вращательного момента (Спиновая RAM) и RAM с передачей момента спина (SMT-RAM). При операции записи поляризованные по спину электроны проявляют вращающий момент на свободном слое, который может переключать полярность свободного слоя. Операция считывания подобна обычной MRAM тем, что для обнаружения сопротивления/логического состояния элемента памяти MTJ используют электрический ток, как описано выше. Как иллюстрирует фиг.3A, однобитовая ячейка 300 STT-MRAM содержит MTJ 305, транзистор 310, разрядную шину 320 и числовую шину 330. Транзистор 310 включают и для операций считывания, и для операций записи для обеспечения возможности электрического тока через MTJ 305, так чтобы могло быть считано или записано логическое состояние.

Фиг.3B иллюстрирует более подробную диаграмму ячейки 301 STT-MRAM для дополнительного описания операции считывания/записи. Дополнительно к ранее описанным элементам, таким как MTJ 305, транзистор 310, разрядная шина 320 и числовая шина 330, иллюстрируют шину 340 истока, усилитель 350 считывания, схему 360 считывания записи и опорные данные 370 разрядной шины. Как описано выше, операция записи в STT-MRAM является электрической. Схема 360 считывания/записи создает напряжение записи между разрядной шиной 320 и шиной 340 истока. В зависимости от полярности напряжения между разрядной шиной 320 и шиной 340 истока может быть изменена полярность свободного слоя MTJ 305, и соответственно логическое состояние может быть записано в ячейку 301. Аналогично, при операции считывания, создают электрический ток считывания, который протекает между разрядной шиной 320 и шиной 340 истока через MTJ 305. Когда обеспечена возможность протекания электрического тока через транзистор 310, может быть определено сопротивление (логическое состояние) MTJ 305 на основе разности напряжений между разрядной шиной 320 и шиной 340 истока, которую сравнивают с опорными данными 370 и затем усиливают усилителем 350 считывания. Специалисту в данной области техники будут очевидны функционирование и структура ячейки 301 памяти, которые известны. Обеспечены дополнительные подробности, например, в работе М. Hosomi, и др., A Novel Nonvolatile Memory with Spin Transfer Torque Magnetoresistive Magnetization Switching: Spin-RAM, работы конференции IEDM (2005), которая полностью включена в это описание по ссылке.

Электрическая операция записи STT-MRAM устраняет проблему масштабирования, обусловленную магнитной операцией записи в MRAM. Дополнительно разработка схемы для STT-MRAM является менее сложной. Однако, так как операции считывания и записи выполняют при прохождении электрического тока через MTJ 305, существует возможность разрушения операциями считывания данных, которые хранятся в MTJ 305. Например, если электрический ток считывания подобен или превышает по величине порог электрического тока записи, то существует большая вероятность, что операция считывания может разрушить логическое состояние MTJ 305 и, соответственно, ухудшить целостность памяти.

Сущность изобретения

Возможные варианты осуществления изобретения направлены на системы, схемы и способы для понижения напряжения считывания в магниторезистивной оперативной памяти с передачей спинового вращательного момента (STT-MRAM).

Соответственно, вариант осуществления изобретения может содержать способ разработки магниторезистивной оперативной памяти с передачей спинового вращательного момента (STT-MRAM), содержащий: получение характеристической кривой для транзистора доступа; определение сопротивления состояния 0 и сопротивления состояния 1 туннельного магниторезистивного элемента памяти (MTJ), соответствующих первому и второму состоянию памяти; определение напряжения записи таким образом, чтобы рабочие точки операций записи первого состояния и второго состояния пересекали характеристическую кривую в области насыщения; и определение напряжения считывания таким образом, чтобы рабочие точки операций считывания первого состояния и второго состояния пересекали характеристическую кривую в линейной области.

Память Доступа (STT-MRAM) содержит несколько однобитовых ячеек, каждая однобитовая ячейка содержит: туннельный магниторезистивный элемент памяти (MTJ), имеющий сопротивление состояния 0 и сопротивление состояния 1, соответствующие первому и второму состоянию памяти; транзистор доступа, подсоединенный последовательно с MTJ между разрядной шиной и шиной истока, причем затвор транзистора доступа подсоединен к числовой шине; напряжение питания (VDD) подсоединено к разрядной шине или к шине истока, при операциях записи; и напряжение считывания (VR) подсоединено к разрядной шине при операции считывания, и при этом напряжение считывания выбирают таким образом, чтобы транзистор доступа функционировал в линейной области при операциях считывания, при этом транзистор доступа функционировал в области насыщения при операциях записи.

Другой вариант осуществления изобретения содержит компьютерно-читаемый носитель информации, содержащий сохраненный на нем код для разработки магниторезистивной оперативной памяти с передачей спинового вращательного момента (STT-MRAM), содержащий: код для вызова загрузки компьютером характеристической кривой для транзистора доступа; код для вызова определения компьютером сопротивления состояния 0 и сопротивления состояния 1 туннельного магниторезистивного элемента памяти (MTJ), соответствующих первому и второму состоянию памяти; код для вызова определения компьютером напряжения записи таким образом, чтобы рабочие точки операций записи первого состояния и второго состояния пересекали характеристическую кривую в области насыщения; и код для вызова определения компьютером напряжения считывания таким образом, чтобы рабочие точки операций считывания первого состояния и второго состояния пересекали характеристическую кривую в линейной области.

Краткий перечень чертежей

Приложенные чертежи представлены для облегчения описания вариантов осуществления изобретения и обеспечены исключительно для иллюстрации, а не для ограничения вариантов осуществления.

Фиг.1A и 1B - иллюстрации туннельного магниторезистивного элемента памяти (MTJ).

Фиг.2A и 2B - иллюстрации ячейки магниторезистивной оперативной памяти (MRAM) при операциях считывания и записи, соответственно.

Фиг.3A и 3B - иллюстрации ячеек магниторезистивной оперативной памяти с передачей спинового вращательного момента (STT-MRAM).

Фиг.4A - упрощенное схематическое представление ячейки STT-MRAM.

Фиг.4B - график, иллюстрирующий характеристические кривые для транзистора числовой шины и линию нагрузки, указывающий различные рабочие точки.

фиг.5A - график, иллюстрирующий характеристическую кривую для транзистора числовой шины и линии нагрузки, указывающий различные рабочие точки считывания в области насыщения.

фиг.5B - график, иллюстрирующий характеристическую кривую для транзистора числовой шины и линии нагрузки, указывающий различные рабочие точки считывания в линейной области.

фиг.6A - график, иллюстрирующий характеристическую кривую для транзистора числовой шины и линии нагрузки, указывающий различные рабочие точки записи в области насыщения.

фиг.6B - график, иллюстрирующий характеристическую кривую для транзистора числовой шины и для линии нагрузки, указывающий различные рабочие точки записи в линейной области.

фиг.7 - график, иллюстрирующий характеристическую кривую для транзистора числовой шины и линии нагрузки, указывающий различные рабочие точки считывания и записи.

Фиг.8 - график, иллюстрирующий характеристическую кривую для транзистора числовой шины и линии нагрузки, указывающий различные рабочие точки считывания и записи.

Фиг.9 - блок-схема, иллюстрирующая способ разработки для определения различных рабочих точек однобитовой ячейки STT-MRAM.

Подробное описание изобретения

Аспекты вариантов осуществления изобретения раскрыты в последующем описании и соответствующих чертежах, относящихся к определенным вариантам осуществления изобретения. Не выходя из контекста изобретения, могут быть разработаны дополнительные варианты осуществления. Дополнительно, известные элементы изобретения не будут описаны подробно или будут опущены, чтобы не затенять релевантные подробности вариантов осуществления изобретения.

Используемая здесь терминология предназначена для описания определенных вариантов осуществления, а не для ограничения вариантов осуществления изобретения. Как здесь используют, единственное число предназначено также для охвата множественного числа, если в контексте явно не указано иначе. Дополнительно подразумевается, что термины "содержит", "содержащий", "включает в себя" и/или "включающий в себя" при использовании здесь определяют наличие изложенных признаков, целых величин, этапов, операций, элементов и/или компонентов, но не препятствуют наличию или добавлению одного или большего количества других признаков, целых величин, этапов, операций, элементов, компонентов и/или их групп.

Слово "возможный" используют здесь в значении "служащий примером, возможным вариантом, или иллюстрацией". Любой вариант осуществления, описанный здесь как "возможный", не обязательно должен рассматриваться как предпочтительный или имеющий преимущества перед другими вариантами осуществления. Подобным образом термин "варианты осуществления изобретения" не требует, чтобы все варианты осуществления изобретения содержали описанный признак, преимущество или режим функционирования.

Как описано ранее, в STT-MRAM используют низкий электрический ток записи для каждой ячейки, что является преимуществом этого вида памяти перед MRAM. Однако в обычных разработках электрический ток считывания ячейки может достигать порога электрического тока записи или превышать его и, соответственно, приводить к возникновению недопустимой операции записи/разрушающего считывания.

Согласно фиг.4A иллюстрируют упрощенную схему ячейки STT-MRAM. MTJ представлен сопротивлением (R) 410 и подсоединен последовательно с транзистором 420 доступа между разрядной шиной (BL) и шиной истока (SL). Предполагают, что функционирование ячейки имеет три режима: Выход из строя; Считывание и Запись. Для надлежащего функционирования предпочтительна большая разность электрического тока ячейки между состоянием 0 и состоянием 1. Как описано ранее, в режиме Записи операция записи является двунаправленной операцией для состояния 0 и состояния 1 записи. Низкий электрический ток записи используют для операции малой мощности. Некоторые из проблем разработки для указанной ячейки памяти состоят в том, что операции считывания и записи используют идентичный тракт и являются электрическими. Соответственно, если электрический ток считывания превышает минимальный электрический ток записи, должно происходить разрушающее считывание. Дополнительно, если напряжение через MTJ (например, VM) при операции записи выше, чем Vвыхода из строя, то может возникнуть режим Выхода из строя. Напряжение (V) является суммой напряжения через MTJ (VM) и напряжения истока-утечки (VDS). Напряжение через MTJ может быть определено как:

,

и электрический ток истока-утечки (IDS) может быть определен, как функция напряжения затвора-истока (VGS), напряжения истока-утечки (VDS), порогового напряжения транзистора (Vt), и отношения ширины канала к длине канала (W/L), что может быть задано как:

IDS=f(VGS, VDS, Vt, W/L).

Напряжение затвора-истока (VGS) может быть определено как:

VGS=VWL-VSL,

где VWL является напряжением на числовой шине и VSL является напряжением на шине истока. Напряжение истока-утечки (VDS) может быть определено как:

VDS=VD-VSL,

где VD является напряжением в узле D между MTJ 410 и транзистором 420 доступа. Напряжение (V) также может быть определено как:

V=VBL-VSL,

где VBL является напряжением на разрядной шине. Дополнительно условия для линейной области и для области насыщения транзистора доступа могут быть определены как:

Линейная область: VGS-VT>VDS

Область насыщения: VGS-VT≤VDS

Дополнительно к упрощенной схеме на фиг.4В приведены характеристические кривые для транзистора 420 доступа (или числовой шины). Характеристическими кривыми является семейство кривых, каждая из которых является графиком электрического тока истока-утечки (IDS) относительно напряжения истока-утечки (VDS) для определенного напряжения затвора-истока (VGS). Дополнительно к характеристическим кривым составлен график линии 450 нагрузки. Как можно увидеть из фиг.4B, линия 450 нагрузки пересекает линейную область характеристических кривых в точке 452 и область насыщения в точке 454.

Фиг.5A иллюстрирует линию нагрузки для операции считывания состояния 0, 520 и линию нагрузки для операции считывания состояния 1, 510, для заданного напряжения считывания VR. Линия 520 нагрузки имеет наклон 1/R0, где R0 является сопротивлением состояния 0 MTJ. Подобным образом линия 510 нагрузки имеет наклон 1/R1, где R1 является сопротивлением состояния 1 MTJ. Обе линии пересекают линию напряжения истока-утечки (VDS) в точке VR и пересекают участок насыщения кривой транзистора доступа в точках 512 и 522, соответственно. Так как оба состояния являются рабочими в участке насыщения, электрический ток считывания для состояния 0, по существу, равен электрическому току считывания для состояния 1 (то есть, I0=I1). Соответственно если операция считывания происходит в области насыщения, то будет затруднительно обнаружить состояние MTJ, так как электрические токи считывания для обоих состояний будут подобны.

Функционирование режима считывания может быть разработано так, чтобы существовала существенная разность тока между состоянием 0 и состоянием 1, при ее разработке для использования в линейной области. Фиг.5B иллюстрирует линию нагрузки для операции считывания состояния 0 540 и линию нагрузки для операции считывания состояния 1 530 для заданного напряжения считывания VR и заданного напряжения затвора-истока (VGS). Линия 540 нагрузки имеет наклон 1/R0, где R0 является сопротивлением состояния 0 MTJ. Аналогично линия 530 нагрузки также имеет наклон 1/R1, где R1 является сопротивлением состояния 1 MTJ. Обе линии пересекают линию напряжения истока-утечки в точке VR. Однако в этой конфигурации линии нагрузки пересекают линейный участок кривой транзистора доступа в точках 532 и 542 для R1 и R0, соответственно. При функционировании на линейном участке при операции считывания электрический ток считывания для состояния 0 может быть больше электрического тока считывания для состояния 1 (то есть, I0>I1), как можно заметить из фиг.5B. Может быть достигнута задача разработки, состоящая в наличии существенной разности электрического тока между состоянием 0 и состоянием 1. Соответственно будет проще обнаруживать состояние MTJ на основе различных электрических токов, и могут быть уменьшены ошибки считывания. Разность электрических токов могут увеличивать также другие факторы, такие как меньшее сопротивление состояния «включено» R0n транзистора числовой шины (или доступа). Дополнительно разница между R0 и R1 также будет способствовать увеличению разности электрического тока при операции считывания.

В отличие от операции считывания операция записи может иметь подобную величину электрического тока для каждого состояния и, предпочтительно, имеет по возможности низкий электрический ток записи для уменьшения энергопотребления. Фиг.6A и 6B иллюстрируют линию нагрузки для операции записи. Фиг.6A иллюстрирует линию нагрузки для операции записи состояния 0 620 и линию нагрузки для операции записи состояния 1 610 для заданного напряжения записи VW. Линия 620 нагрузки имеет наклон 1/R0, где R0 является сопротивлением состояния 0 MTJ. Аналогично линия 610 нагрузки имеет наклон 1/R1, где R1 является сопротивлением состояния 1 MTJ. Обе линии пересекают линию напряжения истока-утечки в точке VW и пересекают участок насыщения кривой транзистора числовой шины в точках 612 и 622, соответственно. Так как оба состояния функционируют на участке насыщения, величина электрического тока записи для состояния 0 может быть, по существу, равна величине электрического тока записи для состояния 1 (то есть, IW0=IW1=IW).

В виде варианта фиг.6B иллюстрирует линию нагрузки, которая имеет пересечение в области насыщения для операции записи состояния 0 640, и линию нагрузки для операции записи состояния 1 630, для заданного напряжения записи VW. Линия 640 нагрузки также имеет наклон 1/R0, где R0 является сопротивлением состояния 0 MTJ. Аналогично линия 630 нагрузки имеет наклон 1/R1, где R1 является сопротивлением состояния 1 MTJ. Обе линии пересекают линию напряжения истока-утечки (VDS) в точке VW. Однако в этой конфигурации линии нагрузки пересекают линейный участок кривой транзистора числовой шины в точках 632 и 642 для R1 и R0, соответственно. При функционировании на линейном участке при операции записи величина электрического тока записи для состояния 0 больше величины электрического тока записи для состояния 1 (то есть, IW0>IW1), как может быть заметно из фиг.6B. При операции записи не требуется большая разность электрического тока, соответственно, задача разработки состоит в том, чтобы операция записи происходила в области насыщения транзистора доступа.

Фиг.7 иллюстрирует возможный вариант комбинированных рабочих точек считывания и записи и соответствующие линии нагрузки в возможной разработке. В иллюстрируемом возможном варианте предполагают, что напряжение затвора-истока (VGS) на транзисторе доступа является постоянным, соответственно только одна кривая 700 представляет график для VGS. В этой разработке иллюстрируют линию нагрузки для операции записи состояния 0 720 и линию нагрузки для операции записи состояния 1 710 для заданного напряжения записи, VW. Вновь линия 720 нагрузки имеет наклон 1/R0, где R0 является сопротивлением состояния 0 MTJ. Подобным образом линия 710 нагрузки имеет наклон 1/R1, где R1 является сопротивлением состояния 1 MTJ. Обе линии пересекают линию напряжения (VDS) истока-утечки в точке VW и могут быть разработаны для пересечения области насыщения в точках 712 и 722 для R1 и R0 соответственно. Соответственно может быть получена согласованная величина IW электрического тока записи.

При операции считывания предпочтительно наличие разности электрического тока для различных состояний считывания. Соответственно составлены графики линии нагрузки для операции считывания состояния 0 740 и линии нагрузки для операции считывания состояния 1 730 для заданного напряжения считывания VR. Линия 740 нагрузки также имеет наклон 1/R0, где R0 является сопротивлением состояния 0 MTJ. Подобным образом линия 730 нагрузки также имеет наклон 1/R1, где R1 является сопротивлением состояния 1 MTJ. Ясно, что указанные наклоны, в основном, соответствуют идентичным наклонам для операции записи. Обе линии пересекают линию напряжения утечки при напряжении считывания VR.

При выборе соответствующего напряжения считывания VR линии нагрузки могут пересекать линейный участок кривой 700 транзистора доступа в точках 732 и 742 для R1 и R0 соответственно. При функционировании на линейном участке при операции считывания может быть установлена обнаруживаемая разность между электрическим током считывания для состояния 0 и электрическим током считывания для состояния 1 (то есть, IR0>IR1), как можно заметить из фиг.7.

В возможном варианте, иллюстрируемом фиг.7, достигают по меньшей мере следующие задачи разработки.

• Рабочая точка считывания: Линейная область транзистора доступа

• Рабочая точка записи: Область Насыщения транзистора доступа

• Электрический ток считывания меньше электрического тока записи для предотвращения разрушающих считываний.

Как отмечено выше, операция считывания происходит в линейной области, соответственно, электрический ток считывания для состояния 0 должен быть больше электрического тока считывания для состояния 1 (то есть, I0>I1). Соответственно существенная разность электрического тока между состоянием 0 и состоянием 1 облегчает обнаружение состояния MTJ, и могут быть уменьшены ошибки считывания. Чем больше разность электрического тока между состоянием считывания, тем более гибкой должна быть разработка в отношении изменений процесса, напряжения и температуры (PVT), которые испытывают все схемы. Подобным образом разработка операций записи, которые должны происходить в области насыщения при более высоком электрическом токе, чем все электрические токи считывания (то есть, IW >> I0 > I1), может улучшить допускаемые изменения PVT в отношении описанной выше проблемы разрушающего считывания. Как иллюстрируется, это может быть достигнуто при наличии напряжения записи (VW), большего, чем напряжение считывания (VR). Разность 750 между напряжением записи и напряжением считывания является параметром разработки, который может быть определен на основе ожидаемых изменений PVT и характеристических кривых транзистора доступа для заданной разработки.

Фиг.8 - обобщенный график, иллюстрирующий различные рабочие точки считывания и записи, согласно вариантам осуществления изобретения. Элементы графика могут быть получены из различных параметров разработки ячейки STT-MRAM. Эти параметры, например, содержат сопротивления состояния 0 (R0) и состояния 1 (R1) MTJ и характеристическую кривую для транзистора доступа для заданного напряжения (VGS). Тогда может быть выбрано напряжение записи (VW) для пересечения области насыщения, и напряжение считывания может быть установлено для пересечения линейной области, на основе линий нагрузки записи и считывания. Дополнительно напряжения считывания и записи могут быть установлены для обеспечения того, чтобы максимальный электрический ток считывания (например, IR0) был меньше электрического тока записи (IW), и минимальный электрический ток записи удовлетворял задачам разработки, описанным выше. Минимальный электрический ток записи (IWmin) может быть определен с учетом электрического тока ячейки, изменений сопротивления MTJ, размера ячейки и Vt. Минимальный электрический ток записи может быть установлен большим, чем вычисленный минимальный электрический ток записи.

Простая разработка схемы может быть получена с использованием только одного источника питания (например, напряжения питания (VDD) и земли) и формирования промежуточного напряжения для напряжения считывания (VR). Возможная конфигурация может быть следующей:

• VDD, 0 и VR в качестве уровней напряжения

• VWL=VDD и для считывания и для записи

• VBL=VDD(0) и VSL=0(VDD) для записи

• VBL=VR и VSL=0 для считывания

Выше VDD является напряжением питания, VR является напряжением считывания, VWL является напряжением числовой шины, VBL является напряжением разрядной шины и VSL является напряжением шины истока. Приведенные выше параметры используют только один генератор напряжения DC для VR. Как отмечено выше, напряжение разрядной шины и шины истока подсоединяют к земле (0) или к VDD при операциях записи в зависимости от записываемого состояния. Напряжение шины истока устанавливают в землю (0) при считывании, и разрядную шину устанавливают в VR. Напряжение числовой шины подсоединяют к VDD и для считывания, и для записи, когда это доступно. Соответственно все рабочие состояния могут быть получены с использованием только VDD, VR и земли (0) в качестве уровней напряжения. Соответствующий выбор VDD и VR в комбинации с характеристическими кривыми транзистора доступа может обеспечивать возможность достижения задач разработки, описанных выше (то есть, рабочая точка считывания находится в линейной области транзистора доступа; рабочая точка записи находится в области насыщения транзистора доступа; и электрический ток считывания меньше электрического тока записи) с использованием минимального количества напряжений DC.

Соответственно вариант осуществления изобретения может содержать магниторезистивную оперативную память с передачей спинового вращательного момента (STT-MRAM), имеющую несколько однобитовых ячеек. Каждая ячейка может содержать туннельный магниторезистивный элемент памяти (MTJ), имеющий сопротивление состояния 0, и сопротивление состояния 1, и транзистор доступа, такой как иллюстрирует фиг.4A. Транзистор доступа может быть подсоединен последовательно с MTJ между разрядной шиной и шиной истока. Затвор транзистора доступа может быть подсоединен к числовой шине (WL). При операции записи напряжение питания (VDD) может быть подано на разрядную шину или шину истока. Другая шина (разрядная шина или шина истока), не подсоединенная к VDD, может быть подсоединена к земле для обеспечения возможности операций записи для обоих состояний, как описано выше. При операции считывания напряжение считывания (VR) может быть подано на разрядную шину, и шина истока может быть установлена в землю или 0 вольт. Дополнительно WL может быть подсоединена к VDD и при операциях считывания, и при операциях записи. Как описано выше, напряжение считывания может быть выбрано таким образом, чтобы транзистор доступа функционировал в линейной области при операциях считывания, и напряжение записи (VDD) может быть выбрано так, чтобы транзистор доступа функционировал в области насыщения при операциях считывания.

Ввиду вышеизложенного ясно, что в варианты осуществления изобретения включены способы для выполнения различных последовательностей действий, этапов, функций и/или алгоритмов. Соответственно согласно фиг.9 вариант осуществления изобретения может содержать способ для разработки магниторезистивной оперативной памяти с передачей спинового вращательного момента (STT-MRAM), содержащий: получение характеристической кривой для транзистора доступа, 910. Могут быть определены, 920, сопротивление состояния 0 и сопротивление состояния 1 туннельного магниторезистивного элемента памяти (MTJ), соответствующие первому и второму состоянию памяти. Может быть определено, 930, напряжение записи таким образом, чтобы рабочие точки операций записи первого состояния и второго состояния пересекали характеристическую кривую в области насыщения. Затем может быть определено, 940, напряжение считывания таким образом, чтобы рабочие точки операций считывания первого состояния и второго состояния пересекали характеристическую кривую в линейной области. Дополнительно максимальный электрический ток считывания устанавливают меньшим минимального электрического тока записи.

Дополнительно может быть определено воздействие изменений процесса, напряжения и температуры (PVT) по множеству однобитовых ячеек в матрице памяти. Каждая однобитовая ячейка содержит MTJ, транзистор доступа и подобные напряжения записи и напряжения считывания. Соответственно может быть сделана оценка воздействия изменений PVT и может быть сделана оценка разработки для обеспечения ее успешного действия по ожидаемому диапазону изменений, который может быть определен из информации, легко доступной для разработчиков (например, характеристических кривых для различных разработок транзистора доступа), и посредством ограничений, наложенных разработчиками (например, минимальных и максимальных рабочих напряжения и температуры). Если исходная разработка определена недопустимой, то, например, может быть проведена корректировка по меньшей мере одного из сопротивления состояния 0, сопротивления состояния 1, напряжения записи или напряжения считывания, на основе определенного воздействия изменений PVT, и может быть повторен процесс фиг.9. Дополнительно может быть рассмотрена другая разработка транзистора доступа с другими характеристическими кривыми. Соответственно разработка памяти может быть определена таким образом, чтобы каждая из множества однобитовых ячеек имела операции записи, которые пересекают характеристическую кривую в области насыщения, и каждая из операций считывания пересекала характеристическую кривую в линейной области.

Способы, последовательности и/или алгоритмы, описанные в связи с раскрытыми здесь вариантами осуществления, могут быть реализованы непосредственно в аппаратных средствах, в программном модуле, выполняемом процессором или в их комбинации. Программный модуль может быть размещен в памяти RAM, флэш-памяти, памяти ROM, памяти EPROM, памяти EEPROM, регистрах, на жестком диске, съемном диске, CD-ROM или любом другом виде известного носителя информации. Возможный носитель информации подсоединяют к процессору таким образом, чтобы процессор мог считывать информацию с носителя информации или записывать информацию на него. В виде варианта носитель информации может быть встроенным в процессор. Процессор и носитель информации могут быть размещены в ASIC. ASIC может быть размещена в пользовательском терминале. В виде варианта процессор и носитель информации могут быть размещены в виде дискретных компонентов в пользовательском терминале. Соответственно вариант осуществления изобретения может содержать пользовательский терминал, сконфигурированный для выполнения процессов разработки, описанных выше.

В одном или большем количестве возможных вариантов осуществления описанные функции могут быть реализованы в аппаратных средствах, программном обеспечении, встроенном программном обеспечении или в любой их комбинации. При реализации в программном обеспечении функции в виде одной или большего количества инструкций или в виде кода могут быть сохранены на компьютерно-читаемом носителе информации, или переданы на компьютерно-читаемый носитель информации. Компьютерно-читаемые носители информации содержат и носители информации памяти компьютера, и носители информации средств связи, включая в себя любую передающую среду, которая способствует передаче компьютерной программы из одного места в другое. Носителями информации могут быть любые доступные носители информации, к которым может осуществить доступ компьютер. В виде возможного варианта, а не ограничения, такие компьютерно-читаемые носители информации могут содержать RAM, ROM, EEPROM, CD-ROM или другую оптическую память на диске, магнитную память на диске или д