Способ изготовления инвертора и инвертор

Иллюстрации

Показать всеИзобретение относится к инвертору, состоящему из тонкопленочных транзисторов с оксидным полупроводниковым слоем. Сущность изобретения: способ изготовления инвертора, работающего в режиме обогащения/обеднения (E/D), имеющего множество тонкопленочных транзисторов на одной и той же подложке, канальные слои которых состоят из оксидного полупроводника, содержащего по меньшей мере один элемент, выбранный из In, Ga и Zn, содержит этапы, на которых формируют первый транзистор и второй транзистор, толщина канальных слоев первого и второго транзисторов является взаимно различной, и применяют термообработку по меньшей мере к одному из канальных слоев первого и второго транзисторов. Изобретение обеспечивает расширение технических средств, позволяющих получить инвертор с оксидными полупроводниковыми тонкопленочными транзисторами, имеющими различные пороговые напряжения, упрощение способа получения инвертора с такими характеристиками, снижение его стоимости. 3 н. и 10 з.п. ф-лы, 18 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение имеет отношение к инвертору, который состоит из тонкопленочного транзистора, содержащего оксидный полупроводниковый слой в качестве канального слоя. Кроме того, настоящее изобретение имеет отношение к интегральной схеме, которая содержит соответствующий инвертор.

УРОВЕНЬ ТЕХНИКИ

Соединительные платы тонкопленочных транзисторов (TFT), на которых транзисторы TFT размещаются в виде массива на подложках, представляют собой части основы для различных видов жидкокристаллических дисплеев с активной матрицей, таких как дисплей на жидких кристаллах, дисплей на органических светодиодах (OLED) и т.п. В жидкокристаллическом дисплее с активной матрицей транзистор TFT управляет электрооптическим прибором, соответствующим каждому пикселю, для отображения желаемой информации. В качестве транзистора TFT для такой цели рассматривается транзистор TFT на основе низкотемпературного поликристаллического кремния (LTPS), транзистор TFT на основе гидрогенизированного аморфного кремния (a-Si:H) и т.п.

Кроме того, рассматривается технология для одновременного производства транзисторов TFT, соответственно имеющих различные функции, на одной и той же подложке в качестве соединительной платы. Более конкретно, в этой технологии транзистор TFT (схема пикселя) для управления электрооптическим прибором каждого пикселя и периферийные схемы, такие как драйвер затвора, драйвер истока и т.п., состоящие из транзисторов TFT, изготовляются одновременно на одной и той же подложке. В этом случае, поскольку функция транзистора TFT является различной в зависимости от каждого блока схемы, такого как схема пикселя, периферийная схема и т.п., желательно отрегулировать пороговое напряжение транзистора TFT для каждого блока схемы. Например, следует отметить, что большое пороговое напряжение, подходящее для порога инвертирования электрооптического прибора, желательно в схеме пикселя, а малое пороговое напряжение желательно для сдерживания потребления энергии в периферийной схеме. На таком уровне техники опубликованная заявка на патент Японии № 2005-072461 раскрывает способ регулировки пороговых напряжений транзисторов TFT в соответствии с блоками пикселей в схемах транзисторов TFT на основе LTPS, изготовленных с использованием отжига с помощью эксимерного лазера (ELA).

Периферийные схемы включают в себя цифровые схемы, такие как сдвиговый регистр и т.п. При этом следует отметить, что в случае изготовления цифровой схемы с транзисторами TFT следующие четыре структуры (1)-(4) могут быть использованы в качестве логического элемента "НЕ" (инвертора). Структура (1) представляет собой активную нагрузку, структура (2) представляет собой обогащение/обогащение (E/E), структура (3) представляет собой обогащение/обеднение (E/D), и структура (4) представляет собой комплементарный металл-оксидный полупроводник (CMOS). В общем случае структура E/D или структура CMOS часто применяется с целью сокращения области размещения и достижения работы с большой скоростью. Кстати говоря, для эффективной работы инвертора со структурой обогащения/обеднения необходимо управлять пороговым напряжением транзистора TFT таким образом, чтобы сделать разность между пороговыми напряжениями двух транзисторов TFT, составляющих инвертор, достаточно большой. С другой стороны, поскольку для инвертора со структурой CMOS необходим и транзистор TFT с каналом n-типа, и транзистор TFT с каналом p-типа, требуются соответствующие процессы легирования для каждого транзистора TFT, что приводит к большему количеству процессов фотолитографии по сравнению с другими структурами.

В качестве потенциально возможных вариантов эффективных транзисторов TFT для использования вместо транзисторов TFT на основе LTPS или a-Si:H были активно исследованы и разработаны транзисторы TFT (оксидные транзисторы TFT), в которых в качестве канального слоя используются слои из оксидных полупроводников. При этом способ изготовления оксидного транзистора TFT с использованием тонкой пленки, полученной радиочастотным магнетронным распылением, из аморфного оксида индия-галлия-цинка (In-Ga-Zn-O; IGZO) в качестве канального слоя раскрывается в документе "Appl. Phys. Lett. 89, 112123 (2006)". Многие виды оксидных полупроводников с высокой подвижностью носителей тока, такие как аморфный IGZO и т.п., имеют проводимость n-типа (электронную), но не приобретают проводимость p-типа (дырочную) даже при легировании, поэтому структура CMOS не может быть использована. Однако оксидный транзистор TFT имеет следующие два преимущества. Так, (1) подвижность носителей тока оксидного транзистора TFT гораздо выше, чем подвижность носителей тока транзистора TFT на основе a-Si:H. Поэтому документ "IEEE Elec. Dev. Lett., 28, p.273 (2007)" раскрывает, что даже если используется инвертор с насыщенной нагрузкой, работающий в режиме обогащения/обогащения, который неудобен с точки зрения скорости работы, может быть достигнута работа с большой скоростью, которая превышает скорость работы инвертора с транзистором TFT на основе a-Si:H. Кроме того, (2) для канального слоя доступно осаждение методом распыления. Таким образом, поскольку исходная стеклянная подложка может быть увеличена, можно ожидать понижение стоимости изготовления в соответствии с увеличением подложки.

Кроме того, в следующих документах раскрываются различные способы управления пороговым напряжением для оксидного транзистора TFT. Во-первых, публикация заявки на патент США № US-2006-0113565 раскрывает транзистор TFT, который включает в себя In, Ga, Zn и O в качестве своих составных элементов и использует в качестве канального слоя прозрачную аморфную оксидную тонкую пленку, концентрация электронных носителей которой составляет меньше чем 1018 см-3, и интегральную схему, которая использует соответствующие транзисторы TFT. Кроме того, этот документ упоминает использование транзистора TFT, работающего в режиме обеднения (D), но не упоминает конкретный способ управления напряжением Vth в транзисторе TFT.

Публикация заявки на патент США № US-2006-0244107 раскрывает способ управления напряжением Vth в транзисторе TFT, который использует оксид цинка (ZnO) в качестве канального слоя, посредством введения легирующего вещества в атмосферу осаждения канального слоя.

Кроме того, документ "BARQUINHA ET AL: "Influence of the semiconductor thickness on the electrical properties of transparent TFTs based on indium zinc oxide" JOURNAL OF NONCRYSTALLINE SOLIDS, NORTH-HOLLAND PHYSICS PUBLISHING. AMSTERDAM, NL, vol. 352, no. 9-20, 15 June 2006 (2006-06-15), pages 1749-1752, XP005482522 ISSN: 0022-3093 figure 3" раскрывает, что в транзисторе TFT, который использует ZnO в качестве материала канального слоя, напряжение Vth регулируется посредством толщины осажденного канального слоя.

Кроме того, документ "Journal of Applied physics, 97, p.064505 (2005)" раскрывает, что в транзисторе TFT, который использует оксид цинка-индия (Zn-In-O) в качестве материала канального слоя, напряжение Vth регулируется посредством температуры термической обработки.

В любом случае все документы множества, состоящего из публикации заявки на патент США № US-2006-0244107, документа "Solid State Electronics, 352(9-20), p.1749 (2006)" и документа "Journal of Applied physics, 97, p.064505 (2005)", раскрывают, что характеристики транзисторов TFT, соответственно изготовленных на разных подложках при различных условиях, отличаются друг от друга. Однако ни один из этих документов не раскрывает конкретный способ изготовления на одной и той же подложке транзисторов TFT, каждый из которых имел бы свое напряжение Vth.

В способе, раскрытом в опубликованной заявке на патент Японии № 2005-072461, недорогое изготовление цифровой схемы с транзисторами TFT является сложным по следующим двум причинам.

Во-первых, транзистор TFT, раскрытый в этом документе, является транзистором TFT на основе LTPS. Другими словами, поскольку стоимость увеличивается из-за увеличения самого прибора отжига с помощью эксимерного лазера (ELA), даже если увеличивается исходная стеклянная подложка, преимущество стоимости производства в соответствии с увеличением подложки является малым. Во-вторых, невозможно получить инвертор, работающий в режиме обогащения/обеднения, который эффективно работает, поскольку разность пороговых напряжений транзисторов TFT, полученная в способе, раскрытом в этом документе, слишком мала. Поэтому инвертор, раскрытый в этом документе, имеет структуру CMOS и процесс фотолитографии усложняется по сравнению с другими структурами, посредством чего стоимость увеличивается.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Настоящее изобретение имеет своей целью решить описанные выше проблемы. Настоящее изобретение характеризуется способом изготовления инвертора, работающего в режиме обогащения/обеднения (E/D), имеющего множество тонкопленочных транзисторов на одной и той же подложке, канальные слои упомянутых транзисторов состоят из оксидного полупроводника, содержащего по меньшей мере один элемент, выбранный из In, Ga и Zn, и способ содержит этапы: формирования первого транзистора и второго транзистора, толщина канальных слоев первого и второго транзисторов различны; и применения термообработки по меньшей мере к одному из канальных слоев первого и второго транзисторов.

Кроме того, настоящее изобретение характеризуется способом изготовления инвертора, работающего в режиме обогащения/обеднения (E/D), имеющего множество тонкопленочных транзисторов на одной и той же подложке, канальные слои упомянутых транзисторов состоят из оксидного полупроводника, содержащего по меньшей мере один элемент, выбранный из In, Ga и Zn, и способ содержит этапы: формирования общей осажденной пленки, действующей в качестве канального слоя первого транзистора и канального слоя второго транзистора; и выполнения термообработки посредством приложения большего количества тепла к какому-либо одному из канальных слоев первого транзистора и второго транзистора.

Кроме того, настоящее изобретение отличается тем, что среди множества оксидных полупроводниковых тонкопленочных транзисторов, которые сформированы на одной и той же подложке и каждый из которых содержит по меньшей мере один элемент, выбранный из In, Ga и Zn, толщина канальных слоев по меньшей мере двух транзисторов является взаимно различной, и пороговые напряжения двух транзисторов являются взаимно различными.

В соответствии с настоящим изобретением возможно относительно легко изготовить оксидные полупроводниковые тонкопленочные транзисторы, соответственно имеющие различные пороговые напряжения, на одной и той же подложке с использованием характеристик оксидного полупроводникового тонкопленочного транзистора. Например, соответствующие характеристики включают в себя такую характеристику, что разность пороговых напряжений возникает вследствие разности толщины канальных слоев, и такую характеристику, что разность пороговых напряжений возникает вследствие различия условий термообработки канальных слоев. Даже если используется какая-либо одна из этих двух характеристик, возможно существенно увеличить разность пороговых напряжений, посредством чего инвертор, работающий в режиме обогащения/обеднения, функционирует эффективно.

Дополнительные отличительные признаки настоящего изобретения станут понятны на основе последующего описания иллюстративных вариантов воплощения со ссылкой на приложенные чертежи.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Сопроводительные чертежи, которые включены в описание и составляют его часть, иллюстрируют варианты воплощения изобретения и вместе с описанием служат для разъяснения принципов изобретения.

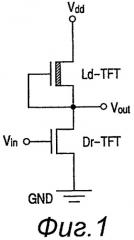

Фиг.1 - принципиальная схема инвертора, работающего в режиме обогащения/обеднения.

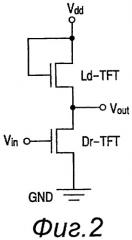

Фиг.2 - принципиальная схема инвертора с насыщенной нагрузкой, работающего в режиме обогащения/обогащения.

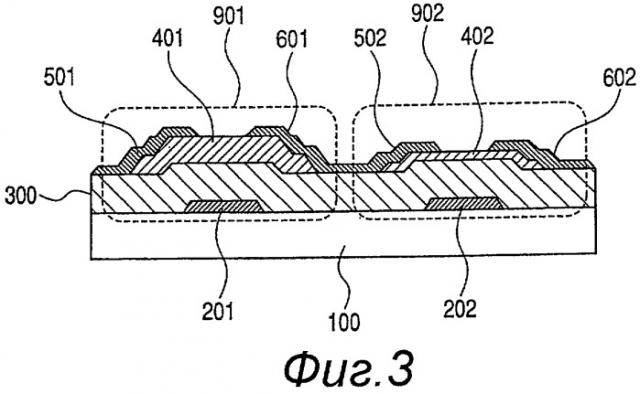

Фиг.3 - изображение поперечного разреза первого варианта воплощения.

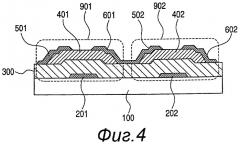

Фиг.4 - изображение поперечного разреза второго варианта воплощения.

Фиг.5 - изображение, показывающее результат оценки (моделирования) эффективного условия изготовления инвертора, работающего в режиме обогащения/обеднения.

Фиг.6 - изображение поперечного разреза изготовленного транзистора TFT.

Фиг.7A, 7B, 7C, 7D, 7E, 7F, 7G и 7H - изображения, показывающие характеристическую зависимость Ids-Vgs изготовленного транзистора TFT.

Фиг.8 - изображения поперечных разрезов, показывающие процесс изготовления инвертора, работающего в режиме обогащения/обеднения, в варианте воплощения 1, варианте воплощения 4 и сравнительном примере 4-1.

Фиг.9 - изображение, показывающее выходную форму сигнала модели кольцевого генератора, составленного из инверторов, работающих в режиме обогащения/обеднения, в варианте воплощения 1.

Фиг.10 - изображения поперечных разрезов, показывающие процесс изготовления инвертора с насыщенной нагрузкой, работающего в режиме обогащения/обогащения, в сравнительном примере 1-1 и сравнительном примере 4-2.

Фиг.11 - изображение, показывающее выходную форму сигнала модели кольцевого генератора, составленного из инверторов с насыщенной нагрузкой, работающих в режиме обогащения/обогащения, в сравнительном примере 1-1.

Фиг.12 - изображения поперечных разрезов, показывающие процесс изготовления инвертора с насыщенной нагрузкой, работающего в режиме обогащения/обогащения, в сравнительном примере 1-2.

Фиг.13 - изображения поперечных разрезов, показывающие процесс изготовления инвертора, работающего в режиме обогащения/обеднения, в варианте воплощения 3.

Фиг.14 - изображение, показывающее выходную форму сигнала модели кольцевого генератора, составленного из инверторов, работающих в режиме обогащения/обеднения, в варианте воплощения 3.

Фиг.15 - изображение, показывающее выходную форму сигнала модели кольцевого генератора, составленного из инверторов с насыщенной нагрузкой, работающих в режиме обогащения/обогащения, в сравнительном примере 3-1.

Фиг.16 - изображение, показывающее выходную форму сигнала модели кольцевого генератора, составленного из инверторов, работающих в режиме обогащения/обеднения, в варианте воплощения 4.

Фиг.17 - изображение, показывающее выходную форму сигнала модели кольцевого генератора, составленного из инверторов с насыщенной нагрузкой, работающих в режиме обогащения/обогащения, в сравнительном примере 4-1.

Фиг.18 - изображение, показывающее выходную форму сигнала модели кольцевого генератора, составленного из инверторов с насыщенной нагрузкой, работающих в режиме обогащения/обогащения, в сравнительном примере 4-2.

ПРЕДПОЧТИТЕЛЬНЫЙ ВАРИАНТ ВОПЛОЩЕНИЯ ИЗОБРЕТЕНИЯ

Теперь будут подробно описаны иллюстративные варианты воплощения настоящего изобретения со ссылкой на сопроводительные чертежи.

На фиг.1 показана принципиальная схема инвертора, работающего в режиме обогащения/обеднения (E/D), который может быть изготовлен в соответствии с настоящим изобретением. В инверторе, работающем в режиме обогащения/обеднения, используется одна часть тонкопленочного транзистора (TFT), работающего в режиме обогащения (в режиме E), и одна часть транзистора TFT, работающего в режиме обеднения (в режиме D). Напряжение источника питания подается извне как разность потенциалов между напряжением Vdd и заземлением GND. Электрод истока транзистора TFT, работающего в режиме обеднения, и электрод стока транзистора TFT, работающего в режиме обогащения, соединены друг с другом, и электрод затвора транзистора TFT, работающего в режиме обеднения, соединен с электродом истока транзистора TFT, работающего в режиме обеднения. Электрод стока транзистора TFT, работающего в режиме обеднения, соединен с точкой Vdd напряжения источника питания, и электрод истока транзистора TFT, работающего в режиме обогащения, соединен с заземлением. Также электрод затвора транзистора TFT, работающего в режиме обогащения, служит точкой входа, и электрод стока транзистора TFT, работающего в режиме обогащения, служит точкой выхода.

В принципе выходное напряжение инвертора, работающего в режиме обогащения/обеднения, во время высокого уровня выходного сигнала повышается до напряжения, эквивалентного напряжению источника питания. Поэтому инвертор, работающий в режиме обогащения/обеднения, имеет такой отличительный признак, что амплитуда выходного напряжения является широкой и время нарастания выходного напряжения является быстрым.

С другой стороны, на фиг.2 показана принципиальная схема инвертора с насыщенной нагрузкой, работающего в режиме обогащения/обогащения, в котором и нагрузочный транзистор TFT, и управляющий транзистор TFT работают в режиме обогащения. Аналогично инвертору, работающему в режиме обогащения/обеднения, напряжение источника питания подается извне как разность потенциалов между напряжением Vdd и заземлением.

При сравнении этих двух типов инверторов друг с другом инвертор, работающий в режиме обогащения/обеднения, может управлять нагрузочной емкостью на более высокой скорости с большей амплитудой.

В транзисторе TFT, когда напряжение Vds между стоком и истоком существенно больше, чем напряжение Vgs между затвором и истоком, транзистор TFT работает в области насыщения и ток Ids между стоком и истоком представлен следующим выражением:

Ids=(W·Ci·µ/2L)·(Vgs-Vth)2 (1)

Здесь L обозначает длину канала (мкм), W обозначает ширину канала (мкм), Ci обозначает емкость диэлектрика затвора (Ф/см2), µ обозначает подвижность носителей полевого эффекта (см2/В·с), и Vth обозначает пороговое напряжение (В).

Хотя существуют несколько способов экспериментального получения значений µ и Vth, ниже будет описан один из способов. В транзисторе TFT квадратный корень от тока Ids в течение периода, пока изменяется напряжение Vgs и подается постоянное напряжение Vds, существенно большее, чем напряжение Vgs, наносится на график как функция от напряжения Vgs. Значения µ и Vth могут быть получены из градиента и отрезка касательной линии, проведенной в точке произвольного напряжения Vgs на этом графике. Касательная линия также может быть проведена в точке напряжения Vgs, где производная предшествующего графика становится максимальной, или в точке напряжения Vgs, которое фактически должно быть приложено к транзистору TFT. Считается, что в последнем случае могут быть получены фактические значения µ и Vth вблизи от напряжения Vgs.

Одно определение транзисторов TFT, работающих в режимах обогащения и обеднения, для упрощения будет описано посредством иллюстрации транзистора TFT с каналом n-типа. Транзистор TFT может называться работающим в режиме обогащения (E), если его ток Ids достаточно мал при напряжении Vgs=0, и поэтому он может рассматриваться как находящийся в закрытом состоянии. Наоборот, транзистор TFT, который имеет конечный ток Ids при напряжении Vgs=0 в транзисторе TFT с каналом n-типа и к которому должно быть приложено отрицательное напряжение Vgs в качестве обратного смещения, чтобы привести транзистор TFT в закрытое состояние, называют работающим в режиме обеднения (D). Эквивалентно транзисторы TFT, работающие в режимах обогащения и обеднения, могут быть определены с использованием напряжения Von включения, которое является напряжением Vgs, при котором ток Ids начинает увеличиваться, пока напряжение Vgs изменяется от значения, в котором транзистор TFT находится в закрытом состоянии. Транзистор TFT, имеющий положительное напряжение Von, может быть определен как работающий в режиме обогащения, и транзистор TFT, имеющий отрицательное напряжение Von, может быть определен как работающий в режиме обеднения. Вместо приведенного выше определения также можно определить, что транзистор TFT, имеющий в значительной степени положительное напряжение Vth, является работающим в режиме обогащения, и транзистор TFT, имеющий в значительной степени отрицательное напряжение Vth, соответственно является работающим в режиме обеднения.

Хотя приведенное выше описание было дано с использованием транзистора TFT с каналом n-типа, аналогично приведенному выше описанию также могут быть рассмотрены различные определения, относящиеся к режимам обогащения и обеднения в транзисторе TFT с каналом p-типа.

Далее определяется, что транзистор TFT с каналом n-типа, обычно имеющий положительное напряжение Vth, является работающим в режиме обогащения, и транзистор TFT с каналом n-типа, в значительной степени имеющий отрицательное напряжение Vth, является работающим в режиме обеднения. Однако в случае использования двух транзисторов TFT с каналом n-типа, имеющих положительное напряжение, инвертор также может быть задан посредством рассмотрения транзистора TFT на одной стороне как работающего в режиме обеднения, а не обогащения, когда имеется большая разность между двумя напряжениями Vth.

(Первый вариант воплощения)

На фиг.3 показана часть поперечного разреза инвертора в соответствии с первым вариантом воплощения настоящего изобретения.

Первый транзистор TFT 901 и второй транзистор TFT 902 изготовлены на подложке 100.

Первый транзистор TFT 901 содержит первый электрод 201 затвора, изолирующий слой 300, первый канальный слой 401, первый электрод 501 стока и первый электрод 601 истока.

Второй транзистор TFT 902 содержит второй электрод 202 затвора, изолирующий слой 300, второй канальный слой 402, второй электрод 502 стока и второй электрод 602 истока.

При этом изолирующий слой 300 целиком встроен в первый транзистор TFT 901 и второй транзистор TFT 902. Однако он может быть встроен отдельно в каждый транзистор TFT.

Первый электрод 601 истока и второй электрод 502 стока соединены друг с другом. Первый электрод 201 затвора соединен с первым электродом 601 истока посредством проводного соединения (не показано).

Когда первый электрод 501 стока соединен с точкой Vdd напряжением источника питания и второй электрод 602 истока соединен с землей, получается инвертор, работающий в режиме обогащения/обеднения, в котором второй электрод 202 затвора служит точкой входа, и второй электрод 502 стока служит точкой выхода.

Таким образом, первый транзистор, который является одним транзистором, становится работающим в режиме обеднения, и второй транзистор, который является другим транзистором, работает в режиме обогащения.

Первый канальный слой 401 является более толстым, чем второй канальный слой 402. Таким образом, после изготовления канальных слоев, имеющих различную толщину относительно друг друга, весь прибор целиком подвергается нагреванию на произвольной стадии изготовления. В результате этого процесса первый транзистор TFT 901 и второй транзистор TFT 902 имеют различные значения напряжения Vth относительно друг друга.

Чтобы отрегулировать толщину канальных слоев 401 и 402, после формирования общей осажденной пленки, состоящей из оксидного полупроводника, который становится канальными слоями 401 и 402, может быть выполнен процесс сухого травления или процесс жидкостного травления. Таким образом, при использовании травления, поскольку достигается формирование канального слоя только за один раз, стоимость изготовления может быть уменьшена.

Кроме того, также может быть использован метод обратной литографии. Таким образом, толщина пленки также может регулироваться посредством повторного формирования канального слоя после применения фоторезиста на верхнем участке канального слоя для режима обогащения после изготовления канального слоя, толщина которого соответствует толщине канального слоя для режима обогащения, который является вторым канальным слоем 402, на всей поверхности. При промывании всей структуры на подложке могут быть получены канальные слои, имеющие два вида толщины. Этот случай предпочтителен, поскольку возможность регулирования толщины пленки является высокой для каждого канального слоя.

(Второй вариант воплощения)

На фиг.4 показана часть поперечного разреза инвертора в соответствии со вторым вариантом воплощения настоящего изобретения.

Первый транзистор TFT 901 и второй транзистор TFT 902 изготовлены на подложке 100.

Первый транзистор TFT 901 содержит первый электрод 201 затвора, изолирующий слой 300, первый канальный слой 401, первый электрод 501 стока и первый электрод 601 истока.

Второй транзистор TFT 902 содержит второй электрод 202 затвора, изолирующий слой 300, второй канальный слой 402, второй электрод 502 стока и второй электрод 602 истока.

Первый электрод 601 истока и второй электрод 502 стока соединены друг с другом. Первый электрод 201 затвора соединен с первым электродом 601 истока посредством проводного соединения (не показано).

Когда первый электрод 501 стока соединен с точкой Vdd напряжением источника питания и второй электрод 602 истока соединен с землей, получается инвертор, работающий в режиме обогащения/обеднения, в котором второй электрод 202 затвора служит точкой входа, и второй электрод 502 стока служит точкой выхода.

Таким образом, первый транзистор, который является одним транзистором, становится работающим в режиме обеднения, и второй транзистор, который является другим транзистором, работает в режиме обогащения.

Толщина первого канального слоя 401 приблизительно равна толщине второго канального слоя 402. Первый транзистор TFT 901 и второй транзистор TFT 902 должны иметь различные значения Vth посредством избирательного выполнения процесса нагревания для канального слоя 401 первого транзистора TFT по сравнению с процессом, который должен быть выполнен для канального слоя 402 второго транзистора TFT.

В настоящем изобретении факт избирательного выполнения процесса нагревания означает контроль над тем, что нагревание локально (избирательно/интенсивно) применяется только к заданному участку (также называемому областью), предварительно зафиксированному на подложке. Например, имеется способ локального нагревания только заданного участка. Однако имеется случай, в котором часть теплоты передается участку, отличающемуся от заданного участка, когда процесс нагревания выполняется над заданным участком, но в настоящем изобретении, если влияние (на качество пленки) переданной теплоты находится на незначительном уровне, такое влияние является допустимым. При необходимости является эффективным обеспечить блок охлаждения, чтобы подавить влияние передачи части теплоты участку, отличающемуся от заданного участка, когда процесс нагревания выполняется над заданным участком. Оптимальное значение температуры и времени выдержки каждого транзистора TFT изменяется в зависимости от состава или толщины каждого оксидного полупроводникового слоя первого транзистора TFT и второго транзистора TFT.

Как известно авторам настоящего изобретения, с учетом условий термической обработки и эффекта в случае изготовления оксидной полупроводниковой тонкой пленки, имеющей состав "In (индий):Ga (галлий):Zn (цинк)=1:0,9:0,6", с условием, которое будет описано позже, выявляется следующая зависимость. Таким образом, может быть получен постоянный эффект, например, посредством выдержки первого транзистора TFT в течение десяти минут или более при температуре 200°C и выдержки второго транзистора TFT при температуре 120°C или менее.

Чтобы выборочно нагреть только первый транзистор TFT, могут быть использованы различные способы локального нагревания с использованием контактного нагревания и нагревания посредством облучения электромагнитными волнами (облучения высокочастотными волнами, облучения ультрафиолетовыми лучами, облучения лазерным лучом и т.п.).

В настоящем изобретении упомянутые выше электромагнитные волны включают в себя радиочастотные волны, высокочастотные волны, такие как микроволны, ультрафиолетовые лучи, видимые лучи, инфракрасные лучи, рентгеновские лучи и гамма-лучи.

В настоящем изобретении избирательное нагревание может быть достигнуто посредством выполнения индукционного нагревания с использованием удельного сопротивления или удельной теплоемкости различных материалов и разности коэффициентов поглощения при заданной длине волны.

Выполнение индукционного нагревания, поскольку разность количества теплоты становится больше в зависимости от способа выбора материалов, является предпочтительным, поскольку напряжение Vth может эффективно регулироваться для каждого транзистора TFT.

Кроме того, при использовании разности коэффициентов поглощения в зависимости от материалов заданный транзистор TFT может быть избирательно нагрет также посредством общего нагревания, такого как нагревание с помощью импульсной лампы. А именно, для структурных материалов (электрода затвора, электродов истока/стока) электрода заданного транзистора TFT используются вещества, отличающиеся от структурных материалов электрода, соответствующего другому транзистору TFT. Посредством обеспечения такой структуры заданный транзистор TFT может быть избирательно нагрет посредством выполнения общего оптического облучения при использовании импульсной лампы и т.п. Этот процесс реализуется, поскольку только участок электрода, сформированный из материала, имеющего высокий коэффициент поглощения, выборочно поглощает оптическую энергию для нагревания этого участка. В частности, предпочтительно оптическое облучение импульсной лампой, поскольку нагревающее устройство является простым.

При этом, чтобы управлять температурой заданного транзистора TFT, для материалов, отличающихся от структурных материалов транзистора TFT, может быть назначен светопоглощающий материал или светоотражающий материал. Кроме того, при необходимости может быть использована оптическая система, такая как фокусировка, проецирование или сканирование света. Кроме того, в случае, когда имеется риск изменения качества пленки вследствие того, что теплота избирательно нагретого участка передается смежной части, также при необходимости может быть обеспечен блок охлаждения.

Другими словами, в вариантах воплощения настоящего изобретения является предпочтительным, что упомянутый выше инвертор имеет по меньшей мере любой вид структуры среди следующих пунктов от A до C.

A: Структура, в которой структурный материал электрода истока упомянутого выше первого транзистора отличается от структурного элемента электрода истока упомянутого выше второго транзистора.

B: Структура, в которой структурный материал электрода стока упомянутого выше первого транзистора отличается от структурного элемента электрода стока упомянутого выше второго транзистора.

C: Структура, в которой структурный материал электрода затвора упомянутого выше первого транзистора отличается от структурного элемента электрода затвора упомянутого выше второго транзистора.

Кроме того, является предпочтительным, что этап термической обработки включает в себя процесс нагревания посредством облучения электромагнитными волнами. Кроме того, в вариантах воплощения настоящего изобретения является предпочтительным, что упомянутый выше инвертор имеет по меньшей мере любой вид структуры среди следующих пунктов от D до F.

D: Структура, в которой физический параметр структурного материала электрода истока упомянутого выше первого транзистора отличается от физического параметра электрода истока упомянутого выше второго транзистора.

E: Структура, в которой физический параметр структурного материала электрода стока упомянутого выше первого транзистора отличается от физического параметра электрода стока упомянутого выше второго транзистора.

F: Структура, в которой физический параметр структурного материала электрода затвора упомянутого выше первого транзистора отличается от физического параметра электрода затвора упомянутого выше второго микротранзистора.

Далее является предпочтительным, что упомянутый выше физический параметр является по меньшей мере одним из свойств, выбранных из удельного сопротивления, удельной теплоемкости и коэффициентов поглощения.

(Третий вариант воплощения)

Как показано в первом варианте воплощения, после изготовления канальных слоев, имеющих различную толщину, условия процесса нагревания первого канального слоя делаются отличными от условий для второго канального слоя, как в способе, описанном во втором варианте воплощения, когда термический процесс выполняется в произвольном процессе изготовления.

В результате этого способа первый транзистор TFT 901 и второй транзистор TFT 902 имеют различные значения напряжения Vth.

Чтобы эффективно эксплуатировать инвертор, работающий в режиме обогащения/обеднения, в соответствии с настоящим изобретением, будет описан подходящий диапазон как разность между пороговыми напряжениями двух видов транзисторов. Фиг.5 является изображением, показывающим результат сравнения колебательных характеристик 31-каскадного кольцевого генератора на основе инверторов с насыщенной нагрузкой, работающих в режиме обогащения/обогащения, с колебательными характеристиками 31-каскадного кольцевого генератора на основе инверторов, работающих в режиме обогащения/обеднения, выполненных посредством способа моделирования с помощью программы SPICE (программы моделирования с акцентом на интегральные схемы). В правой части фиг.5 показана оценка, которая получена посредством изменения напряжения Vth нагрузочного транзистора TFT при каждых условиях геометрического соотношения β, отношения подвижности носителей тока, напряжения Vdd источника питания и напряжения Vth управляющего транзистора TFT, работающего в режиме обогащения, указанных в левой стороне фиг.5. Здесь геометрическое соотношение β представляет собой соотношение отношения (ширина W/длина L) управляющего транзистора TFT и отношения (ширина W/длина L) нагрузочного транзистора TFT. Отношение подвижности представляет собой отношение подвижности управляющего транзистора TFT и подвижности нагрузочного транзистора TFT. Следует отметить, что длина канала была задана равной L=10 мкм во всех транзисторах TFT. Что касается ширины канала, она была задана равной W=40 мкм в нагрузочных транзисторах TFT и W=40×β мкм в управляющих транзисторах TFT. Длина перекрытия затвора каждого транзистора TFT была задана равной 5 мкм, и учитывалась только паразитная емкость, вызванная этим перекрытием.

Согласно фиг.5, в случае когда напряжение Vth нагрузочного транзистора TFT удовлетворяет соотношению, показанному выражением (2), для напряжения Vdd источника питания, приложенного к инвертору, инвертор, работающий в режиме обогащения/обеднения, имеет преимущество по меньшей мере либо по амплитуде колебаний, либо по частоте колебаний кольцевого генератора. Таким образом, каждый инвертор, работающий в режиме обогащения/обеднения, лучше по сравнению с инвертором с насыщенной нагрузкой, работающим в режиме обогащения/обогащения, с точки зрения по меньшей мере либо скорости переключения, либо запаса помехоустойчивости

0,7<|(Vth(Ld)-Vth(Dr))/Vdd|<2 (2)

Таким образом, это выражение (2) показывает, что инвертор, работающий в режиме обогащения/обеднения, работает с таким напряжением источника питания, которое удовлетворяет тому, что разность между пороговыми напряжениями первого и второго транзисторов находится в диапазоне меньше 70% и больше 200% напряжения источника питания.

В упомянутом выше условии оценки в диапазоне вне упомянутого выше неравенства имеется небольшое преимущество в формировании инвертора, работающего в режиме обогащения/обеднения. А именно, в случае когда |(Vth(Ld)-Vth(Dr))/Vdd|<0,7, инвертору не хватает тока для заряда нагрузочной емкости или наблюдается неустойчивое колебание в кольцевом генераторе. С другой стороны, в случае когда |(Vth(Ld)-Vth(Dr))/Vdd|>2, инверсионное напряжение является слишком высоким по сравнению с напряжением источника питания и диапазон входного/выходного напряжения становится узким.

Кроме того, будут подробно описаны материалы для формирования транзисторов TFT, которые должны использоваться в инверторах в соответствии с настоящим изобретением.

• Канальный слой

Для канального слоя используются оксидные полупроводниковые материалы. А именно, могут быть использованы ZnO, In2O3, Ga2O