Интегральный операционный усилитель с токовой обратной связью

Иллюстрации

Показать всеИзобретение относится к электронике, а именно к операционным усилителям (ОУ) с токовой обратной связью, выполненным по интегральной технологии для использования в устройствах обработки, усиления и аналого-цифрового преобразования видео- и радиосигналов. Технический результат: повышение точности. ОУ содержит входную цепь сдвига уровня (1), вход которой соединен с неинвертирующим входом (2) ОУ, первый выход соединен с базой первого n-p-n транзистора (Т) (3), а второй выход - с базой первого p-n-p Т (4) и с первым выводом первого источника тока (ИТ) (5), второй вывод которого соединен с шиной отрицательного питания (ИП) (6) и с зажимом питания первого токового зеркала (ТЗ) (7), вход которого соединен с коллектором Т (4), эмиттер которого подключен к инвертирующему входу (8) ОУ и к эмиттеру Т (3), коллектор которого соединен со входом второго ТЗ (9), зажим питания которого подключен к шине положительного ИП (10) ОУ и к первому выводу второго ИТ (11), второй вывод которого соединен с базой Т (3), первый выход ТЗ (7) соединен с первым выходом ТЗ (9) и с первым входом буфера (12), выход которого соединен с выходом (13) ОУ, второй вход подключен ко второму выходу ТЗ (7), а третий вход - ко второму выходу ТЗ (9). Введены второй n-p-n Т (14), база которого подключена к базе Т (3); второй p-n-p Т (15), база которого подключена к базе Т (4), а эмиттер соединен с эмиттером Т (14); третье ТЗ (16), зажим питания которого соединен с шиной ИП (6), а первый вход - с коллектором Т (15); дополнительный буфер (17), первый вход которого соединен с первым выходом ТЗ (16), а второй вход подключен ко второму выходу ТЗ (16); четвертое ТЗ (18), зажим питания которого подключен к шине ИП (10), вход соединен с коллектором Т (14), первый выход подключен к первому выходу ТЗ (16), а второй выход соединен с третьим входом буфера (17); третий и четвертый n-p-n Т (19) и Т (20), соответственно, эмиттеры которых подключены к третьему выходу ТЗ (16), а базы соединены с выходом буфера (17), коллектор Т (19) подключен к входу управления ТЗ (18), а коллектор Т (20) подключен к входу управления ТЗ (9); пятый и шестой n-p-n Т (21) и Т (22), коллекторы которых соединены с шиной ИП (10), базы соединены с выходом буфера (12), а эмиттеры подключены к третьему выходу ТЗ (16); третий и четвертый p-n-p Т (23) и Т (24), базы которых соединены с выходом буфера (17), эмиттеры подключены к третьему выходу ТЗ (18), коллектор Т (23) соединен со входом управления ТЗ (16), а коллектор Т (24) - со входом управления ТЗ (7); пятый и шестой p-n-p Т (25) и Т (26), эмиттеры которых соединены с третьим выходом ТЗ (18), базы подключены к выходу буфера (12), а коллекторы соединены с шиной отрицательного ИП (6). 7 ил.

Реферат

Изобретение относится к электронике, а именно к операционным усилителям с токовой обратной связью, выполненным по интегральной технологии. Изобретение может использоваться в устройствах обработки, усиления и аналого-цифрового преобразования видео- и радиосигналов в электрических схемах для видеотехники, радиолокации, измерительной техники, связи и других областях.

Известна схема операционного усилителя с токовой обратной связью [1], состоящая из входной цепи сдвига уровня, вход которой соединен с неинвертирующим входом усилителя, первый выход соединен с базой первого n-p-n транзистора, а второй выход - с базой первого p-n-p транзистора, эмиттер которого подключен к эмиттеру первого n-p-n транзистора, второго n-p-n транзистора, база которого подключена к коллектору первого p-n-p транзистора, эмиттер которого соединен с инвертирующим входом усилителя, второго p-n-p транзистора, база которого подключена к коллектору первого n-p-n транзистора и ко второму выводу первого источника тока, первый вывод которого подключен к шине положительного питания, коллектор второго p-n-p транзистора соединен с коллектором второго n-p-n транзистора и с первым входом выходного буфера, выход которого подключен к выходу усилителя, второй вход соединен с коллектором третьего n-p-n транзистора, эмиттер которого подключен к шине отрицательного питания, а база соединена с коллектором первого p-n-p транзистора, с первым выводом второго источника тока и вторым выводом третьего источника тока, первый вывод которого подключен к шине положительного питания, второй вывод второго источника тока соединен с шиной отрицательного питания и первым выводом первого резистора, второй вывод которого подключен к эмиттеру второго n-p-n транзистора, третий вход выходного буфера соединен с коллектором третьего p-n-p транзистора, база которого подключена ко второму выводу первого источника тока и к первому выводу четвертого источника тока, второй вывод которого соединен с шиной отрицательного питания, эмиттер третьего p-n-p транзистора подключен к шине положительного питания и к первому выводу второго резистора, второй вывод которого соединен с эмиттером второго p-n-p транзистора.

Данная схема обеспечивает высокое значение трансимпеданса, но имеет большой входной ток по инвертирующему входу, т.к. разность коллекторных токов первого p-n-p транзистора и первого n-p-n транзистора при включенной отрицательной обратной связи (ООС) приводит к появлению пропорциональной разности их эмиттерных токов. А разность коллекторных токов обусловлена разностями токов третьего, четвертого, пятого и шестого источников токов, соответственно. Последняя, при отсутствии подгонки, обычно достаточно велика, т.к. вызвана разницей параметров p-n-p и n-p-n транзисторов. Причем подгонка минимизирует входной ток при определенном значении входного напряжения (обычно для нулевого значения) и не гарантирует столь же малые значения входного тока во всем диапазоне рабочих напряжений. Второй недостаток данного типа схем заключается в том, что она является двухкаскадной, что приводит к наличию второго низкочастотного полюса и не позволяет обеспечить высокое быстродействие при сохранении устойчивости в схеме с глубокой ООС.

Известна другая схема операционного усилителя с токовой обратной связью [2], состоящая из первого n-p-n транзистора, эмиттер которого соединен с инвертирующим входом усилителя и с эмиттером первого p-n-p транзистора, коллектор которого соединен с базой и подключен к эмиттеру второго p-n-p транзистора и к базе третьего p-n-p транзистора, база первого n-p-n транзистора соединена с коллектором и подключена к эмиттеру второго n-p-n транзистора и к базе третьего n-p-n транзистора, эмиттер которого соединен с неинвертирующим входом усилителя и с эмиттером третьего p-n-p транзистора, коллектор которого соединен с базой второго p-n-p транзистора и с первым выводом первого источника тока, второй вывод которого подключен к шине отрицательного питания и к первому выводу первого резистора, второй вывод которого соединен с коллектором второго p-n-p транзистора и с первым входом первого дифференциального усилителя, коллектор второго n-p-n транзистора подключен к первому выводу второго дифференциального усилителя и к первому выводу второго резистора, второй вывод которого соединен с шиной положительного питания и с первым выводом второго источника тока, второй вывод которого подключен к базе второго n-p-n транзистора и коллектору третьего n-p-n транзистора, второй вход первого дифференциального усилителя соединен с эмиттером четвертого n-p-n транзистора и с первым выводом третьего резистора, второй вывод которого подключен к шине отрицательного питания, второй вход второго дифференциального усилителя соединен с эмиттером четвертого p-n-p транзистора и с первым выводом четвертого резистора, второй вывод которого подключен к шине положительного питания, выход первого дифференциального усилителя соединен с базой четвертого n-p-n транзистора, коллектор которого подключен к коллектору четвертого p-n-p транзистора, база которого соединена с выходом второго дифференциального усилителя и с базой пятого p-n-p транзистора, эмиттер которого подключен к первому выводу пятого резистора, второй вывод которого соединен с шиной положительного питания, коллектор четвертого n-p-n транзистора подключен к первому входу выходного буфера, выход которого соединен с выходом усилителя, третий вход подключен к коллектору пятого p-n-p транзистора, а второй вход соединен с коллектором пятого n-p-n транзистора, база которого подключена к выходу первого дифференциального усилителя, а эмиттер соединен с первым выводом шестого резистора, второй вывод которого подключен к шине отрицательного питания.

Достоинством данной схемы является малый входной ток по инвертирующему входу. Однако такое схемное решение не позволяет получить высокий трансимпеданс. Кроме того, при существенной разнице параметров p-n-p и n-p-n транзисторов, в результате действия местной обратной связи во входном каскаде в таком ОУ, охваченном ООС, входной ток по неинвертирующему входу может достигать неприемлемо высоких значений (до сотни микроампер).

Известна также еще одна схема операционного усилителя с токовой обратной связью [3], состоящая из входной цепи сдвига уровня, вход которой соединен с неинвертирующим входом усилителя, первый выход соединен с базой первого n-p-n транзистора, а второй выход - с базой первого p-n-p транзистора и с первым выводом первого источника тока, второй вывод которого соединен с шиной отрицательного питания и с зажимом питания первого токового зеркала, вход которого соединен с коллектором первого p-n-p транзистора, эмиттер которого подключен к инвертирующему входу усилителя и к эмиттеру первого n-p-n транзистора, коллектор которого соединен со входом второго токового зеркала, зажим питания которого подключен к шине положительного питания усилителя и к первому выводу второго источника тока, второй вывод которого соединен с базой первого n-p-n транзистора, первый выход первого токового зеркала соединен с первым выходом второго токового зеркала и с первым входом выходного буфера, выход которого соединен с выходом усилителя, второй вход подключен к второму выходу первого токового зеркала, а третий вход - ко второму выходу второго токового зеркала.

Описанная выше схема наиболее близка к предлагаемому варианту и принята за прототип. Операционные усилители с токовой обратной связью, отвечающие данной структуре, имеют неудовлетворительную совокупность параметров: большой входной ток по инвертирующему входу вследствие разности параметров p-n-p и n-p-n транзисторов и малое значение трансимпеданса из-за конечности напряжений Эрли транзисторов и отсутствия цепей, компенсирующих указанные недостатки.

Техническим результатом изобретения является повышение точности.

Для достижения поставленной цели в схему, состоящую из входной цепи сдвига уровня, вход которой соединен с неинвертирующим входом усилителя, первый выход соединен с базой первого n-p-n транзистора, а второй выход - с базой первого p-n-p транзистора и с первым выводом первого источника тока, второй вывод которого соединен с шиной отрицательного питания и с зажимом питания первого токового зеркала, вход которого соединен с коллектором первого p-n-p транзистора, эмиттер которого подключен к инвертирующему входу усилителя и к эмиттеру первого n-p-n транзистора, коллектор которого соединен со входом второго токового зеркала, зажим питания которого подключен к шине положительного питания усилителя и к первому выводу второго источника тока, второй вывод которого соединен с базой первого n-p-n транзистора, первый выход первого токового зеркала соединен с первым выходом второго токового зеркала и с первым входом выходного буфера, выход которого соединен с выходом усилителя, второй вход подключен ко второму выходу первого токового зеркала, а третий вход - ко второму выходу второго токового зеркала, дополнительно введены: второй n-p-n транзистор, база которого подключена к базе первого n-p-n транзистора, второй p-n-p транзистор, база которого подключена к базе первого p-n-p транзистора, а эмиттер соединен с эмиттером второго n-p-n транзистора, третье токовое зеркало, зажим питания которого соединен с шиной отрицательного питания, а первый вход - с коллектором второго p-n-p транзистора, дополнительный буфер, первый вход которого соединен с первым выходом третьего токового зеркала, а второй вход подключен ко второму выходу третьего токового зеркала, четвертое токовое зеркало, зажим питания которого подключен к шине положительного питания, вход соединен с коллектором второго n-p-n транзистора, первый выход подключен к первому выходу третьего токового зеркала, а второй выход соединен с третьим входом дополнительного буфера, третий и четвертый n-p-n транзисторы, соответственно, эмиттеры которых соединены между собой и подключены к третьему выходу третьего токового зеркала, а базы соединены между собой и с выходом дополнительного буфера, коллектор третьего n-p-n транзистора подключен к входу управления четвертого токового зеркала, а коллектор четвертого n-p-n транзистора подключен к входу управления второго токового зеркала, пятый и шестой n-p-n транзисторы, коллекторы которых соединены между собой и с шиной положительного питания, базы соединены между собой и с выходом выходного буфера, а эмиттеры соединены между собой и подключены к третьему выходу третьего токового зеркала, третий и четвертый p-n-p транзисторы, базы которых соединены между собой и с выходом дополнительного буфера, эмиттеры соединены между собой и подключены к третьему выходу четвертого токового зеркала, коллектор третьего p-n-p транзистора соединен со входом управления третьего токового зеркала, а коллектор четвертого p-n-p транзистора - со входом управления первого токового зеркала, пятый и шестой p-n-p транзисторы, эмиттеры которых соединены между собой и с третьим выходом четвертого токового зеркала, базы соединены между собой и подключены к выходу выходного буфера, а коллекторы соединены между собой и с шиной отрицательного питания.

Признаками, отличающими предлагаемое устройство от прототипа, являются наличие второго n-p-n транзистора, база которого подключена к базе первого n-p-n транзистора, второго p-n-p транзистор, база которого подключена к базе первого p-n-p транзистора, а эмиттер соединен с эмиттером второго n-p-n транзистора, третьего токового зеркала, зажим питания которого соединен с шиной отрицательного питания, а первый вход - с коллектором второго p-n-p транзистора, дополнительного буфера, первый вход которого соединен с первым выходом третьего токового зеркала, а второй вход подключен ко второму выходу третьего токового зеркала, четвертого токового зеркала, зажим питания которого подключен к шине положительного питания, вход соединен с коллектором второго n-p-n транзистора, первый выход подключен к первому выходу третьего токового зеркала, а второй выход соединен с третьим входом дополнительного буфера, третьего и четвертого n-p-n транзисторов, соответственно, эмиттеры которых соединены между собой и подключены к третьему выходу третьего токового зеркала, а базы соединены между собой и с выходом дополнительного буфера, коллектор четвертого n-p-n транзистора подключен к входу управления четвертого токового зеркала, а коллектор пятого n-p-n транзистора подключен к входу управления второго токового зеркала, пятого и шестого n-p-n транзисторов, коллекторы которых соединены между собой и с шиной положительного питания, базы соединены между собой и с выходом выходного буфера, а эмиттеры соединены между собой и подключены к третьему выходу третьего токового зеркала, третьего и четвертого p-n-p транзисторов, базы которых соединены между собой и с выходом дополнительного буфера, эмиттеры соединены между собой и подключены к третьему выходу четвертого токового зеркала, коллектор третьего p-n-p транзистора соединен со входом управления третьего токового зеркала, а коллектор четвертого p-n-p транзистора - со входом управления первого токового зеркала, пятого и шестого p-n-p транзисторов, эмиттеры которых соединены между собой и с третьим выходом четвертого токового зеркала, базы соединены между собой и подключены к выходу выходного буфера, а коллекторы соединены между собой и с шиной отрицательного питания.

Таким образом, заявляемое схемное решение соответствует критерию "новизна".

Повышение точности обусловлено уменьшением входного тока по инвертирующему входу и увеличением трансимпеданса за счет добавления компенсирующих токов в токовые зеркала усилительного каскада благодаря введению в схему второго, третьего, четвертого, пятого и шестого n-p-n транзисторов, второго, третьего, четвертого, пятого и шестого p-n-p транзисторов, третьего и четвертого токовых зеркал и дополнительного буфера.

Таким образом, повышение точности интегрального операционного усилителя с токовой обратной связью обусловлено введением в схему второго, третьего, четвертого, пятого и шестого n-p-n транзисторов, второго, третьего, четвертого, пятого и шестого p-n-p транзисторов, третьего и четвертого токовых зеркал и дополнительного буфера.

Совокупность новых признаков в данном изобретении неочевидна для специалистов, следовательно, заявленное схемотехническое решение соответствует критерию "изобретательский уровень".

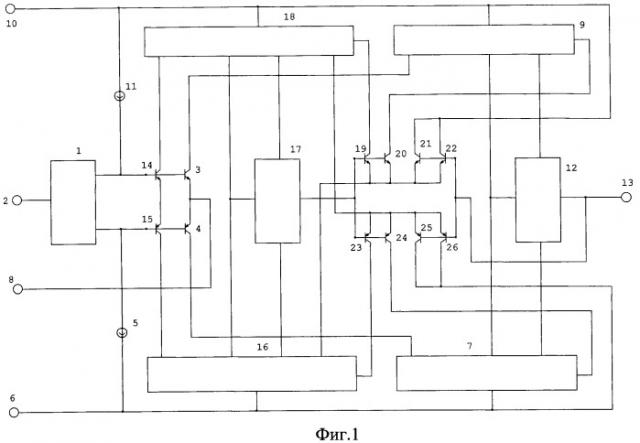

Примером реализации интегрального операционного усилителя с токовой обратной связью является электрическая схема, изображенная на фиг.1.

Интегральный операционный усилитель с токовой обратной связью содержит входную цепь сдвига уровня 1, вход которой соединен с неинвертирующим входом 2 усилителя, первый выход соединен с базой первого n-p-n транзистора 3, а второй выход - с базой первого p-n-p транзистора 4 и с первым выводом первого источника тока 5, второй вывод которого соединен с шиной отрицательного питания 6 и с зажимом питания первого токового зеркала 7, вход которого соединен с коллектором первого p-n-p транзистора 4, эмиттер которого подключен к инвертирующему входу 8 усилителя и к эмиттеру первого n-p-n транзистора 3, коллектор которого соединен со входом второго токового зеркала 9, зажим питания которого подключен к шине положительного питания 10 усилителя и к первому выводу второго источника тока 11, второй вывод которого соединен с базой первого n-p-n транзистора 3, первый выход первого токового зеркала 7 соединен с первым выходом второго токового зеркала 9 и с первым входом выходного буфера 12, выход которого соединен с выходом 13 усилителя, второй вход подключен ко второму выходу первого токового зеркала 7, а третий вход - ко второму выходу второго токового зеркала 9, второй n-p-n транзистор 14, база которого подключена к базе первого n-p-n транзистора 3, второй p-n-p транзистор 15, база которого подключена к базе первого p-n-p транзистора 4, а эмиттер соединен с эмиттером второго n-p-n транзистора 14, третье токовое зеркало 16, зажим питания которого соединен с шиной отрицательного питания 6, а первый вход - с коллектором второго p-n-p транзистора 15, дополнительный буфер 17, первый вход которого соединен с первым выходом третьего токового зеркала 16, а второй вход подключен ко второму выходу третьего токового зеркала 16, четвертое токовое зеркало 18, зажим питания которого подключен к шине положительного питания 10, вход соединен с коллектором второго n-p-n транзистора 14, первый выход подключен к первому выходу третьего токового зеркала 16, а второй выход соединен с третьим входом дополнительного буфера 17, третий и четвертый n-p-n транзисторы 19 и 20, соответственно, эмиттеры которых соединены между собой и подключены к третьему выходу третьего токового зеркала 16, а базы соединены между собой и с выходом дополнительного буфера 17, коллектор третьего n-p-n транзистора 19 подключен к входу управления четвертого токового зеркала 18, а коллектор четвертого n-p-n транзистора 20 подключен к входу управления второго токового зеркала 9, пятый и шестой n-p-n транзисторы 21 и 22, коллекторы которых соединены между собой и с шиной положительного питания, базы соединены между собой и с выходом выходного буфера 12, а эмиттеры соединены между собой и подключены к третьему выходу третьего токового зеркала 16, третий и четвертый p-n-p транзисторы 23 и 24, базы которых соединены между собой и с выходом дополнительного буфера 17, эмиттеры соединены между собой и подключены к третьему выходу четвертого токового зеркала 18, коллектор третьего p-n-p транзистора 23 соединен со входом управления третьего токового зеркала 16, а коллектор четвертого p-n-p транзистора 24 - со входом управления первого токового зеркала 7, пятый и шестой p-n-p транзисторы 25 и 26, эмиттеры которых соединены между собой и с третьим выходом четвертого токового зеркала 18, базы соединены между собой и подключены к выходу выходного буфера 12, а коллекторы соединены между собой и с шиной отрицательного питания 6.

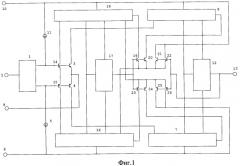

На фиг.2 приведен пример реализации цепи сдвига уровня. Схема содержит входной зажим 27, который является входом устройства, первый выходной зажим 28, являющийся первым выходом устройства, второй выходной зажим 29, являющийся вторым выходом устройства, шину отрицательного питания 30, шину положительного питания 31, первый источник тока 32, первый вход которого соединен с коллектором первого p-n-p транзистора 33, база которого соединена со вторым выходом устройства 29, а эмиттер подключен ко входу 27 устройства и к эмиттеру первого n-p-n транзистора 34, база которого соединена с первым выходом устройства 28, а коллектор соединен со вторым выводом второго источника тока 35 и с базой второго n-p-n транзистора 36, эмиттер которого подключен к первому выходу устройства 28 и к первому выводу третьего источника тока 37, второй вывод которого соединен с шиной отрицательного питания 30, со вторым выводом первого источника тока 32 и с коллектором второго p-n-p транзистора 38, база которого подключена к первому выводу первого источника тока 32, а эмиттер соединен со вторым выходом устройства 29 и со вторым выводом четвертого источника тока 39, первый вывод которого подключен к шине положительного питания 31, к первому выводу второго источника тока 35 и к коллектору второго n-p-n транзистора 36.

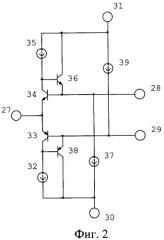

На фиг.3 приведен пример реализации первого токового зеркала. Схема содержит входной зажим 40, являющийся входом устройства, первый выходной зажим 41, являющийся первым выходом устройства, второй выходной зажим 42, являющийся вторым выходом устройства, зажим питания 43, являющийся зажимом питания устройства, вход управления 44, являющийся входом управления устройства, первый n-p-n транзистор 45, база которого соединена с базой и коллектором второго n-p-n транзистора 46 и с эмиттером третьего n-p-n транзистора 47, база которого подключена к входному зажиму 40 и к коллектору первого n-p-n транзистора 45, а коллектор соединен с первым выходным зажимом 41, база первого n-p-n транзистора 45 подключена к входу управления 44 и к базе четвертого n-p-n транзистора 48, коллектор которого соединен со вторым выходным зажимом 42, эмиттер первого n-p-n транзистора 45 подключен к первому выводу первого резистора 49, второй вывод которого соединен с зажимом питания 43 и с первыми выводами второго резистора 50 и третьего резистора 51, второй вывод второго резистора 50 подключен к эмиттеру второго n-p-n транзистора 46, а второй вывод третьего резистора 51 соединен с эмиттером четвертого n-p-n транзистора 48.

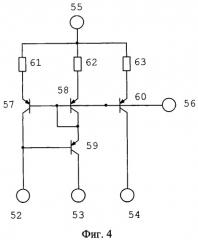

На фиг.4 приведен пример реализации второго токового зеркала. Схема содержит входной зажим 52, являющийся входом устройства, первый выходной зажим 53, являющийся первым выходом устройства, второй выходной зажим 54, являющийся вторым выходом устройства, зажим питания 55, являющийся зажимом питания устройства, вход управления 56, являющийся входом управления устройства, первый p-n-p транзистор 57, база которого соединена с базой и коллектором второго p-n-p транзистора 58 и с эмиттером третьего p-n-p транзистора 59, база которого подключена к входному зажиму 52 и к коллектору первого p-n-p транзистора 57, а коллектор соединен с первым выходным зажимом 53, база первого p-n-p транзистора 57 подключена к входу управления 56 и к базе четвертого p-n-p транзистора 60, коллектор которого соединен со вторым выходным зажимом 54, эмиттер первого p-n-p транзистора 57 подключен к первому выводу первого резистора 61, второй вывод которого соединен с зажимом питания 55 и с первыми выводами второго резистора 62 и третьего резистора 63, второй вывод второго резистора 62 подключен к эмиттеру второго p-n-p транзистора 58, а второй вывод третьего резистора 63 соединен с эмиттером четвертого p-n-p транзистора 60.

На фиг.5 приведен пример реализации третьего токового зеркала. Схема содержит входной зажим 64, являющийся входом устройства, первый выходной зажим 65, являющийся первым выходом устройства, второй выходной зажим 66, являющийся вторым выходом устройства, зажим питания 67, являющийся зажимом питания устройства, вход управления 68, являющийся входом управления устройства, первый n-p-n транзистор 69, база которого соединена с базой и коллектором второго n-p-n транзистора 70 и с эмиттером третьего n-p-n транзистора 71, база которого подключена к входному зажиму 64 и к коллектору первого n-p-n транзистора 69, а коллектор соединен с первым выходным зажимом 65, база первого n-p-n транзистора 69 подключена к входу управления 68 и к базе четвертого n-p-n транзистора 72, коллектор которого соединен со вторым выходным зажимом 66, эмиттер первого n-p-n транзистора 69 подключен к первому выводу первого резистора 73, второй вывод которого соединен с зажимом питания 67 и с первыми выводами второго резистора 74 и третьего резистора 75, второй вывод второго резистора 74 подключен к эмиттеру второго n-p-n транзистора 70, а второй вывод третьего резистора 75 соединен с эмиттером четвертого n-p-n транзистора 72, третий выходной зажим 76, являющийся третьим выходом устройства, соединенный с коллектором пятого n-p-n транзистора 77, база которого подключена к входу управления 68, а эмиттер соединен с первым выводом четвертого резистора 78, второй вывод которого подключен к зажиму питания 67.

На фиг.6 приведен пример реализации четвертого токового зеркала. Схема содержит входной зажим 79, являющийся входом устройства, первый выходной зажим 80, являющийся первым выходом устройства, второй выходной зажим 81, являющийся вторым выходом устройства, зажим питания 82, являющийся зажимом питания устройства, вход управления 83, являющийся входом управления устройства, первый p-n-p транзистор 84, база которого соединена с базой и коллектором второго p-n-p транзистора 85 и с эмиттером третьего p-n-p транзистора 86, база которого подключена к входному зажиму 79 и к коллектору первого p-n-p транзистора 84, а коллектор соединен с первым выходным зажимом 80, база первого p-n-p транзистора 84 подключена к входу управления 83 и к базе четвертого p-n-p транзистора 87, коллектор которого соединен со вторым выходным зажимом 81, эмиттер первого p-n-p транзистора 84 подключен к первому выводу первого резистора 88, второй вывод которого соединен с зажимом питания 82 и с первыми выводами второго резистора 89 и третьего резистора 90, второй вывод второго резистора 89 подключен к эмиттеру второго p-n-p транзистора 85, а второй вывод третьего резистора 90 соединен с эмиттером четвертого p-n-p транзистора 87, третий выходной зажим 91, являющийся третьим выходом устройства, соединенный с коллектором пятого p-n-p транзистора 92, база которого подключена к входу управления 83, а эмиттер соединен с первым выводом четвертого резистора 93, второй вывод которого подключен к зажиму питания 82.

На фиг.7 приведен пример реализации выходного и дополнительного буферов.

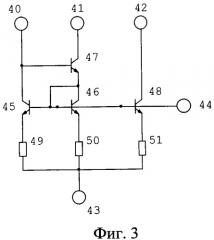

Схема содержит первый входной зажим 94, являющийся первым входом устройства, второй входной зажим 95, являющийся вторым входом устройства, третий входной зажим 96, являющийся третьим входом устройства, выходной зажим 97, являющийся выходом устройства, шину отрицательного питания 98, шину положительного питания 99, первый n-p-n транзистор 100, база которого соединена с первым входным зажимом 94 и с базой первого p-n-p транзистора 101, эмиттер которого подключен к третьему входному зажиму 96, а коллектор - к шине отрицательного питания 98 и к коллектору второго p-n-p транзистора 102, база которого соединена со вторым входным зажимом 95, а эмиттер подключен к выходному зажиму 97 и к эмиттеру второго n-p-n транзистора 103, база которого соединена с третьим входным зажимом 96, а коллектор подключен к шине положительного питания 99 и к коллектору первого n-p-n транзистора 100.

Предложенная схема интегрального операционного усилителя с токовой обратной связью позволяет увеличить точность за счет уменьшения входного тока по инвертирующему входу в 6 раз по сравнению с прототипом и увеличить трансимпеданс в 17 раз по сравнению с прототипом. Отмеченные выше свойства схемы являются техническим результатом.

Схема работает следующим образом. Площади эмиттеров первого n-p-n транзистора 3 и второго n-p-n транзистора 14 относятся как m:1, площади первого p-n-p транзистора 4 и второго p-n-p транзистора 15 также относятся как m:1. Площади эмиттеров транзисторов выходного буфера 12 относятся к площадям эмиттеров дополнительного буфера 17 как m:1. Площадь эмиттера транзистора 20 относится к площади эмиттера транзистора 19 как m:1, площадь эмиттера транзистора 22 относится к площади эмиттера транзистора 21 как m:1, площадь эмиттера транзистора 24 относится к площади эмиттера транзистора 23 как m:1, площадь эмиттера транзистора 26 относится к площади эмиттера транзистора 25 как m:1. Коэффициенты отражения токовых первого и третьего зеркал 7 и 16 со входа на первый выход равны n1, а со входа на второй выход - n2. Коэффициенты отражения токовых второго и четвертого зеркал 9 и 18 со входа на первый выход равны р1, а со входа на второй выход - р2. Транзисторы выполнены на одном кристалле, поэтому характеристики всех n-p-n транзисторов, кроме площадей эмиттеров, идентичны и характеристики всех p-n-p транзисторов идентичны.

Обозначим как Ik1 - ток коллектора второго n-p-n транзистора 14, Ik2 - ток коллектора второго p-n-p транзистора 15. Тогда токи коллекторов первого n-p-n транзистора 3 и первого p-n-p транзистора 4 будут равны, соответственно: mIk1 и mIk2, токи с первых выходов, соответственно, четвертого и третьего токовых зеркал: p1Ik1 и n1Ik2. Входной ток выходного буфера 12 равен (без учета базовых токов выходных транзисторов буфера):

где h21n - коэффициент усиления по току входного n-p-n транзистора буфера, h21p - коэффициент усиления по току входного p-n-p транзистора буфера. Входной ток дополнительного буфера 17 равен (без учета базовых токов выходных транзисторов буфера):

Следовательно, можно записать:

Ia - ток коллектора транзистора 19, Il - ток коллектора транзистора 23. Тогда коллекторные токи транзисторов 20 и 24, соответственно, равны:

В ОУ, охваченном отрицательной обратной связью (ООС), в состоянии равновесия выполняются условия:

Токи коллекторов 3 и 4 равны, соответственно: mIk1 и mIk2, а токи коллекторов 14 и 15 равны, соответственно: Ik1 и Ik2. При этом в соответствии с законом Кирхгофа:

Где α1 и α2 - коэффициенты передачи по току из эмиттера в коллектор, соответственно, транзисторов 14 и 15. Т.к. характеристики транзисторов 3 и 14 и 4 и 15 попарно идентичны за исключением площадей транзисторов, то:

То есть входной ток по инвертирующему входу стремится к нулю.

При изменении выходного напряжения в схеме с ОУ, охваченным ООС, изменяется ток через цепь обратной связи. Например, если выходное напряжение должно получить положительное приращение ΔUout, ток через вывод 8 изменяется на 2ΔI и коллекторные токи транзисторов 3 и 4 получают приращения:

В результате условие нового равновесия ОУ выглядит как:

где

ΔIa и ΔIl - приращения, вызванные работой транзисторов 19…26, которая заключается в следующем. При изменении выходного напряжения ОУ потенциалы на выходах буферов 12 и 17 становятся не равны, вследствие чего токи Ia, Il изменяются на величины, соответственно, ΔIa, ΔIl так, чтобы выходные напряжения буферов 12 и 17 вновь стали равны. Токи коллекторов транзисторов 20 и 24 изменяются при этом, соответственно, на величины: mΔIa и mΔIl. Тогда новое условие равновесия для потенциала на входе дополнительного буфера 17:

Т.к. m не равно нулю, то, подставляя (14) в (12), получаем:

С учетом (13):

Т.к. и , то

То есть ΔI=0.

Фактически получается, что изменение токов коллекторов токовых зеркал, необходимое для приращения выходного напряжения ОУ, происходит за счет изменения Ia и Il, в то время как в схеме прототипа для такого приращения необходимо изменение входного тока по инвертирующему входу. Трансимпеданс ОУ с ТОС рассчитывается как:

Т.к. dIn-=ΔI=0, то Rt, теоретически, стремится к бесконечности. В реальной схеме трансимпеданс будет иметь конечное значение вследствие конечности коэффициентов усиления дифференциальных каскадов на транзисторах 19…26, разности сопротивлений нагрузок буферов 12 и 17 и разброса параметров транзисторов, возникающего в процессе производства микросхемы. По этим же причинам не будет равно нулю и реальное значение Iвх-. Но предлагаемое схемное решение позволяет существенно уменьшить Iвх- и увеличить Rt по сравнению с прототипом.

При сравнительном моделировании заявляемого устройства и прототипа получены следующие результаты (при одинаковых режимных токах и параметрах транзисторов). При четырехкратной разнице в h21 и двукратной разнице напряжений Эрли между n-p-n и p-n-p транзисторами, для схемы прототипа: Iвх-=24 мкА, Rt=833 кОм, для заявляемого устройства: Iвх-=4 мкА, Rt=14286 кОм. Таким образом, входной ток по инвертирующему входу по сравнению с прототипом уменьшился в 6 раз, трансимпеданс по сравнению с прототипом увеличился в 17 раз.

Список литературы.

1. U.S. Patent N 5537079, 330/265; 330/267, Jul. 16, 1996.

2. U.S. Patent N 5734293, 327/561; 327/563; 327/103; 327/317; 323/316, Mar. 31, 1998.

3. U.S. Patent N 5789982, 330/255; 330/267; 330/310, Aug. 4, 1998 (прототип).

Перечень фигур чертежей.

Фиг.1. Электрическая схема интегрального операционного усилителя с токовой обратной связью: 1 - цепь сдвига уровня, 2 - неинвертирующий вход устройства, 3 - первый n-p-n транзистор, 4 - первый p-n-p транзистор, 5 - первый источник тока, 6 - шина отрицательного питания, 7 - первое токовое зеркало, 8 - инвертирующий вход устройства, 9 - второе токовое зеркало, 10 - шина положительного питания, 11 - второй источник тока, 12 - выходной буфер, 13 - выход устройства, 14 - второй n-p-n транзистор, 15 - второй p-n-p транзистор, 16 - третье токовое зеркало, 17 - дополнительный буфер, 18 - четвертое токовое зеркало, 19 - третий n-p-n транзистор, 20 - четвертый n-p-n транзистор, 21 - пятый n-p-n транзистор, 22 - шестой n-p-n транзистор, 23 - третий p-n-p транзистор, 24 - четвертый p-n-p транзистор, 25 - пятый p-n-p транзистор, 26 - шестой p-n-p транзистор.

Фиг.2. Цепь сдвига уровня: 27 - входной зажим, 28 - первый выходной зажим, 29 - второй выходной зажим, 30 - шина отрицательного питания, 31 - шина положительного питания, 32 - первый источник тока, 33 - первый p-n-p транзистор, 34 - первый n-p-n транзистор, 35 - второй источник тока, 36 - второй n-p-n транзистор, 37 - третий источник тока, 38 - второй p-n-p транзистор, 39 - четвертый источник тока.

Фиг.3. Первое токовое зеркало: 40 - входной зажим, 41 - первый выходной зажим, 42 - второй выходной зажим, 43 - зажим питания, 44 - вход управления, 45 - первый n-p-n транзистор, 46 - второй n-p-n транзистор, 47 - третий n-p-n транзистор, 48 - четвертый n-p-n транзистор, 49 - первый резистор, 50 - второй резистор, 51 - третий резистор.

Фиг.4. Второе токовое зеркало: 52 - входной зажим, 53 - первый выходной зажим, 54 - второй выходной зажим, 55 - зажим питания, 56 - вход управления, 57 - первый p-n-p транзистор, 58 - второй p-n-p транзистор, 59 - третий p-n-p транзистор, 60 - четвертый p-n-p транзистор, 61 - первый резистор, 62 - второй резистор, 63 - третий резистор.

Фиг.5. Третье токовое зеркало: 64 - входной зажим, 65 - первый выходной зажим, 66 - второй выходной зажим, 67 - зажим питания, 68 - вход управления, 69 - первый n-p-n транзистор, 70 - второй n-p-n транзистор, 71 - третий n-p-n транзистор, 72 - четвертый n-p-n транзистор, 73 - первый резистор, 74 - второй резистор, 75 - третий резистор, 76 - третий выходной зажим, 77 - пятый n-p-n транзистор, 78 - четвертый резистор.

Фиг.6. Четвертое токовое зеркало: 79 - входной зажим, 80 - первый выходной зажим, 81 - второй выходной зажим, 82 - зажим питания, 83 - вход управления, 84 - первый p-n-p транзистор, 85 - второй p-n-p транзистор, 86 - третий p-n-p транзистор, 87 - четвертый p-n-p транзистор, 88 - первый резистор, 89 - второй резистор, 90 - третий резистор, 91 - третий выходной зажим, 92 - пятый p-n-p транзистор, 93 - четвертый резистор.

Фиг.7. Выходной и дополнительный буфер: 94 - первый входной зажим, 95 - второй входной зажим, 96 - третий входной зажим, 97 - выходной зажим, 98 - шина отрицательного питания, 99 - шина положительного питания, 100 - первый n-p-n транзистор, 101 - первый p-n-p транзистор, 102 - второй p-n-p транзистор, 103 - второй n-p-n транзистор.

Операционный усилитель с токовой обратной связью, состоящий из входной цепи сдвига уровня, вход которой соединен с неинвертирующим входом усилителя, первый выход соединен с базой первого n-p-n транзистора, а второй выход - с базой первого p-n-p транзистора и с первым выводом первого источника тока, второй вывод которого соединен с шиной отрицательного питания и с зажимом питания первого токового зеркала, вход которого соединен с коллектором первого p-n-p транзистора, эмиттер которого подключен к инвертирующему входу усилителя и к эмиттеру первого n-p-n транзистора, коллектор которого соединен со входом второго токового зеркала, зажим питания которого подключен к шине положительного питания усилителя и к первому выводу второго источника тока, второй вывод которого соединен с базой первого n-p-n транзистора, первый выход первого токового зеркала соединен с первым выходом второго токового зеркала и с первым входом выходного буфера, выход которого соединен с выходом усилителя, второй вход подключен к второму выходу первого токового зеркала, а третий вход - ко второму выходу второго токового зеркала, отличающийся тем, что в него введены второй n-p-n транзистор, база которого подключена к базе первого n-p-n транзистора, второй p-n-p транзистор, база которого подключена к базе первого p-n-p транзистора, а эмиттер соединен с эмиттером второго n-p-n транзистора, третье токовое зеркало, зажим питания, которого соединен с шиной отрицательного питания, а первый вход - с ко