Улучшение устойчивости считывания памяти с использованием избирательной предварительной зарядки

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в повышении устойчивости считывания за счет снижения напряжения разрядной линии. Способ управления устройством памяти, имеющим разрядную линию, включающую в себя первый участок и второй участок, состоящий в том, что предварительно заряжают первый участок разрядной линии до первого напряжения; предварительно заряжают второй участок разрядной линии до второго напряжения, второе напряжение отличается от первого напряжения; и распределяют заряд между первым участком разрядной линии и вторым участком разрядной линии для получения заключительного напряжения между первым напряжением и вторым напряжением. 5 н. и 20 з.п. ф-лы, 10 ил.

Реферат

ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННУЮ ЗАЯВКУ

Эта заявка испрашивает приоритет по предварительной заявке США, № 61/014038, поданной 15 декабря 2007 года.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение в целом относится к интегральным схемам (ИС, IC). Более точно, это изобретение относится к устройствам памяти.

УРОВЕНЬ ТЕХНИКИ

Устройство памяти или память в целом могут быть описаны в качестве аппаратных средств, которые могут сохранять данные для более поздней выборки. Некоторые устройства памяти включают в себя набор транзисторов, используемых для сохранения данных (например, представленных электрическим зарядом), и набор транзисторов, используемых для управления доступом к хранилищу данных. Размеры транзисторов сократились до 45 нм, а скоро будут достигать 32 нм. Так как размеры уменьшились, уменьшилась относительная величина погрешности, приемлемая во время производства. Как результат, транзисторы промышленного производства демонстрируют большую нестабильность во время работы.

Большой прирост нестабильности транзисторных технологий оказал негативное влияние на устройства памяти и устойчивость их считывания. Устойчивость считывания является способностью устройства памяти удерживать правильные данные, когда подвергаются доступу в присутствии шумов. Как правило, устойчивость считывания измеряется с использованием статического запаса помехоустойчивости (SNM). Большие разбросы характеристик транзисторов промышленного производства вызывают уменьшение статического запаса устойчивости устройства памяти. Это уменьшение статического запаса помехоустойчивости снижает надежность разрядных ячеек и устойчивость к шуму, а отсюда, уменьшает выход годной памяти вследствие повышенных отказов.

Незначительное снижение напряжения разрядной линии устройства памяти по сравнению с напряжением питания значительно улучшает статический запас помехоустойчивости устройства памяти. Однако в конструкциях памяти разрядная линия обычно предварительно заряжается до напряжения питания перед осуществлением доступа к памяти. Было несколько попыток уменьшить напряжение разрядной линии для улучшения устойчивости считывания. Предыдущие попытки показали большую чувствительность к изменениям технологического процесса, температуры и напряжения во время производства, которая может ограничивать свою эффективность для улучшения устойчивости считывания. Некоторые из этих попыток включают в себя импульсную схему разрядной линии, двойные напряжения питания и динамическое смещение ячейки.

В импульсной схеме разрядной линии сбросное устройство присоединено к разрядной линии. После предварительной зарядки разрядной линии до напряжения питания короткий импульс подается на сбросное устройство, которое понижает напряжение разрядной линии и улучшает устойчивость считывания. Эта технология очень чувствительная к формированию этого короткого импульса, особенно потому, что длительность импульса будет меняться в зависимости от изменений технологического процесса, напряжения и температуры во время производства транзисторов и изменений внешней среды.

Еще одна попытка использует два напряжения питания, одно - для разрядной ячейки, а другое - для разрядной линии, где напряжение разрядной линии ниже, чем напряжение разрядной ячейки. Добавление дополнительных напряжений питания является трудной задачей и усложняет проектирование на физическом уровне и проверку микросхемы.

Еще одна другая попытка уменьшить напряжение разрядной линии включает в себя использование устройства NMOS для предварительной зарядки разрядной линии для уменьшения напряжения разрядной линии пороговым напряжением устройства NMOS. В этом случае используется устройство NMOS с низким пороговым напряжением, которое повышает сложность технологического процесса и себестоимость, например, требуя дополнительных масок. В дополнение, пороговое напряжение обладает сильной зависимостью от изменений технологического процесса, напряжения и температуры.

Эти три попытки улучшить устойчивость считывания памяти чувствительны к изменениям производственного процесса и, по существу, трудны для реализации и дорогостоящи для реализации. Такая себестоимость дополнительно повышается, когда многочисленные напряжения питания или устройство NMOS реализованы в цепях предварительной зарядки. Таким образом, есть необходимость в улучшенной устойчивости считывания в конструкциях памяти, которые понижают чувствительность к изменениям производственного процесса, не навлекая на себя дополнительные затраты.

КРАТКАЯ СУЩНОСТЬ ИЗОБРЕТЕНИЯ

В соответствии с одним из аспектов этого раскрытия, устройство памяти включает в себя разрядную линию, имеющую первый участок и второй участок. Устройство памяти также включает в себя схему распределения заряда, избирательно присоединяемую к первому участку и второму участку, в котором схема распределения заряда сконфигурирована для присоединения и отсоединения первого участка от второго участка.

В соответствии с еще одним аспектом этого раскрытия, способ управления устройством памяти включает в себя предварительную зарядку первого участка разрядной линии до первого напряжения и предварительную зарядку второго участка разрядной линии до второго напряжения. Второе напряжение является отличным от первого напряжения. Способ также включает в себя распределение заряда между первым участком разрядной линии и вторым участком разрядной линии.

В соответствии с еще одним другим аспектом этого раскрытия, устройство памяти включает в себя средство для предварительной зарядки первого участка разрядной линии до первого напряжения. Устройство памяти также включает в себя средство для предварительной зарядки второго участка разрядной линии до второго напряжения. Устройство памяти дополнительно включает в себя средство для распределения заряда между первым участком разрядной линии и вторым участком разрядной линии.

В соответствии с дополнительным аспектом раскрытия, способ управления устройством памяти, имеющим разрядную линию, включающую в себя первый участок и второй участок, включает в себя этап предварительной зарядки первого участка разрядной линии до первого напряжения. Способ дополнительно включает в себя этап предварительной зарядки второго участка разрядной линии до второго напряжения, которое отличается от первого напряжения. Способ также включает в себя этап распределения заряда между первым участком разрядной линии и вторым участком разрядной линии для получения уровня напряжения между первым напряжением и вторым напряжением.

Выше, в общих чертах, описаны признаки и технические преимущества настоящего раскрытия, для того чтобы могло быть лучше понято подробное описание, которое следует ниже. Дополнительные признаки и преимущества раскрытия будут описаны ниже. Специалистами в данной области техники должно быть принято во внимание, что это раскрытие может без труда использоваться в качестве основы для модификации или проектирования других конструкций для выполнения идентичных целей настоящего раскрытия. Специалистами в данной области техники также должно пониматься, что такие эквивалентные конструкции не отходят от принципов, которые изложены в прилагаемой формуле изобретения. Новые признаки, которые предполагаются характеристиками раскрытия, как в отношении своей организации, так и способа работы, вместе с дополнительными целями и преимуществами, будут лучше понятны из последующего описания, когда рассматриваются в связи с прилагаемыми фигурами. Однако должно быть отчетливо понятно, что каждая из фигур приведена исключительно с целью иллюстрации и описания, и не подразумевается в качестве определения границ настоящего раскрытия.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Для более полного понимания раскрытия в настоящей заявке ниже приводится подробное описание изобретения со ссылками на прилагаемые чертежи, на которых:

фиг. 1 - иллюстрация примерной системы беспроводной связи, в которой преимущественно может применяться вариант осуществления раскрытия;

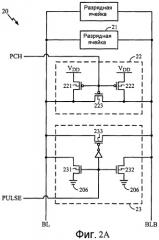

фиг. 2A - схема, схематически иллюстрирующая традиционную импульсную схему разрядной линии для улучшенной устойчивости SRAM;

фиг. 2B - временная диаграмма, иллюстрирующая традиционную импульсную схему разрядной линии для улучшенной устойчивости SRAM;

фиг. 3 - принципиальная схема, иллюстрирующая операцию начальной предварительной зарядки в примерной технологии избирательной предварительной зарядки согласно одному из вариантов осуществления раскрытия;

фиг. 4 - принципиальная схема, иллюстрирующая операцию распределения заряда в примерной технологии избирательной предварительной зарядки согласно одному из вариантов осуществления раскрытия;

фиг. 5 - принципиальная схема, иллюстрирующая выборку разрядной ячейки для операции считывания или записи согласно одному из вариантов осуществления раскрытия;

фиг. 6 - принципиальная схема, иллюстрирующая предварительную зарядку разрядных линий до разных напряжений в примерной технологии избирательной предварительной зарядки согласно одному из вариантов осуществления раскрытия;

фиг. 7 - временная диаграмма, иллюстрирующая примерную операцию избирательной предварительной зарядки согласно одному из вариантов осуществления раскрытия;

фиг. 8 - принципиальная схема для реализации примерной технологии избирательной предварительной зарядки согласно одному из вариантов осуществления раскрытия;

фиг. 9 - структурная схема, иллюстрирующая АРМ проектировщика, используемый для проектирования схемы, компоновки и логики раскрытой полупроводниковой интегральной схемы.

ПОДРОБНОЕ ОПИСАНИЕ

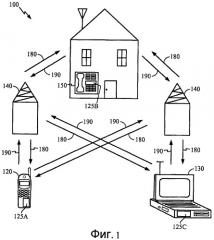

Фиг. 1 показывает примерную систему 100 беспроводной связи, в которой может преимущественно применяться вариант осуществления раскрытия. Для целей иллюстрации фиг. 1 показывает три удаленных узла 120, 130 и 150 и две базовых станции 140. Следует отметить, что типичные системы беспроводной связи могут иметь гораздо больше удаленных узлов и базовых станций. Удаленные узлы 120, 130 и 150 включают в себя устройства 125A, 125B и 125C памяти, созданные согласно варианту осуществления раскрытия. Фиг. 1 показывает сигналы 180 прямой линии связи с базовых станций 140 на удаленные узлы 120, 130 и 150, и сигналы 190 обратной линии связи из удаленных узлов 120, 130 и 150 на базовые станции 140.

На фиг. 1 удаленный узел 120 показан в качестве мобильного телефона, удаленный узел 130 показан в качестве портативного компьютера, а удаленный узел 150 показан в качестве удаленного узла стационарной установки в системе беспроводного абонентского шлейфа. Например, удаленные узлы могут быть сотовыми телефонами, карманными устройствами персональных систем связи (PCS), портативными цифровыми устройствами, такими как персональные цифровые секретари, или цифровыми устройствами стационарной установки, такими как оборудование считывания показаний измерительных приборов. Хотя фиг. 1 иллюстрирует удаленные узлы согласно доктринам раскрытия, раскрытие не ограничено этими примерными проиллюстрированными узлами. Раскрытие может надлежаще применяться в любом устройстве, которое включает в себя устройства памяти, изготовленные в соответствии с доктринами раскрытия.

Фиг. 2A - схема, схематически иллюстрирующая традиционную импульсную схему разрядной линии для улучшенной устойчивости памяти. Схема 20 включает в себя разрядную ячейку 21, сконфигурированную для сохранения данных и присоединенную к дополнительным цепям для управления режимом считывания и записи схемы 20. Разрядная ячейка 21 может быть шеститранзисторной ячейкой памяти. Сигнал предварительной зарядки, PCH, привязан к схеме 22 предварительной зарядки. Схема 22 предварительной зарядки включает в себя транзистор 221, присоединенный к разрядной линии, BL, транзистор 222, присоединенный к инверсной разрядной линии, BLB, и транзистор 223, присоединенный к обеим, разрядной линии, BL, и инверсной разрядной линии, BLB. Импульсный сигнал, PULSE, привязан к схеме 23 сброса. Схема 23 сброса включает в себя транзистор 231, присоединенный к разрядной линии, BL, транзистор 232, присоединенный к инверсной разрядной линии, BLB, и транзистор 233, присоединенный к обеим, разрядной линии, BL, и инверсной разрядной линии, BLB.

Для иллюстративных целей далее будет описана работа традиционной импульсной схемы разрядной линии. Фиг. 2B - временная диаграмма, иллюстрирующая традиционную импульсную схему разрядной линии для улучшенной устойчивости памяти. Схема 20 запускается в момент 251 времени, когда сигнал предварительной зарядки, PCH, низок, и транзистор 221 подтягивает разрядную линию, BL, к напряжению питания, VDD, и транзистор 222 подтягивает инверсную разрядную линию, BLB, к напряжению питания, VDD. В момент 252 времени сигнал предварительной зарядки, PCH, является выключением возбуждения транзистора 221, транзистора 222 и транзистора 223, чтобы отсоединять разрядную линию, BL, и инверсную разрядную линию, BLB, от напряжения питания, VDD. В момент 252 времени короткий положительный импульс формируется в импульсном сигнале, PULSE. Импульсный сигнал, PULSE, включает транзистор 231 и транзистор 232, чтобы присоединять разрядную линию, BL, и инверсную разрядную линию, BLB, к потенциалу 206 земли. Транзистор 233 выключается, чтобы отсоединять разрядную линию, BL, от инверсной разрядной линии, BLB. Снижение напряжения происходит на разрядной линии, BL, и инверсной разрядной линии, BLB. В момент 253 времени импульсный сигнал, PULSE, возвращается в низкое состояние, так что разрядная линия, BL, и инверсная разрядная линия, BLB, прекращают уменьшение напряжения. Хотя эта технология снижает напряжение разрядной линии для улучшения устойчивости считывания, эта технология очень чувствительная к формированию короткого импульса, особенно потому, что длительность импульса будет сильно меняться в зависимости от изменений технологического процесса, напряжения и температуры во время производства транзисторов.

Далее, со ссылкой на фиг. 3, фиг. 4 и фиг. 5, теперь будет описана улучшенная технология избирательной предварительной зарядки. Технология избирательной предварительной зарядки понижает напряжение разрядной линии для улучшения устойчивости считывания, не будучи настолько чувствительной к изменениям технологического процесса, напряжения и температуры. Напряжение разрядной линии понижается посредством распределения заряда между участками разрядной линии, которые избирательно соединяются, чтобы давать возможность распределения во время операций считывания и записи. Хотя будут описаны устройства памяти SRAM (статического запоминающего устройства с произвольной выборкой), технология избирательной предварительной зарядки может применяться к любой конструкции памяти, в том числе, но не в качестве ограничения, SRAM, DRAM или MRAM.

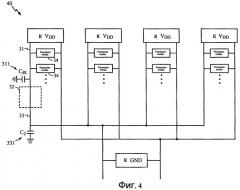

Разные части разрядной линии предварительно заряжаются до разных напряжений (например, VDD и GND) и, используя распределение заряда, достигается требуемое итоговое значение напряжения разрядной линии. В одном из вариантов осуществления, операция распределения заряда поделена на три части. Прежде всего, как проиллюстрировано на фиг. 3, верхняя часть разрядной линии предварительно заряжается до VDD наряду с тем, что нижняя часть разрядной линии предварительно заряжается до GND (потенциала земли). Затем, как проиллюстрировано на фиг. 4, ключи распределения заряда выключаются, чтобы дать возможность распределения заряда между верхними из нижних частей разрядных линий. Поэтому итоговое напряжение разрядной линии будет определяться отношением емкостей между CBL и C2. В заключение, как проиллюстрировано на фиг. 5, распределение заряда выключается из работы для всех столбцов наряду с тем, что ключ остается включенным для столбца, выбранного для операции считывания или записи.

Фиг. 3 - структурная схема, иллюстрирующая операцию начальной предварительной зарядки в примерной технологии избирательной предварительной зарядки. Структурная схема 30 включает в себя верхнюю разрядную линию 31 наряду с ассоциативно связанной емкостью, проиллюстрированной конденсатором 311, со значением CBL. Нижняя разрядная линия 33 имеет ассоциативно связанную емкость, проиллюстрированную емкостью 331, со значением C2. Верхняя разрядная линия 31 и нижняя разрядная линия 33 присоединены к ключу 32 мультиплексирования. На структурной схеме 30 ключ 32 мультиплексирования разомкнут во время начальной предварительной зарядки, чтобы предоставлять верхней разрядной линии 31 возможность предварительно заряжаться до напряжения питания, VDD, а нижней разрядной линии 33 возможность предварительно заряжаться до потенциала земли, GND. Дополнительно, разрядные ячейки 34 присоединены к верхней разрядной линии 31. В еще одном варианте осуществления, разрядные ячейки 34 могут быть присоединены к нижней разрядной линии 33.

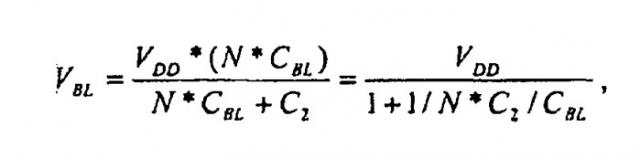

Фиг. 4 - структурная схема, иллюстрирующая операцию распределения заряда в примерной технологии избирательной предварительной зарядки. Структурная схема 40 включает в себя верхнюю разрядную линию 31, емкость, представленную конденсатором 311, нижнюю разрядную линию 33, емкость, представленную конденсатором 331, и ключ 32 мультиплексирования. Операция распределения заряда происходит посредством замыкания ключа 32 мультиплексирования, чтобы присоединять верхнюю разрядную линию 31 к нижней разрядной линии 33. Итоговое напряжение, VBL, на сочетании верхней разрядной линии 31 и нижней разрядной линии 33 является функцией начального напряжения на верхней разрядной линии 31, начального напряжения на нижней разрядной линии 33, конденсатора 311 и конденсатора 331, которая задана

где N - количество пар разрядных линий, присоединенных к ключу 32 мультиплексирования.

Фиг. 5 - структурная схема, иллюстрирующая выключения из работы распределения заряда в примерной технологии избирательной предварительной зарядки. Структурная схема 50 включает в себя верхнюю разрядную линию 31, емкость, представленную конденсатором 311, нижнюю разрядную линию 33, емкость, представленную конденсатором 331, и ключ 32 мультиплексирования. Ключ 32 мультиплексирования размыкается для отсоединения верхней разрядной линии 31 от нижней разрядной линии 33 после того, как завершено распределение заряда. Это размыкание выключает из работы операцию распределения заряда, поэтому данные могут считываться из или записываться в разрядную ячейку 34. Ключ 52 мультиплексирования остается замкнутым, так как разрядная ячейка 54 была выбрана для операции считывания или записи.

Фиг. 6 - структурная схема, иллюстрирующая предварительную зарядку разрядных линий до разных напряжений в примерной технологии избирательной предварительной зарядки согласно еще одному варианту осуществления раскрытия. В этом варианте осуществления, не все верхние разрядные линии заряжаются до напряжения питания, VDD. Структурная схема 60 включает в себя верхнюю разрядную линию 31, емкость, представленную конденсатором 311, нижнюю разрядную линию 33, емкость, представленную конденсатором 331, и ключ 32 мультиплексирования. Верхняя разрядная линия 31 предварительно заряжается до напряжения питания, VDD, а нижняя разрядная линия 33 предварительно заряжается до потенциала земли, GND. В этом варианте осуществления, каждая верхняя разрядная линия может предварительно заряжаться до разного напряжения. Например, верхняя разрядная линия 61 предварительно заряжается до потенциала земли, GND. Таким образом, когда происходит распределение заряда, верхние разрядные линии и инверсные верхние разрядные линии будут иметь более низкое итоговое напряжение по сравнению с тем, когда все верхние разрядные линии предварительно заряжаются до напряжения питания, VDD. Дополнительные разрядные линии могут заряжаться до потенциала земли, GND, напряжения питания, VDD, или других напряжений питания (не показаны) для получения надлежащего итогового напряжения.

Фиг. 7 - временная диаграмма, иллюстрирующая операцию избирательной предварительной зарядки. Операция избирательной предварительной зарядки на верхней разрядной линии, BLU, инверсной верхней разрядной линии, BLBU, нижней разрядной линии, BLL, и инверсной разрядной линии, BLBL, управляется сигналом предварительной зарядки, PRECHG, сигналом мультиплексирования, MUX_STATE (состояния мультиплексирования) и сигналом распределения заряда, CH_SH. Сигнал числовой линии, WL, дает возможность доступа к верхней разрядной линии, BLU, инверсной верхней разрядной линии, BLBU, нижней разрядной линии, BLL, и инверсной нижней разрядной линии, BLBL. Начальное состояние схемы имеет место в момент 711 времени, когда сигнал предварительной зарядки, PRECHG, сигнал мультиплексирования, MUX_STATE, сигнал распределения заряда, CH_SH, и сигнал числовой линии, WL, являются низкими. Нижняя разрядная линия, BLL, и инверсная нижняя разрядная линия, BLBL, предварительно разряжаются до потенциала земли, а верхняя разрядная линия, BLU, и инверсная верхняя разрядная линия, BLBU, предварительно заряжаются до напряжения питания, VDD. Уровень напряжения питания указан штрихпунктирной линией.

После сигнала предварительной зарядки, PRECHG, находившегося в высоком состоянии (деактивизации схемы предварительной зарядки), распределение заряда включается в работу, когда сигнал мультиплексирования, MUX_STATE, является низким. Как результат, в момент 712 времени, сигнал распределения заряда, CH_SH, переходит в высокое состояние. Верхняя разрядная линия, BLU, и инверсная верхняя разрядная линия, BLBU, снижаются по напряжению к потенциалу земли, GND, в ответ на распределение заряда. Дополнительно, нижняя разрядная линия, BLL, и инверсная нижняя разрядная линия, BLBL, повышаются по напряжению к напряжению питания, VDD. Сигнал мультиплексирования, MUX_STATE, переходит в высокое состояние незадолго до момента 713 времени, указывающего окончание операции распределения заряда. Как результат, сигнал распределения заряда, CH_SH, находится в низком состоянии в момент 713 времени, завершающем операцию распределения заряда. Напряжения верхней разрядной линии, BLU, инверсной верхней разрядной линии, BLBU, нижней разрядной линии, BLL, и инверсной нижней разрядной линии, BLBL, стабилизируются в момент 713 времени, когда заканчивается операция распределения заряда. Уменьшение напряжений верхней разрядной линии, BLU, и инверсной верхней разрядной линии, BLBU, повышает устойчивость считывания памяти.

В момент 714 времени числовая линия, WL, переходит в высокое состояние, указывая, что началась операция считывания. Напряжение на верхней разрядной линии, BLU, верхней инверсной разрядной линии, BLBU, нижней разрядной линии, BLL, и нижней инверсной разрядной линии, BLBL, разряжается к потенциалу земли, GND. В момент 715 времени после того как операция считывания завершена, а числовая линия, WL, находилась в низком состоянии, сигнал предварительной зарядки, PRECHG, находится в низком состоянии. Как результат, верхняя разрядная линия, BLU, и инверсная верхняя разрядная линия, BLBU, заряжаются до напряжения питания, VDD, а нижняя разрядная линия, BLL, и инверсная нижняя разрядная линия, BLBL, предварительно разряжаются до потенциала земли, GND. Незадолго до момента 716 времени сигнал мультиплексирования, MUX_STATE, переходил в низкое состояние, возвращая все сигналы в их исходное состояние, в момент 716 времени.

Фиг. 8 - принципиальная схема у схемы для реализации примерной технологии избирательной предварительной зарядки согласно одному из вариантов осуществления раскрытия. Схема 80 включает в себя верхнюю разрядную линию 85, BLU, и инверсную верхнюю разрядную линию 87, BLBU, сконфигурированные для осуществления доступа к разрядным ячейкам 84. Дополнительно, схема 80 включает в себя нижнюю разрядную линию 86, BLL, и инверсную нижнюю разрядную линию 88, BLBL. Хотя разрядные ячейки 84 показаны присоединенными к верхним разрядным линиям 85, 87, разрядные ячейки 84 также могут быть присоединены к нижним разрядными линиям 86, 88. Схема 81 разрешения распределения заряда, сконфигурированная для активизации распределения заряда, привязана к сигналу мультиплексирования, MUX_STATE, и сигналу предварительной зарядки, PRECHRG, и выдает сигнал распределения заряда, CH_SH. Схема 81 разрешения распределения заряда включает в себя инвертер 812, привязанный к сигналу мультиплексирования, MUX_STATE, и логический элемент 814 NAND, присоединенный к выходу инвертера 812 и сигналу предварительной зарядки, PRECHRG, и инвертор 816, присоединенный к выходу логического элемента 814 NAND. Проиллюстрированная схема 81 разрешения распределения заряда является всего лишь одной из возможных комбинаций логических вентилей, способной к активизации распределения заряда. Схема 891 предварительной зарядки присоединена к верхним разрядным линиям 85, 87, а сбросная схема 892 присоединена к нижним разрядным линиям 86, 88. Схема 891 предварительной зарядки и разрядная схема 892 могут управляться сигналом предварительной зарядки, PRECHRG.

Сигнал распределения заряда, CH_SH, и сигнал выборки, SELn, вводятся в логический элемент 82 NOR для управления схемой 83 распределения заряда. Схема 83 распределения заряда активна, когда сигнал распределения заряда, CH_SH, находится в высоком состоянии. Когда схема 83 распределения заряда активна, верхняя разрядная линия 85 присоединена к нижней разрядной линии 86, а верхняя разрядная линия 87 присоединена к нижней разрядной линии 88. Сигнал выборки, SELn, используется для выборки разрядных ячеек для операций считывания или записи. Хотя показаны только один сигнал выборки, SELn, верхняя разрядная линия, BLU, инверсная верхняя разрядная линия, BLBU, нижняя разрядная линия, BLL, и инверсная нижняя разрядная линия, BLBL, гораздо большее количество может быть включено в схему 80. Дополнительно, гораздо большее количество разрядных ячеек может быть включено в схему 80.

Работа схемы 80 далее будет описана в соединении с временной диаграммой 70. В момент 711 времени сигнал предварительной зарядки, PRECHG, является низким, и сигнал мультиплексирования, MUX_STATE, является низким. Выходной сигнал схемы 81 разрешения распределения заряда, CH_SH, будет низким. Верхние разрядные линии 85, 87 предварительно заряжаются до напряжения питания, VDD, а нижние разрядные линии 86, 88 предварительно заряжаются до потенциала земли. В момент 712 времени после того, как сигнал предварительной зарядки, PRECHG, переходит в высокое состояние (деактивируя схему предварительной зарядки), наряду с тем, что сигнал мультиплексирования, MUX_STATE, остается низким, выходной сигнал схемы 81 разрешения распределения заряда, CH_SH, переходит в высокое состояние. Это заставляет логический элемент 82 NOR управлять схемами 83 распределения заряда для присоединения верхних разрядных линий 85, 87 к нижним разрядным линиям 86, 88, приводя к снижению напряжения на верхней разрядной линии, BLU, и инверсной верхней разрядной линии, BLBU. В момент 713 времени после того, как сигнал мультиплексирования, MUX_STATE, переходит в высокое состоянии, выходной сигнал схемы 81 разрешения распределения заряда, CH_SH, переходит в низкое состояние. Это изменение заставляет схемы 83 распределения заряда отсоединять верхние разрядные линии 85, 87 от нижних разрядных линий 86, 88, заканчивая распределение заряда. В момент 714 времени разрядные ячейки 84 подвергаются доступу (в ответ на сигнал линии записи, WL), и происходит операция считывания или записи.

Технология распределения заряда, как описано этим раскрытием, улучшает устойчивость считывания памяти посредством уменьшения напряжения разрядной линии от напряжения питания. Напряжение разрядной линии снижается предварительной зарядкой одного участка разрядной линии до первого напряжения, а второго участка разрядной линии до второго напряжения. Схема распределения заряда затем избирательно соединяет два участка, чтобы добиваться напряжения разрядной линии между первым и вторым напряжением. Итоговое напряжение является отчасти зависящим от относительной емкости двух участков разрядной линии, поэтому любое изменение производственного процесса в устройствах не оказывает влияния на операцию распределения заряда. В одном из вариантов осуществления, первый участок является верхней разрядной линией, а второй участок является нижней разрядной линией.

Одно из преимуществ этого раскрытия является улучшенной устойчивостью считывания благодаря снижению напряжения разрядной линии. Точный уровень напряжения может выбираться для разрядных линий. Как упомянуто выше, уменьшение напряжения разрядной линии улучшает статический запас помехоустойчивости (SNM) устройства памяти. Как подвергаемые доступу разрядные ячейки и полувыбранные разрядные ячейки улучшены, так как все разрядные линии принимают более низкое напряжение по сравнению с напряжением питания разрядной ячейки. Полувыбранные разрядные ячейки являются ячейками, выбранными утвержденной числовой линией, но не выбраны своими разрядными линиями.

Вторым преимуществом этого раскрытия является превосходная надежность конструкции. Раскрытие не зависит от порогового напряжения транзистора и привязки по времени решающего сигнала.

Третьим преимуществом этого раскрытия является устойчивость к изменению технологического процесса. Предложенное решение зависит от значений относительной емкости, которые не изменяются в зависимости от изменения технологического процесса, напряжения и температуры. Напряжение разрядной линии будет зависеть от условий технологического процесса.

Четвертым преимуществом этого раскрытия является гибкость конструкции. Значение напряжения разрядной линии может изменяться посредством выбора, какие участки разрядной линии следует предварительно заряжать до VDD, а какие участки разрядной линии следует предварительно заряжать до потенциала земли. Например, предварительная зарядка одной разрядной линии или более до потенциала земли может предоставить возможность большего значения допустимой ошибки (сдвига разрядной линии от VDD). Например, если напряжение питания имеет значение 1,125 вольт, и верхние участки имеют значение 1,125 вольт, и нижние отрезки имеют значение 1,125 вольт, то итоговым напряжением может быть 1,125 вольт, если все разрядные линии предварительно заряжаются до VDD. Допустимая ошибка составляла бы 0 милливольт в этом случае. Однако, в том же самом случае, если одна из разрядных линий предварительно заряжена до потенциала земли, то итоговое напряжение составляло бы 1,00 вольт. Допустимая ошибка составляла бы 125 милливольт в этом случае. Поэтому есть высокая степень гибкости касательно напряжений, до которых могут предварительно заряжаться участки разрядной линии.

Пятое преимущество этого раскрытия состоит в том, что используется только одно напряжение питания. Это упрощает высокоуровневое проектирование на физическом уровне и проверку памяти.

Устройство памяти, которое раскрыто, может быть присоединено к микропроцессору или другому микроэлектронному устройству. Устройство памяти может быть помещено в корпус с микропроцессором и, в дальнейшем, включено в устройство связи. Например, память может быть встроена в мобильный телефон или базовую станцию связи.

Фиг. 9 - структурная схема, иллюстрирующая АРМ проектировщика, используемый для проектирования схемы, компоновки и логики раскрытой полупроводниковой интегральной схемы. АРМ (автоматизированное рабочее место) 900 проектировщика включает в себя жесткий диск 901, содержащий в себе программное обеспечение операционной системы, файлы поддержки и программное обеспечение САПР (системы автоматизированного проектирования), такое как Cadence или OrCAD. АРМ 900 проектировщика также включает в себя дисплей для облегчения проектирования схемного решения 910. Схемное решение 910 может быть схемой памяти, как описанная выше. Запоминающий носитель 904 предусмотрен для материального хранения схемного решения 910. Схемное решение 910 может храниться на запоминающем носителе 904 в файловом формате, таком как GDSII или GERBER. Запоминающий носитель 904 может быть CD-ROM (ПЗУ на компакт-диске), DVD (многофункциональным цифровым диском), жестким диском, флэш-памятью или другим надлежащим устройством. Более того, АРМ 900 проектировщика включает в себя устройство 903 привода для приема входных данных с или записи выходных данных на запоминающий носитель 904.

Данные, записанные на запоминающем носителе 904, могут определять конфигурации логической схемы, данные шаблона для фотографических масок или данные шаблона маски для инструментальных средств последовательной записи, таких как электронно-лучевая литография. Данные дополнительно могут включать в себя данные логической проверки, такие как временные диаграммы или сетевые схемы, ассоциативно связанные с логическими моделированиями. Предоставление данных на запоминающем носителе 904 облегчает проектирование схемного решения 910, снижая количество последовательностей операций для конструирования полупроводниковых интегральных схем.

Хотя были подробно описаны настоящее раскрытие и его преимущества, должно быть понятно, что различные изменения, замены и переделки могут быть произведены в материалах настоящей заявки, не выходя из сущности и объема раскрытия, которые определены прилагаемой формулой изобретения. Например, хотя были описаны устройства памяти SRAM, технология избирательной предварительной зарядки может применяться к любой конструкции памяти, в том числе, но не в качестве ограничения, SRAM, DRAM или MRAM. Более того, объем настоящей заявки не подразумевается ограниченным конкретными вариантами осуществления технологического процесса, машины, производства, смеси веществ, средства, способов и этапов, описанных в описании изобретения. Как рядовой специалист в данной области техники без труда поймет из описания настоящего раскрытия, технологические процессы, машины, производство, смеси веществ, средства, способы или этапы, существующие сегодня или должные быть разработанными позже, которые выполняют по существу такую же функцию или достигают по существу такого же результата, как соответствующие варианты осуществления, описанные в материалах настоящей заявки, могут использоваться согласно настоящему раскрытию. Соответственно, прилагаемая формула изобретения подразумевается включающей в пределы своего объема такие технологические процессы, машины, производство, смеси материалов, средства, способы или этапы.

1. Устройство памяти, содержащее:первую разрядную линию, имеющую первый участок и второй участок; исхему распределения заряда, избирательно присоединяемую к первому участку и второму участку, в которой схема распределения заряда сконфигурирована для присоединения и отсоединения первого участка от второго участка.

2. Устройство памяти по п.1, в котором первый участок первой разрядной линии предварительно заряжается до первого напряжения, а второй участок первой разрядной линии предварительно заряжается до второго напряжения, отличного от первого напряжения.

3. Устройство памяти по п.2, в котором первый участок первой разрядной линии предварительно разряжается до напряжения земли, а второй участок первой разрядной линии предварительно заряжается до напряжения питания.

4. Устройство памяти по п.2, дополнительно содержащее вторую разрядную линию, имеющую первый участок и второй участок, в котором первый участок второй разрядной линии и второй участок второй разрядной линии предварительно заряжаются до первого напряжения.

5. Устройство памяти по п.1, дополнительно содержащее схему разрешения распределения заряда, сконфигурированную для активизации схемы распределения заряда, когда схема предварительной зарядки неактивна, и сигнал мультиплексирования указывает распределение заряда.

6. Устройство памяти по п.1, дополнительно содержащее разрядную ячейку, присоединенную к первому участку первой разрядной линии.

7. Устройство памяти по п.1, дополнительно