Операция записи для магниторезистивного оперативного запоминающего устройства с переносом спинового момента с уменьшенным размером ячейки бита

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в улучшении стабильности записи и уменьшении размеров ячейки битов в STT-MRAM. Магниторезистивное оперативное запоминающее устройство с переносом спинового момента (STT-MRAM), имеющее линии истока, причем каждая линия истока по существу расположена параллельно словарной шине, соединенной с первым рядом ячеек битов, при этом каждая линия истока расположена, по существу, перпендикулярно линиям битов, соединенным с первым рядом ячеек битов, причем устройство STT-MRAM содержит: средство для установления низкого напряжения в линии битов выбранной ячейки бита во время операции записи; средство для установления высокого напряжения в линиях битов невыбранных ячеек битов во время операции записи; селектор линий истока, соединенный со множеством линий выбора, каждая из линий выбора соединена с одной из множества линий истока, и выполненный с возможностью активировать линию выбора, и активированная линия выбора активирует линию истока; задающий модуль линии истока, соединенный с каждой из множества линий истока и выполненный с возможностью устанавливать высокое напряжение на активированной линии истока во время операции записи. 2 н. и 19 з.п. ф-лы, 18 ил.

Реферат

Область техники, к которой относится изобретение

Варианты осуществления изобретения относятся к оперативному запоминающему устройству (RAM, ОЗУ). Более конкретно, варианты осуществления изобретения относятся к операциям записи в магниторезистивном оперативном запоминающем устройстве с переносом спинового момента (STT-MRAM, МОЗУ-ПСМ).

Уровень техники

Оперативное запоминающее устройство (ОЗУ) представляет собой неотъемлемый компонент современных цифровых архитектур. ОЗУ могут представлять собой отдельные устройства или могут быть интегрированы или встроены в устройства, в которых используются ОЗУ, такие как микропроцессоры, микроконтроллеры, специализированные интегральные микросхемы (ASIC, СИМС), системы на кристалле (SoC, СнК) и другие устройства, как будет понятно. ОЗУ могут быть энергозависимыми или энергонезависимыми. Энергозависимые ОЗУ теряют сохраненную в них информацию всякий раз при отключении питания. Энергонезависимые ОЗУ могут поддерживать содержание своей памяти, даже когда отключают питание запоминающего устройства. Хотя энергонезависимое ОЗУ имеет преимущество, состоящее в возможности поддержания своего содержания без подключения питания, обычные энергонезависимые ОЗУ более медленно выполняют операции считывания/записи, чем энергозависимые ОЗУ.

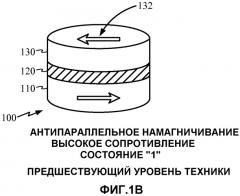

Магниторезистивное оперативное запоминающее устройство (MRAM) представляет технологии энергонезависимого запоминающего устройства, которое имеет время отклика (считывания/записи), сравнимое с энергозависимым запоминающим устройством. В отличие от обычных технологий ОЗУ, в которых данные сохраняют как электрические заряды или протекающие токи, в MRAM используются магнитные элементы. Как показано на фиг.1A и 1B, элемент 100 сохранения на основе магнитного туннельного перехода (MTJ, МТП) может быть сформирован из двух магнитных слоев 110 и 130, каждый из которых может содержать магнитное поле, отделенное изолирующим (туннельным переходом) слоем 120. К одному из двух слоев (например, к фиксированному слою 110) приложена определенная полярность. Полярность 132 другого из слоев (например, свободного слоя 130) может свободно изменяться так, чтобы она соответствовала внешнему полю, которое может быть приложено. Изменение полярности 132 свободного слоя 130 изменяет сопротивление элемента 100 сохранения MTJ. Например, когда полярности совмещены, фиг.1A, существует состояние низкого сопротивления. Когда полярности не совмещены, фиг.1B, существует состояние высокого сопротивления. Иллюстрация MTJ 100 была упрощена, и понятно, что каждый представленный слой может содержать один или больше слоев материалов, как известно в данной области техники.

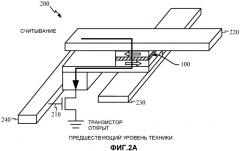

На фиг.2A показана ячейка 200 памяти обычного MRAM, представленная во время операции считывания. Ячейка 200 включает в себя транзистор 210, линию 220 бита, разрядную линию 230 и словарную шину 240. Ячейка 200 может выполнять считывание путем измерения электрического сопротивления MTJ 100. Например, определенный MTJ 100 может быть выбран путем активации ассоциированного транзистора 210, который может переключать ток из линии 220 бита через MTJ 100. В результате туннельного магниторезистивного эффекта электрическое сопротивление MTJ 100 изменяется на основе ориентации полярностей двух магнитных слоев (например, 110, 130), как описано выше. Сопротивление внутри любого конкретного MTJ 100 может быть определено по току, протекающему в результате полярности свободного слоя. Обычно, если фиксированный слой 110 и свободный слой 130 имеют одинаковую полярность, сопротивление будет низким и будет считан "0". Если фиксированный слой 110 и свободный слой 130 имеют противоположную полярность, сопротивление будет более высоким и будет считана "1".

На фиг.2B ячейка 200 памяти обычного MRAM представлена при выполнении операции записи. Операция записи MRAM представляет собой магнитную операцию. В соответствии с этим транзистор 210 закрыт во время операции записи. Ток протекает через линию 220 бита и разрядную линию 230 для установления магнитных полей 250 и 260, которые могут влиять на полярность свободного слоя MTJ 100 и, следовательно, на логическое состояние ячейки 200. В соответствии с этим данные могут быть записаны и сохранены в MTJ 100.

MRAM имеет ряд желательных характеристик, которые делают его кандидатом для использования в качестве универсальной памяти, таких как высокая скорость, высокая плотность (то есть малый размер ячейки бита), малое потребление энергии и отсутствие ухудшения характеристик с течением времени. Однако MRAM имеет проблемы масштабируемости. В частности, по мере того как ячейка битов становится меньшей, магнитные поля, используемые для переключения состояния памяти, увеличиваются. В соответствии с этим плотность тока и потребляемая мощность увеличиваются для обеспечения более сильных магнитных полей, ограничивая таким образом масштабируемость MRAM.

В отличие от обычного MRAM в магниторезистивном оперативном запоминающем устройстве с переносом спинового момента (STT-MRAM) используются электроны, спин которых становится поляризованным по мере того, как электроны протекают через тонкую пленку (фильтр спина). STT-MRAM также известно как RAM с переносом спинового момента (STT-RAM), RAM с переключением намагниченности с переносом спинового момента (спин RAM) и перенос спинового момента (SMT-RAM). Во время операции записи электроны с поляризованным спином прикладывают момент к свободному слою, что может переключить полярность свободного слоя. Операция считывания аналогична обычному MRAM в том, что ток используется для детектирования сопротивления/логического состояния элемента сохранения MTJ, как описано выше. Как показано на фиг.3A, ячейка 300 битов STT-MRAM включает в себя MTJ 305, транзистор 310, линию 320 битов и словарную шину 330. Транзистор 310 переключают для одной или обеих операций считывания и записи, обеспечивая протекание тока через MTJ 305 таким образом, что логическое состояние может быть считано или записано.

На фиг.3B показана более подробная схема ячейки 301 STT-MRAM для дальнейшего обсуждения операции считывания/записи. В дополнение к описанным выше элементам, таким как MTJ 305, транзистор 310, линия 320 битов и словарная шина 330, показаны линия 340 истока, усилитель 350 считывания, схема 360 считывания/записи и источник 370 опорного напряжения для линии битов. Как описано выше, операция записи в STT-MRAM является электрической. Цепь 360 считывания/записи генерирует напряжение записи между линией 320 битов и линией 340 истока. В зависимости от полярности напряжения между линией 320 битов и линией 340 истока полярность свободного слоя MTJ 305 может быть изменена, и, соответственно, логическое состояние может быть записано в ячейку 301. Аналогично, во время операции считывания генерируется ток считывания, который протекает между линией 320 битов и линией 340 истока через MTJ 305. Когда обеспечивается протекание тока через транзистор 310, сопротивление (логическое состояние) MTJ 305 может быть определено на основе разности напряжений между линией 320 битов и линией 340 истока, которую сравнивают с опорным напряжением 370 и затем усиливают с помощью усилителя 350 считывания. Следует понимать, что работа и конструкция ячейки 301 памяти известны в данной области техники. Дополнительные детали представлены, например, в публикации M.Hosomi et al., A Novel Nonvolatile Memory with Spin Transfer Torque Magnetoresistive Magnetization Switching: Spin-RAM, proceedings of IEDM conference (2005)М.), которая представлена здесь полностью в качестве ссылочного материала.

Электрическая операция записи STT-MRAM устраняет проблему масштабирования, связанную с операцией магнитной записи в MRAM. Кроме того, конструкция цепей становится менее сложной для STT-MRAM. В обычной компоновке массива STT-MRAM, такой как показана на фиг.4A, линия (SL) истока расположена ортогонально словарной шине (WL, ЧЛ) и параллельно линии (BL, ЛБ) бита. Такая компоновка увеличивает площадь, используемую для массива ячеек бита, в результате чего получается больший размер ячейки бита. В обычной компоновке обеспечивается стабильная операция записи. Например, во время операции записи для записи состояния "1" (или записи "1"), WL=H, BL=L и SL=H для выбранной ячейки 410 битов и может быть выполнена соответствующая операция записи. Как используется здесь, H представляет собой высокое напряжение/логический уровень и L представляет собой низкое напряжение/логический уровень. Для невыбранных ячеек 420 битов WL=H, BL=L и SL=L и таким образом не выполняются недействительные операции записи для невыбранных ячеек битов. Однако, хотя это помогает предотвратить недействительные операции записи, обычная компоновка неэффективна в области, используемой для ячейки битов, поскольку нельзя совместно использовать линию, в результате чего требуется использовать дополнительный металл 1 (например, SL(M1)) для линии истока, как показано на фиг.4B. Кроме того, как представлено в компоновке цепей на фиг.4B, каждая линия (BL) битов может быть расположена на другом металлическом слое (например, Mx), который продолжается, по существу, параллельно линиям истока.

Сущность изобретения

Примерные варианты осуществления изобретения направлены на системы, цепи и способы улучшения стабильности записи и уменьшения размеров ячейки битов в STT-MRAM.

Вариант осуществления изобретения может включать в себя магниторезистивное оперативное запоминающее устройство с переносом спинового момента (STT-MRAM), содержащее: массив ячеек бита, линия истока которого расположена, по существу, параллельно словарной шине, соединенной с первым рядом ячеек битов, в котором линия истока расположена, по существу, перпендикулярно линиям битов, соединенным с первым рядом ячеек битов.

Другой вариант осуществления изобретения может включать в себя способ, состоящий в том, что формируют массив ячеек битов магниторезистивного оперативного запоминающего устройства с переносом спинового момента (STT-MRAM), имеющий линию истока, расположенную, по существу, параллельно словарной шине первого ряда ячеек битов и, по существу, перпендикулярно линиям битов, соединенным с первым рядом ячеек битов.

Вариант осуществления изобретения может включать в себя способ для записи данных в магниторезистивном оперативном запоминающем устройстве с переносом спинового момента (STT-MRAM), линия истока которого, по существу, параллельна словарной шине, соединенной с первым рядом ячеек битов, в котором линия истока расположена, по существу, перпендикулярно линиям битов, соединенным с первым рядом ячеек битов, способ, состоящий в том, что устанавливают низкое напряжение в линии битов для выбранной ячейки битов, соединенной со словарной шиной первого ряда ячеек битов и линией истока, и устанавливают высокое напряжение в линиях битов среди невыбранных ячеек битов, соединенных со словарной шиной первого ряда ячеек битов и линией истока.

Другой вариант осуществления изобретения может включать в себя магниторезистивное оперативное запоминающее устройство с переносом спинового момента (STT-MRAM), имеющее линию истока, расположенную, по существу, параллельно словарной шине, соединенной с первым рядом ячеек битов, в котором линия истока расположена, по существу, перпендикулярно линии битов, соединенной с первым рядом ячеек битов, STT-MRAM содержит средство для установления низкого напряжения в линии битов выбранной ячейки бита, соединенной со словарной шиной первого ряда ячеек битов, и линией истока, и средство для установления высокого напряжения в линиях битов невыбранных ячеек битов, соединенных со словарной шиной в первом ряду ячеек битов и линией истока.

Краткое описание чертежей

Приложенные чертежи представлены для помощи при описании вариантов осуществления изобретения и предоставлены исключительно для иллюстрации вариантов осуществления, а не для их ограничения.

На фиг.1A и 1B показаны иллюстрации элемента сохранения с магнитным туннельным переходом (MTJ).

На фиг.2A и 2B показаны иллюстрации ячейки магниторезистивного оперативного запоминающего устройства (MRAM) во время операции считывания и записи соответственно.

На фиг.3A и 3B представлены иллюстрации ячеек битов магниторезистивного оперативного запоминающего устройства с переносом спинового момента (STT-MRAM).

На фиг.4A показана схема обычной компоновки ячеек битов для STT-MRAM, и на фиг.4B показана компоновка обычной компоновки ячейки бита для STT-MRAM.

На фиг.5 показана упрощенная схема ячейки бита для STT-MRAM.

На фиг.6A схематично показана иллюстрация компоновки ячейки битов с уменьшенным размером для STT-MRAM, в которой используется обычная логика записи, и на фиг.6B показана компоновка размещения ячейки бита с уменьшенным размером.

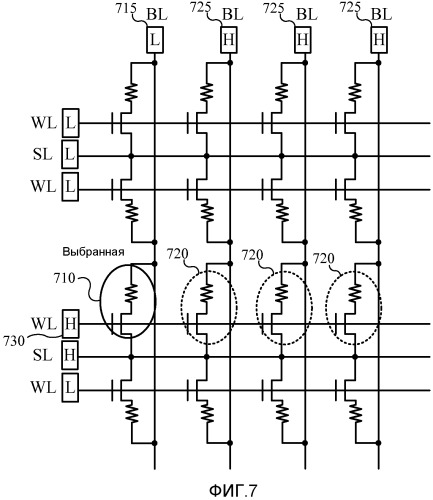

На фиг.7 показана иллюстрация компоновки ячейки битов с уменьшенным размером для STT-MRAM, включающей в себя уровни логики записи.

На фиг.8 представлена иллюстрация массива STT-MRAM.

На фиг.9 показана иллюстрация синхронизации соотношений передачи сигналов для блочной памяти в массиве STT-MRAM по фиг.8.

На фиг.10A показана иллюстрация селектора линии битов, который можно использовать в массиве STT-MRAM по фиг.8.

На фиг.10B показана иллюстрация задающего модуля линии битов, которую можно использовать в массиве STT-MRAM по фиг.8.

На фиг.11A представлена иллюстрация комбинированного задающего устройства словарной шины и селектора линии истока, которые можно использовать в массиве STT-MRAM по фиг.8.

На фиг.1B показана иллюстрация задающего модуля линии истока, который можно использовать в массиве STT-MRAM по фиг.8.

Подробное описание изобретения

Аспекты вариантов осуществления изобретения раскрыты в следующем описании и показаны на соответствующих чертежах, которые направлены на определенные варианты осуществления изобретения. Альтернативные варианты осуществления могут быть сформулированы без выхода за пределы объема изобретения. Кроме того, хорошо известные элементы изобретения не будут подробно описаны или их описание будет исключено с тем, чтобы не загромождать соответствующие детали вариантов осуществления изобретения.

Слово "примерный", используемое здесь, означает "использование в качестве примера, отдельного случая или иллюстрации". Любой вариант осуществления, описанный здесь как "примерный", не обязательно должен рассматриваться как предпочтительный или преимущественный по сравнению с другими вариантами осуществления. Аналогично, термин "варианты осуществления изобретения" не требует, чтобы все варианты осуществления изобретения включали в себя описанные свойства, преимущества или режим работы.

Используемая здесь терминология предназначена только для описания определенных вариантов осуществления и не должна ограничивать варианты осуществления изобретения. Используемые здесь формы единственного числа предназначены также для включения форм множественного числа, если только в контексте не будет четко обозначено другое. Как будет также понятно, термины "содержит", "содержащий" "включает в себя" и/или "включающий в себя", когда их используют здесь, устанавливают присутствие указанных свойств, целых чисел, этапов, операций, элементов и/или компонентов, но не исключают присутствие или добавление одного или больше других свойств, целых чисел, этапов, операций, элементов, компонентов и/или их групп.

Кроме того, варианты осуществления могут быть описаны в виде последовательности действий, которые должны быть выполнены, например, элементов вычислительного устройства. Следует понимать, что различные действия, описанные здесь, могут быть выполнены с использованием конкретных цепей (например, специализированных интегральных схем (ASIC)), с помощью программных инструкций, выполняемых одним или больше процессорами, или с использованием комбинации обоих подходов. Кроме того, эти последовательности действий, описанные здесь, можно рассматривать, как воплощенные исключительно в любой из форм считываемого компьютером носителя записи, на котором записан соответствующий набор компьютерных инструкций, которые при исполнении могут привести к выполнению ассоциированным процессором функций, описанных здесь. Таким образом, различные аспекты изобретения могут быть осуществлены в виде множества разных форм, все из которых рассматриваются как находящиеся в пределах объема заявленного предмета изобретения. Кроме того, для каждого из вариантов осуществления, описанных здесь, соответствующая форма любых таких вариантов осуществления может быть описана здесь, как, например, "логические схемы, сконфигурированные" для выполнения описанного действия.

На фиг.5 показана упрощенная схема ячейки бита STT-MRAM. Ячейка бита включает в себя словарную шину (WL), соединенную с транзистором 510 словарной шины. Элемент 520 сохранения (например, MTJ) представлен как простое сопротивление. Транзистор 510 и элемент 520 сохранения расположены между линией (BL) бита и линией (SL) истока. Во время операции записи для состояния "0", WL=H, BL=H и SL=L и для состояния "1", WL=H, BL=L и SL=H. Как используется здесь, H обозначает высокое напряжение/логический уровень, и L обозначает низкое напряжение/логический уровень. Уровни напряжения могут представлять собой уровни напряжения истока питания (например, Vdd и 0) или могут быть выше или ниже, чем уровни напряжений источников питания. Следует понимать, что описанные выше компоновки и состояния представлены исключительно для описания вариантов осуществления изобретения и не предназначены для ограничения вариантов осуществления иллюстрируемыми компоновками или описанными состояниями.

На фиг.6A показана компоновка массива ячеек бита STT-MRAM в соответствии с вариантом осуществления изобретения, которая обеспечивает возможность получения уменьшенного или минимального размера ячейки битов. В отличие от обычной конструкции, такой, как показана на фиг.4, числовые линии (WL) и линии (SL) истока расположены, по существу, параллельно и, по существу, перпендикулярно линиям (BL) битов. Например, при сравнении с компоновкой, показанной на фиг.4B, вертикальный металл 1, который расположен параллелью линии битов и перпендикулярно словарной шине, используемый для линии истока, может быть устранен, и, таким образом, область ячейки бита может быть существенно уменьшена, как показано на фиг.6B. При сравнении с фиг.4B, очевидно, что линии истока (например, SL (М1) больше не расположены параллельно линиям бита. В соответствии с этим конфигурация, показанная на фиг.6B, обеспечивает возможность уменьшения размера ячейки благодаря обеспечению возможности удаления дополнительных параллельных металлических линий и соединений, используемых для линии истока, показанной на фиг.4B. Кроме того, при использовании представленной компоновки линия истока может совместно использоваться для всех ячеек вдоль заданного направления словарной шины. В некоторых вариантах осуществления изобретения линии истока могут совместно использоваться между двумя соседними ячейками битов и могут быть расположены между линиями слов (например, WL (GP)), как показано на иллюстрации.

Однако, используя обычную логику для операций записи, формируется потенциально недействительная операция записи в невыбранных ячейках 620. Например, при операции записи "1" выбранная ячейка 610 имеет WL=H, BL=L и SL=H. Однако невыбранная ячейка 620 бита также подвергается недействительной записи, поскольку каждая из них будет иметь аналогичные приложенные сигналы (то есть WL=H, BL=L и SL=H). В соответствии с этим при использовании обычной логики записи в конструкции ячейки бита с уменьшенным размером возникают проблемы во время операций записи в память.

На фиг.7 иллюстрируется решение описанных выше проблем для операций записи в конструкциях ячейки битов с уменьшенным размером (например, параллельно WL и SL) для STT-MRAM в соответствии с вариантами осуществления изобретения. На фиг.7 показаны невыбранные линии 725 битов, управление которыми может осуществляться с переводом в высокое состояние во время операции записи "1" для решения проблемы недействительных операций записи для невыбранных ячеек 720 битов. Например, при записи "1" в выбранную ячейку 710 битов логика записи устанавливает WL(730)=H, BL(715)=L и SL(740)=H. В соответствии с этим невыбранные ячейки 720 битов также имеют WL(730)=H и SL(740)=H во время операции записи в ячейку 710 бита. Тогда, для предотвращения недействительной операции записи в невыбранных ячейках 720 битов невыбранные BL 725 устанавливают в состояние H во время цикла записи для записи "1" в выбранную ячейку 710 битов. Следует понимать, что логика управления записью для невыбранных линий битов будет разработана так, чтобы применять высокое значение (H) сигнала напряжения/логического сигнала во время операций записи. В качестве альтернативы, невыбранные линии битов могут быть помещены в состоянии высокого импеданса, что предотвращает любое протекание тока через невыбранные линии битов. Логика управления записью может быть воплощена с использованием любого устройства или комбинации устройств, которые могут выполнять описанные здесь функции. В соответствии с этим варианты осуществления изобретения не ограничиваются конкретными цепями или логическими схемами, представленными здесь для выполнения описанных функций.

На фиг.8 представлен пример массива STT-MRAM. Как отмечено выше, невыбранные линии (BL) битов в массиве установлены в высокое состояние, в то время как выбранные BL, ассоциированные с ячейками 801 и 811, установлены в низкое состояние в одной конфигурации записи. Выбранные сигналы обозначены прямоугольниками, и выбранные ячейки обозначены кружком. В соответствии с этим для выбора ячеек 801 и 811 битов задающий модуль 820 словарной шины (WL) активирует WL1 821. WL1 821 активирует транзистор доступа (словарную шину), ассоциированный с ячейками 801, 811 и другими ячейками вдоль словарной шины 821. Аналогично, селектор линий 830 истока активирует линию 831 выбора, соединенную с линиями SL01 и SL11 истока. В частности, линия 831 выбора активирует транзисторы, ассоциированные с линиями SL01 и SL11 истока, которые соединены с задающими модулями линии 803 и 813 истока соответственно. Кроме того, селекторы 804 и 814 линии битов выбирают задающие модули 802 и 812 линии битов соответственно. Как отмечено выше для этого примера, задающие модули 802 и 812 линии битов могут быть установлены в низкий уровень, и оставшиеся невыбранные задающие модули линии битов могут быть установлены в высокий уровень. В соответствии с этим ячейки 801 и 811 битов могут быть выбраны из массива 800. Хотя в описанном выше примере представлены конкретные ячейки, выбранные в массиве для блока 0 и блока 1, следует понимать, что любая ячейка может быть выбрана с использованием представленной логики. Кроме того, ячейки в обоих блоках не обязательно должны быть выбраны. Кроме того, следует понимать, что размеры массива являются произвольными и могут быть изменены в сторону увеличения или уменьшения в соответствии с необходимостью, и различные задающие модули/селекторы могут быть переконфигурированы для обеспечения большей или меньшей разрешающей способности при выборе отдельных ячеек битов. Более подробное описание конкретных вариантов осуществления представленных логических блоков предусмотрено ниже. Однако эти детали представлены как примеры и не предназначены для ограничения вариантов осуществления изобретения иллюстрируемыми цепями, логическими схемами или описанными свойствами.

На фиг.9 иллюстрируется временная диаграмма для сигналов, относящихся к блоку 0 на фиг.8. Кроме того, ниже приведен список условий для различных сигналов на основе предположений, что линия (BL) битов/линия (SL) истока заранее заряжены в состоянии 0 или низкого уровня и что ячейки выбраны, как представлено на фиг.8.

• Запись данных L

o Выбранная BL=H

o Невыбранные BL = Неподключенный L

o Сигнал выбора BL для выбранной BL=H

o Сигнал выбора BL для невыбранной BL=L

o Выбранная SL=L

o Невыбранная SL = Неподключенный L

o Сигнал выбора SL для выбранной SL=H

o Сигнал выбора SL для невыбранной SL=L

• Запись данных H

o Выбранная BL=L

o Невыбранные BL=H

o Сигнал выбора BL для выбранной BL=H

o Сигнал выбора BL для невыбранной BL=H

o Выбранная SL=H

o Невыбранная SL = Неподключенный L

o Сигнал выбора SL для выбранной SL=H

o Сигнал выбора SL для невыбранной SL=L.

Как отмечено выше, H представляет собой высокое напряжение/логический уровень, и L представляет собой низкое напряжение/логический уровень, и эти уровни могут представлять собой уровни напряжения истока питания или могут быть выше или ниже, чем уровни напряжения истока питания. Термин неподключенный L, в общем, обозначает, что линия имела низкое напряжение перед ее отключением от истока низкого напряжения.

Приведенные выше списки предоставлены исключительно для иллюстрации и совместно с иллюстрируемыми сигналами синхронизации, показанными на фиг.9, иллюстрируют описываемый выбор ячеек битов блока 0 на фиг.8. Например, как описано выше, для невыбранных линий битов (например, BL00, BL02, BL03) установлен высокий уровень, для выбранных линий битов (например, BL01) установлен низкий уровень, и для ассоциированной линии истока (SL00) установлен высокий уровень при записи данных "H" или "1". В отличие от этого при записи данных "L" или "0" для невыбранных линий битов (например, BL00, BL02, BL03) установлен низкий уровень, для выбранной линии бита (например, BL01) установлен высокий уровень, и для ассоциированной линии истока (SL00) установлен низкий уровень. Также представлены соответствующие сигналы для задающего блока линии бита (задающий блок BL), сигналы выбора линии битов (выбор BL), задающего блока линии истока (задающий блок SL) и выбора линии истока (выбор SL). Схемы и логические цепи для воплощения этих функций будут более подробно описаны ниже. В соответствии с этим подробное описание каждого сигнала не будет предусмотрено. Следует также отметить, что разные данные (данные L или данные H) могут быть записаны в блок 0 и блок 1. Например, для записи данных L в блок 0 и записи H в блок 1 можно применять запись сигналов L данных, временные характеристики, представленные на фиг.9, можно применять для блока 0 и сигналов записи данных для записи H, а временные характеристики, показанные на фиг.9, можно применять для блока 1.

На фиг.10А иллюстрируется пример цепи селектора линии бита. Например, используя входы (CAi и CAj) адреса столбца и их дополнения (CAib, CAjb) как входы для логических элементов 841 "НЕ-И", в комбинации с инверторами 842, логические элементы 843 "НЕ-ИЛИ", инверторы 844 и сигнал DH0 данных (высокий уровень (H) данных в блоке 0), соответствующая линия битов может быть выбрана и может быть предусмотрен некоторый уровень (например, H/L). Например, вход из двух битов CAi, j (00, 01, 10, 11) можно использовать для выбора одной из четырех линий битов. Логический сигнал данных с высоким уровнем можно размещать в буфер с помощью инверторов 845 и затем предоставлять в логические элементы 843 "НЕ-ИЛИ" вместе с выходом инверторов 842. В соответствии с этим, когда сигнал DH0 данных имеет высокий уровень, выход всех логических элементов 843 "НЕ-ИЛИ" будет равен 0 (низкий), и соответствующий выход инверторов 844 будет высоким. Однако, когда выход сигнала DH0 данных низкий, выходом логических элементов 843 "НЕ-ИЛИ" управляют с помощью выхода инверторов 842 (на основе ввода адресов столбца), с помощью которого также управляют выходом инверторов 844. В соответствии с этим сигналы могут быть сконфигурированы таким образом, что выход логических элементов 843 "НЕ-ИЛИ" будет предоставлен в инверторы 844 так, что только одна ячейка бита будет выбрана (или установлена в другое значение, чем остающиеся сигналы выбора линии битов). Выходы (BLse100-BLse103) селектора 804 линии битов предоставляют в транзисторы последовательно с соответствующими задающими модулями линии битов (например, задающим модулем BL 00-03) для включения соответствующих линий битов.

Например, когда уровень DH0 низкий, схема имеет такую конфигурацию, что происходит запись данных "0" в ячейку. Выбранная BL имеет высокий уровень, и линия истока имеет низкий уровень. Кроме того, все линии истока ячеек, в которых используются выбранные WL, имеют низкий уровень. Для невыбранных ячеек линии битов должны иметь низкий уровень для предотвращения записи недействительных данных "0" в невыбранные ячейки. Таким образом, выбранная линия битов имеет высокий уровень, в то время как остальные линии имеют низкий уровень, что представляет собой состояние, противоположное тому, что показано на фиг.7.

На фиг.10B показан пример задающего модуля линии битов. Сигналы (например, CAibjb, CAibj, CAijb, CAij), выведенные из входов адреса столбца (CAi и CAj), и их дополнения (CAib, CAjb) могут быть предоставлены как входы в задающие модули линии битов (например, 802). Например, эти сигналы могут быть отдельно выведены или могут быть получены из логических элементов 841 по фиг.10A. Инверторы 852 соединены между входными узлами 851 и транзисторами (или переключателями) 853(b). Другие каналы передачи сигналов предусмотрены между входными узлами 851 и транзисторами 853(a). Транзисторы 853(a) и 853(b) также соединены с инверторами 854. Сигнал DH0 данных используется для обеспечения как дополняющего сигнала (DH0b), так и недополняющего сигнала (Dh0d), которые подают на входы (затворы) транзисторов 853(b) и 853(a) соответственно. В соответствии с этим, когда DH0 имеет низкий уровень, дополняющий канал через 853(b) является активным, и когда DH0 имеет высокий уровень, недополняющий канал через 853(a) является активным. Таким образом, соответствующий уровень линии битов (например, H/L) может быть предусмотрен для каждого задающего модуля линии битов (задающий модуль BL 00/01/02/03). Например, если DH0=0 (когда данные записи имеют уровень L), тогда BL00d=CAibjb/BL01d=CAibj/BL02d=CAijb/CA03d=CAij. Только одна из BL00d/01d/02d/03d имеет высокий уровень, поскольку только одна из CAibjb/CAibj/CAijb/Caij имеет высокий уровень. Однако, если DH0=1 (когда данные записи имеют уровень H) BL00d = дополнение CAibjb)/BL01d = дополнение (CAibj)/BL02d = дополнение (CAijb)/CA03d = дополнение (CAij). В соответствии с этим только одна из BL00d/01d/02d/03d будет иметь низкий уровень, поскольку только одна из CAibjb/CAibj/CAijb/Caij имеет высокий уровень.

На фиг.11A иллюстрируется пример схемы, которую можно использовать для задающего модуля словарной шины (например, 820) и также для селектора линии истока (например, 830). Например, предположим, четыре числовые линии и две линии истока выбраны, как показано на чертеже, логические элементы 825 "НЕ-И" могут принимать входные адреса i и j в ряду (RAi и RAj) и их дополнения. Выходы логических элементов 825 "НЕ-И" передают в инверторы 826 для инвертирования и размещения в буфере сигнала и управления соответствующей словарной шиной. Выходы логических элементов 825 "НЕ-И" также передают в парах в логические элементы 835 "НЕ-И" для выбора соответствующей линии истока. Поскольку линии истока совместно используются между двумя ячейками, селектор линии истока может быть выполнен так, чтобы он включался, когда включена любая из двух соседних числовых линий. Однако описанная схема также может быть скомпонована в двух или больше независимых схемах. Например, входы i и j адреса (RAi и Raj) могут быть непосредственно подключены к цепи выбора истока, содержащей логические элементы 825 "НЕ-И" и логические элементы 835 "НЕ-И", и логические элементы 835 "НЕ-И" могут быть исключены из схемы задающего модуля словарной шины. В соответствии с этим варианты осуществления изобретения не ограничены представленными для иллюстрации конфигурациями, содержащимися здесь.

На фиг.11B показан пример задающего модуля линии истока. Этот задающий модуль может принимать сигнал DH0, который размещают в буфер с помощью инвертора 836. Поскольку имеется два инвертора, включенные последовательно, DH0 не инвертируется задающим модулем 803 линии истока, как показано на чертеже. Однако следует понимать, что эта конфигурация может быть заменена одиночным неинвертирующим усилителем/задающим модулем. Аналогично, любая из описанных выше цепей может быть модифицирована с использованием компонентов, известных в области техники, для достижения аналогичных функций. В соответствии с этим описанные здесь варианты осуществления представлены просто для удобства представления примеров и пояснения и не предназначены для ограничения объема вариантов осуществления изобретения.

Учитывая описанное выше, также следует понимать, что варианты осуществления изобретения включают в себя способы, этапы, действия, последовательности, алгоритмы и/или процессы для достижения описанных здесь функций. Например, вариант осуществления может включать в себя способ формирования массива STT-MRAM, имеющего конфигурацию совместно используемой линии истока. В соответствии с этим вариант осуществления может включать в себя способ, содержащий формирование массива ячеек битов магниторезистивного оперативного запоминающего устройства с переносом момента спина (STT-MRAM), имеющего линию истока, расположенную, по существу, параллельно словарной шине в первом ряду ячеек битов и, по существу, перпендикулярно линии битов. Аспекты могут дополнительно включать в себя формирование словарной шине второго ряда ячеек битов, по существу, параллельно словарной шине; и соединение линии истока с ячейками битов, которые соединены с одной из числовых линий первого и второго ряда ячеек битов. Варианты осуществления для записи в массиве запоминающего устройства могут включать в себя установление низкого напряжения в линии битов для выбранной ячейки бита, соединенной со словарной шиной, и в линии истока и установление высокого напряжения в линиях битов для невыбранных ячеек битов, соединенных со словарной шиной первых ячеек битов, и в линии истока (см., например, фиг.7 и 9).

Хотя в представленном выше раскрытии показаны иллюстративные варианты осуществления изобретения, следует отметить, что различные изменения и модификации могут быть выполнены здесь без выхода за пределы объема вариантов осуществления изобретения, как определено приложенной формулой изобретения. Функции, этапы и/или действия способов в соответствии с описанными здесь вариантами осуществления изобретения не обязательно должны быть выполнены в каком-либо конкретном порядке. Кроме того, хотя элементы изобретения могут быть описаны или заявлены в единичном числе, предусматривается возможность их множественного числа, если только ограничение единственным числом не будет явно установлено.

1. Магниторезистивное оперативное запоминающее устройство с переносом спинового момента (STT-MRAM), имеющее линии истока, причем каждая линия истока, по существу, расположена параллельно словарной шине, соединенной с первым рядом ячеек битов, при этом каждая линия истока расположена, по существу, перпендикулярно линиям битов, соединенным с первым рядом ячеек битов, устройство STT-MRAM, содержащее:средство для установления низкого напряжения в линии битов выбранной ячейки бита во время операции записи, причем выбранная ячейка бита соединена со словарной шиной в первом ряду ячеек битов и линией истока;средство для установления высокого напряжения в линиях битов невыбранных ячеек битов во время операции записи, причем невыбранные ячейки битов соединены со словарной шиной в первом ряду ячеек битов и линией истока;при этом устройство STT-MRAM дополнительно содержит:селектор линий истока, соединенный со множеством линий выбора, каждая из линий выбора соединена с одной из множества линий истока, причем селектор линий истока выполнен с возможностью активировать линию выбора, и активированная линия выбора активирует линию истока;задающий модуль линии истока, соединенный с каждой из множества линий истока, причем задающий модуль линии истока выполнен с возможностью устанавливать высокое напряжение на активированной линии истока во время операции записи.

2. STT-MRAM по п.1, дополнительно содержащее:словарную шину, соединенную со вторым рядом ячеек битов, в котором линия истока соединена со вторым рядом ячеек битов.

3. STT-MRAM по п.1, в котором линия истока расположена между словарной шиной первого ряда ячеек битов и словарной шиной второго ряда ячеек битов.

4. STT-MRAM по п.1, в котором высокое напряжение представляет собой уровень истока питания, и низкое напряжение представляет собой уровень земли.

5. STT-MRAM по п.1, в котором средство для установления низкого напряжения в линии битов выбранной ячейки содержит:логическую схему выбора линии бита, соединенную с множеством задающих модулей линии бита.

6. STT-MRAM по п.5, в котором логическая схема выбора линии битов выполне