Подложка матрицы и жидкокристаллическая панель отображения

Иллюстрации

Показать всеНастоящее изобретение относится к (i) подложке матрицы, в которой элементы тонкопленочных транзисторов (TFT) и другие компоненты обеспечиваются на изолирующей подложке, и (ii) жидкокристаллической панели отображения, изготовленной с подложкой матрицы. Жидкокристаллическая панель отображения содержит подложку матрицы, содержащую: изолирующую подложку, имеющую область отображения и ее окружающую область; переключающие элементы, размещенные в виде матрицы на изолирующей подложке; пиксельные электроды, размещенные в виде матрицы в области отображения изолирующей подложки и соединенные с переключающими элементами; и схемы возбуждения для возбуждения переключающих элементов. Причем схемы возбуждения обеспечиваются в окружающей области и содержат множество столбцовых групп, размещенных в направлении от краевой стороны изолирующей подложки к области отображения, причем каждая из столбцовых групп имеет продольную сторону вдоль краевой стороны изолирующей подложки и содержит множество строчных групп, соответствующих строкам пиксельных электродов, размещенных в виде матрицы, и каждая имеет множество элементов возбуждения. Множество магистральных линий, проходящих вдоль краевой стороны изолирующей подложки в окружающей области, причем по меньшей мере одна из магистральных линий обеспечивается между соседними столбцовыми группами; ответвительные линии, обеспечиваемые в окружающей области, каждая из которых соединяет магистральную линию с элементом возбуждения; и соединительные линии, каждая из которых проходит от представляющей интерес ответвительной линии для электрического соединения представляющей интерес ответвительной линии с элементом возбуждения, обеспечиваемым в строчной группе, отличной от строчной группы, где обеспечивается элемент возбуждения, соединенный с представляющей интерес ответвительной линией. 2 н. и 10 з.п. ф-лы, 13 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к (i) подложке матрицы, в которой элементы тонкопленочных транзисторов (TFT) и другие компоненты обеспечиваются на изолирующей подложке, и (ii) жидкокристаллической панели отображения, изготовленной с подложкой матрицы.

Уровень техники

Устройства отображения с активной матрицей, снабженные тонкопленочными транзисторами (ниже в данном документе упоминаемыми как «TFT») в качестве переключающих элементов для пикселей, которые имеют высокое быстродействие и легко обеспечивают отображение с многоуровневой серой шкалой, использовались в многочисленных устройствах, включая телевизионный приемник, мобильный телефон, портативную игровую машину и навигационную систему для установки на транспортном средстве.

В типовом устройстве отображения с активной матрицей, подложка матрицы TFT и противоподложка противоположны друг другу, и элемент отображения (жидкий кристалл, органическая электролюминесценция и т.д.) уплотняется уплотняющим материалом между подложкой матрицы TFT и противоподложкой.

(Подложка матрицы TFT)

Нижеследующее описывает конструкцию подложки матрицы TFT с ссылкой на фиг.12.

Фиг.12 представляет собой вид сверху, схематически изображающий конструкцию существенной части подложки матрицы TFT.

Как показано на фиг.12, подложка 20 матрицы TFT имеет область 22 отображения, образованную в ее центральной части, и элементы TFT использования возбуждения отображения (переключающие элементы) (не показаны) для возбуждения пиксельных электродов образованы матричным образом в области 22 отображения.

Что касается элемента TFT использования возбуждения отображения, электрод затвора соединен с линией 42 затвора, электрод истока соединен с линией 44 истока, и электрод стока соединен с пиксельным электродом (не показан).

Линии 42 затвора и линии 44 истока обеспечиваются в направлениях, ортогональных друг к другу на подложке 20 матрицы TFT. Следует отметить, что линии 42 затвора и линии 44 истока обеспечиваются в разных слоях, расположенных на подложке 20 матрицы TFT, при помощи изолирующего слоя, вставленного между ними, так что линии 42 затвора и линии 44 истока электрически не соединены друг с другом в их пересечении.

В области, окружающей область 22 отображения, т.е. в области около краевой стороны 26 подложки на подложке 20 матрицы TFT, образована окружающая область 24. На правом и левом краях окружающей области 24 (в направлении, указанном стрелкой Х на фиг.12) обеспечивается схема 60 возбуждения затвора.

Схема 60 возбуждения затвора электрически соединена с линиями 42 затвора и прикладывает сигналы затвора к линиям 42 затвора.

Схема 60 возбуждения затвора обеспечивается на правом и левом краях окружающей области 24. Поэтому, в случаях, когда каждая из линий 42 затвора принимает сигналы с ее обоих краев, можно уменьшить искажение формы волны сигналов. Это делает возможным уменьшить размеры множества элементов TFT (элементов возбуждения), составляющих схему 60 возбуждения затвора, таким образом обеспечивая жидкокристаллическую панель 10 отображения, имеющую узкую рамку изображения.

Кроме того, даже в случаях, когда каждая из линий 42 затвора принимает сигналы только от одного края, размеры правой и левой зон рамки изображения жидкокристаллической панели 10 отображения могут быть сделаны равными посредством разделения линий 42 затвора на (а) группу линий 42 затвора, которая возбуждается схемой 60 возбуждения затвора правой стороны, и (b) группу линий 42 затвора, которая возбуждается схемой возбуждения затвора левой стороны.

В то же время, на одном крае верхних и нижних краев окружающей области 24 (в направлении, указанном стрелкой Y на фиг.12) обеспечивается драйвер 62.

Драйвер 62 электрически соединен с линиями 44 истока и прикладывает сигналы истока к линиям 44 истока.

Кроме того, обе схемы 60 возбуждения затвора электрически соединены соответственно с линиями схемы возбуждения затвора, которые содержат линию синхронизации и другие линии. На линии схемы возбуждения затвора сигналы, необходимые для работы схемы 60 возбуждения затвора, подаются от преобразователя постоянного тока (DC/DC) и схемы управления отображением, которые расположены вне подложки 20 матрицы TFT, при помощи гибких печатных плат (FPC) или т.п.

Следует отметить, что линии схемы возбуждения затвора (не показаны) схемы 60 возбуждения затвора правой стороны и линии 46 схемы возбуждения затвора схемы 60 возбуждения затвора левой стороны соединены между собой при помощи линий 64, например, на стороне области 22 отображения, противоположной ее стороны, на которой обеспечивается драйвер 62.

Соединение между обеими линиями схемы возбуждения затвора устраняет необходимость подачи сигналов как на линии схемы возбуждения затвора (не показаны) схемы 60 возбуждения затвора правой стороны, так и на линии 46 схемы возбуждения затвора схемы 60 возбуждения затвора левой стороны при помощи FPC. Поэтому, можно образовать FPC с узкой шириной и, таким образом, снизить стоимость FPC. Следует отметить, что, как показано на фиг.12, предпочтительно, что линии 64 выполнены без возможности соединения с линиями 44 истока с точки зрения эффекта снижения сигнальной нагрузки.

На фиг.12 схемы 60 возбуждения затвора обеспечиваются на обоих сторонах области 22 отображения. Альтернативно, схема 60 возбуждения затвора может обеспечиваться на одной стороне области 22 отображения. Кроме того, сигналы, подаваемые на линии 46 схемы возбуждения затвора, могут подаваться от драйвера 62.

Подложка 20 матрицы TFT и противоподложка (не показана) соединены друг с другом при помощи уплотнения 90, которое составляет жидкокристаллическую панель 10 отображения. Уплотнение 90 обеспечивается в форме рамки изображения на внутренней области подложки 20 матрицы TFT по краевой стороне 26 подложки у подложки 20 матрицы TFT.

(Патентная литература 1)

Конкретная конструкция схемы 60 возбуждения затвора, например, представляет собой конструкцию, описанную в патентной литературе 1.

Фиг.13 представляет собой блок-схему, схематически изображающую конструкцию схемы 60 возбуждения затвора, описанную в патентной литературе 1.

Как показано на фиг.13, в окружающей области 24 обеспечиваются линии 46 схемы возбуждения затвора, соединенные со схемой 60 возбуждения затвора и FPC (не показана).

Линиями 46 схемы возбуждения затвора, обеспечиваемыми по направлению Y подложки 20 матрицы TFT, являются: линия 70 источника питания с низким потенциалом в качестве магистральной линии, первая линия 72 синхронизации в качестве магистральной линии, вторая линия 74 синхронизации в качестве магистральной линии и линия 76 инициализации в качестве магистральной линии.

Следует отметить, что эти четыре линии, т.е. линия 70 источника питания с низким потенциалом, первая линия 72 синхронизации, вторая линия 74 синхронизации и линия 76 инициализации, все обеспечиваются между схемой 60 возбуждения затвора и краевой стороной 26 подложки, т.е. вне схем 60 возбуждения затвора.

Схема 60 возбуждения затвора включает в себя множество каскадов ST, которые подсоединены друг к другу каскадным образом и последовательно выводят сигналы затвора на линии 42 затвора. Следует отметить, что каскады ST подсоединены к линиям затвора (не показаны) как одни к одному. Конкретно, каскады ST подсоединены друг к другу каскадным образом. Например, клемма установки (не показана) в j-ом каскаде ST(j) принимает выходной сигнал переноса от предыдущего каскада ST(j-1), и клемма сброса (не показана) принимает выходной сигнал затвора от последующего каскада ST(j+1).

Линии 46 схемы возбуждения затвора и схема 60 возбуждения затвора электрически соединены друг с другом при помощи ответвительных линий 78, проходящих в поперечном направлении (направлении Х).

Нижеследующее описывает дополнительные подробности схемы 60 возбуждения затвора.

Каждый из каскадов ST, составляющих схему 60 возбуждения затвора, включает в себя элементы T1-T13 и T15 TFT.

Например, в каскаде ST(j-1) в (j-1)-ой строке элемент T4 TFT располагается на верхней стороне, чтобы находиться рядом с предыдущим каскадом ST(j-2), и принимает сигнал переноса от предыдущего каскада ST(j-2).

Элементы T1, T7, T10, T12 и T15 TFT располагаются вдоль ответвительной линии 78 в качестве соединительной линии к первой линии 72 синхронизации и принимают сигналы синхронизации с первой линии 72 синхронизации.

Элементы T11 и T5 TFT располагаются вдоль ответвительной линии 78 в качестве соединительной линии ко второй линии 74 синхронизации и принимают сигналы синхронизации со второй линии 74 синхронизации.

Элемент T6 TFT располагается вдоль ответвительной линии 78 в качестве соединительной линией к линии 76 инициализации и принимает сигнал инициализации с линии 76 инициализации.

Элементы Т2, Т3, Т8, Т9 и Т13 TFT располагаются вдоль ответвительной линии 78 в качестве соединительной линии к линии 70 источника питания с низким потенциалом и принимают сигналы низкого потенциала для отключения затворов элементов TFT от линии 70 источника питания с низким потенциалом.

Список ссылок

Патентная литература 1

Публикация заявки на патент Японии, Токукай, № 2006-039524 А (дата публикации: 9 февраля 2006 г.).

Патентная литература 2

Публикация нерассмотренной заявки на патент Японии (перевод заявки PCT) № 2005-527856 А (дата публикации: 15 сентября 2005 г.).

Патентная литература 3

Публикация заявки на патент Японии, Токукай, № 2008-026865 А (дата публикации: 7 февраля 2008 г.).

Сущность изобретения

Техническая проблема

Однако конструкция схемы 60 возбуждения затвора, описанная в патентной литературе 1, имеет проблему в том, что вероятно появление дефектов, таких как обрывы в линиях. Это происходит потому, что линии 46 схемы возбуждения затвора, которые прикладывают сигналы к каскадам ST, располагаются между схемой 60 возбуждения затвора и краевой стороной 26 подложки, т.е. вне схемы 60 возбуждения затвора, и это удлиняет ответвительные линии 78, которые соединяют линии 46 схемы возбуждения затвора с элементами TFT внутри схемы 60 возбуждения затвора.

Настоящее изобретение было создано с учетом вышеупомянутой проблемы, и задачей настоящего изобретения является обеспечение подложки матрицы, имеющей узкую рамку изображения, в то же время ограничивая появление обрывов в ответвительных линиях.

Решение проблемы

Чтобы решить вышеупомянутую проблему, подложка матрицы настоящего изобретения включает в себя: изолирующую подложку, имеющую область отображения и окружающую ее область; переключающие элементы, размещенные в виде матрицы на изолирующей подложке; пиксельные электроды, размещенные в виде матрицы в области отображения изолирующей подложки и соединенные с переключающими элементами; и схемы возбуждения для возбуждения переключающих элементов, причем схемы возбуждения обеспечиваются в окружающей области и содержат множество столбцовых групп, размещенных в направлении от краевой стороны изолирующей подложки к области отображения, причем каждая из столбцовых групп имеет продольную сторону вдоль краевой стороны изолирующей подложки и содержит множество строчных групп, соответствующих строкам пиксельных электродов, размещенных в виде матрицы, и каждая имеет множество элементов возбуждения; множество магистральных линий, проходящих вдоль краевой стороны изолирующей подложки в окружающей области, причем по меньшей мере одна из магистральных линий обеспечивается между соседними столбцовыми группами; ответвительные линии, обеспечиваемые в окружающей области, каждая из которых соединяет магистральную линию с элементом возбуждения; и соединительные линии, каждая из которых проходит от представляющей интерес ответвительной линии для электрического соединения представляющей интерес ответвительной линии с элементом возбуждения, обеспечиваемым в строчной группе, отличной от строчной группы, где обеспечивается элемент возбуждения, соединенный с представляющей интерес ответвительной линией.

Вышеописанная конструкция уменьшает длины магистральных линий, обеспечиваемых между соседними столбцовыми группами, и длину ответвительной линии, которая соединяет магистральную линию с элементами возбуждения. Это делает возможным сократить случаи обрывов в линиях.

Кроме того, удлинение соединительных линий от ответвительной линии уменьшает количество ответвительных линий, которые соединяют магистральную линию с элементом возбуждения. Это делает возможным предотвратить снижение выхода годных изделий.

Кроме того, уменьшение количества соединений между магистральными линиями и ответвительными линиями уменьшает емкость, которая имеет место в пересечениях, таким образом предотвращая появление задержки сигнала. Кроме того, вышеописанная конструкция позволяет использовать элементы, имеющие малый коэффициент усиления по постоянному току. Это делает возможным уменьшить размер элементов возбуждения, которые составляют каждую из строчных групп. Кроме того, вышеописанная конструкция способствует уменьшению размера схем возбуждения. Это делает возможным обеспечение подложки матрицы, имеющей узкую рамку изображения.

Полезные эффекты изобретения

Чтобы решить вышеупомянутую проблему, подложка матрицы настоящего изобретения включает в себя: изолирующую подложку, имеющую область отображения и ее окружающую область; переключающие элементы, размещенные в виде матрицы на изолирующей подложке; пиксельные электроды, размещенные в виде матрицы в области отображения изолирующей подложки и соединенные с переключающими элементами; и схемы возбуждения для возбуждения переключающих элементов, причем схемы возбуждения обеспечиваются в окружающей области и содержат множество столбцовых групп, размещенных в направлении от краевой стороны изолирующей подложки к области отображения, причем каждая из столбцовых групп имеет продольную сторону по краевой стороне изолирующей подложки и содержит множество строчных групп, соответствующих строкам пиксельных электродов, размещенных в виде матрицы, и каждая имеет множество элементов возбуждения; множество магистральных линий, проходящих по краевой стороне изолирующей подложки в окружающей области, причем по меньшей мере одна из магистральных линий обеспечивается между соседними столбцовыми группами; ответвительные линии, обеспечиваемые в окружающей области и каждая из которых соединяет магистральную линию с элементом возбуждения; и соединительные линии, каждая из которых проходит от представляющей интерес ответвительной линии для электрического соединения представляющей интерес ответвительной линии с элементом возбуждения, обеспечиваемым в строчной группе, отличной от строчной группы, где обеспечивается элемент возбуждения, соединенный с представляющей интерес ответвительной линией.

Этим достигается эффект обеспечения подложки матрицы, имеющей узкую рамку изображения, в то же время ограничивая появление обрывов в ответвительных линиях.

Краткое описание чертежей

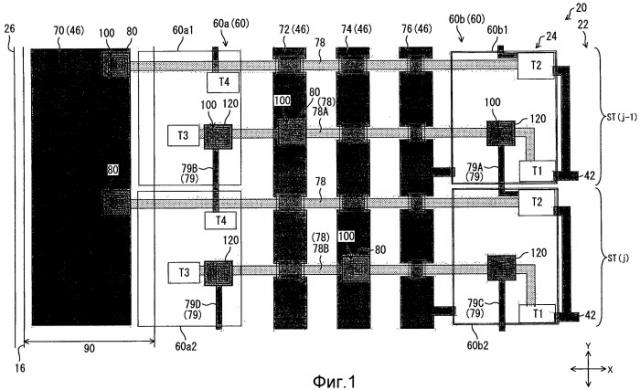

Фиг.1 представляет собой вид сверху, схематически изображающий конструкцию существенной части подложки матрицы TFT согласно первому варианту осуществления настоящего изобретения.

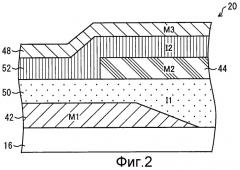

Фиг.2 представляет собой поперечный разрез, схематически изображающий конструкцию существенной части подложки матрицы TFT согласно первому варианту осуществления настоящего изобретения.

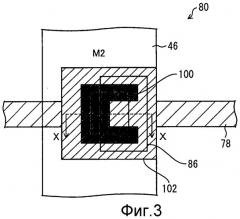

Фиг.3 представляет собой вид сверху, схематически изображающий конструкцию участка переключения согласно первому варианту осуществления настоящего изобретения.

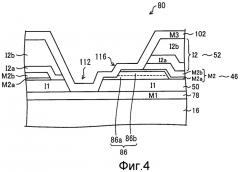

Фиг.4 представляет собой поперечный разрез, схематически изображающий конструкцию участка переключения согласно первому варианту осуществления настоящего изобретения.

Фиг.5 представляет собой вид сверху, схематически изображающий конструкцию существенной части подложки матрицы TFT для сравнения.

Фиг.6 представляет собой вид сверху, схематически изображающий конструкцию существенной части подложки матрицы TFT согласно второму варианту осуществления настоящего изобретения.

Фиг.7 представляет собой вид сверху, схематически изображающий конструкцию существенной части подложки матрицы TFT согласно модифицированному примеру второго варианта осуществления настоящего изобретения.

Фиг.8(а) представляет собой вид сверху, схематически изображающий пример конструкции участка переключения (участка соединения) согласно третьему варианту осуществления настоящего изобретения, фиг.8(b) представляет собой поперечный разрез участка переключения.

Фиг.9(а) представляет собой вид сверху, схематически изображающий пример конструкции участка переключения (участка соединения) согласно третьему варианту осуществления настоящего изобретения, фиг.9(b) представляет собой поперечный разрез участка переключения.

Фиг.10 представляет собой вид сверху, схематически изображающий пример конструкции участка переключения (участка соединения) согласно третьему варианту осуществления настоящего изобретения.

Фиг.11(а) представляет собой вид сверху, схематически изображающий конструкцию участка переключения (участка соединения) согласно модифицированному примеру третьего варианта осуществления настоящего изобретения.

Фиг.12 представляет собой вид сверху, схематически изображающий конструкцию существенной части подложки матрицы TFT.

Фиг.13 представляет собой вид сверху, схематически изображающий конструкцию существенной части подложки матрицы TFT, описанной в патентной литературе 1.

Описание вариантов осуществления

Нижеследующее описывает подробности варианта осуществления настоящего изобретения.

[Первый вариант осуществления]

Нижеследующее описывает один вариант осуществления настоящего изобретения с ссылкой на фиг.1-5.

Подложка 20 матрицы TFT настоящего варианта осуществления выполнена почти аналогично подложке 20 матрицы TFT, описанной раннее со ссылкой на фиг.12.

Фиг.1 представляет собой вид сверху, схематически изображающий конструкцию существенной части подложки 20 матрицы TFT настоящего варианта осуществления.

Как показано на фиг.1, подложка 20 матрицы TFT в качестве подложки матрицы имеет в окружающей области 24 схему 60 (60а, 60b) возбуждения затвора и линии 46 схемы возбуждения затвора, которые подсоединены к FPC (не показана). В схеме 60 возбуждения затвора в качестве схем возбуждения образованы элементы TFT в качестве элементов возбуждения.

В подложке 20 матрицы TFT настоящего варианта осуществления схема 60 возбуждения затвора имеет две отдельные схемы возбуждения вдоль направления Х подложки 20 матрицы TFT. Конкретно, первые схемы 60а возбуждения столбца и вторые схемы 60b возбуждения столбца обеспечиваются в качестве столбцовых групп в направлении Х и составляют схему 60 возбуждения затвора.

Кроме того, каждая из первой схемы 60а возбуждения столбца и второй схемы 60b возбуждения столбца имеет множество схем возбуждения (строчные группы), соответствующих соответствующим строкам, обеспечиваемым в направлении Y подложки 20 матрицы TFT. Ниже это описывается более подробно.

В подложке 20 матрицы TFT настоящего варианта осуществления по меньшей мере некоторые их линий 46 схемы возбуждения затвора обеспечиваются между первой схемой 60а возбуждения столбца и второй схемой 60b возбуждения столбца.

Конкретно, линиями 46 схемы возбуждения затвора, обеспечиваемыми в направлении Y подложки 20 матрицы TFT, являются: линия 70 источника питания с низким потенциалом в качестве магистральной линии, первая линия 72 синхронизации в качестве магистральной линии, вторая линия 74 синхронизации в качестве магистральной линии и линия 76 инициализации в качестве магистральной линии. Вдоль направления от краевой стороны 26 подложки к области 22 отображения обеспечиваются в данном порядке линия 70 источника питания с низким потенциалом, первая линия 72 синхронизации, вторая линия 74 синхронизации и линия 76 инициализации.

В данном случае, область 22 отображения представляет собой область, где элементы TFT использования возбуждения отображения (не показаны) в качестве переключающих элементов и пиксельные электроды (не показаны), соединенные с элементами TFT использования возбуждения отображения, размещены в виде матрицы.

Из всех линий 46 схемы возбуждения затвора первая линия 72 синхронизации, вторая линия 74 синхронизации и линия 76 инициализации обеспечиваются между первой схемой 60а возбуждения столбца и второй схемой 60b возбуждения столбца.

Следует отметить, что линия 70 источника питания с низким потенциалом обеспечивается между краевой стороной 26 подложки и первой схемой 60а возбуждения столбца.

Нижеследующее более конкретно описывает окружающую область 24 подложки 20 матрицы TFT настоящего варианта осуществления.

Каждая из первой схемы 60а возбуждения столбца и второй схемы 60b возбуждения столбца, которые составляют схему 60 возбуждения затвора, имеет множество схем возбуждения, соответствующих соответствующим строкам, обеспечиваемым по направлению Y.

Конкретно, каждая из первой схемы 60а возбуждения столбца и второй схемы 60b возбуждения столбца состоит из множества схем возбуждения, соединенных друг с другом каскадным образом по направлению Y.

Другими словами, схема 60 возбуждения затвора имеет множество каскадов ST, которые последовательно выводят сигналы затвора на линии 42 затвора. Следует отметить, что каскады ST соединены с линиями 42 затвора как одни к одному.

Каждый из каскадов ST включает в себя первую схему 60а возбуждения столбца и вторую схему 60b возбуждения столбца, обе из которых выровнены по направлению Х.

Например, в каскаде ST(j-1) в (j-1)-ой строке первая схема 60а1 возбуждения столбца и вторая схема 60b1 возбуждения столбца выровнены по направлению Х.

Кроме того, в каскаде ST(j) в (j)-ой строке первая схема 60а2 возбуждения столбца и вторая схема 60b2 возбуждения столбца выровнены по направлению Х.

Каждая из первых схем 60а возбуждения столбца обеспечивается между линией 70 источника питания с низким потенциалом и первой линией 72 синхронизации, обе из которых являются магистральными линиями. Каждая из вторых схем 60b возбуждения столбца лежит в граничной зоне между областью 22 отображения и окружающей областью 24 и обеспечиваются между областью 22 отображения и линией 76 инициализации.

Следует отметить что каждая из первых схем 60а возбуждения столбца включает в себя элементы T3 и T4 TFT, и каждая из вторых схем 60b возбуждения столбца включает в себя элементы T1 и T2 TFT.

Кроме того, ответвительные линии 78 обеспечиваются для соединения линий 46 схемы возбуждения затвора с элементами TFT, обеспечиваемыми в схеме 60 возбуждения затвора. Контактные окна 100 обеспечиваются на соответствующих участках 80 соединения между ответвительной линией 78 и линией 70 источника питания с низким потенциалом, между ответвительной линией 78 и первой линией 72 синхронизации и между ответвительной линией 78 и второй линией 74 синхронизации. При помощи контактных окон 100 линии 46 схемы возбуждения затвора и схема 60 возбуждения затвора электрически соединены друг с другом.

Например, в каскаде ST(j-1) элементы T1 и T3 TFT соединены с ответвительной линией 78А, которая электрически соединена с первой линией 72 синхронизации при помощи контактного окна 100, так что элементы T1 и T3 TFT принимают сигнал синхронизации с первой линии 72 синхронизации.

В то же время, в каскаде ST(j) элемент T2 TFT соединен с соединительной линией 79А, проходящей от ответвительной линии 78А, так что элемент T2 TFT принимает сигнал синхронизации с первой линии 72 синхронизации. Контактное окно 100 обеспечивается на участке 120 переключения между ответвительной линией 78А и соединительной линией 79А. Ответвительная линия 78А и соединительная линия 79А электрически соединены друг с другом.

Следует отметить, что в каждом из каскадов ST могут обеспечиваться две или более соединительных линий 79.

Например, в каскаде ST(j) элемент T4 TFT соединен с соединительной линией 79В, проходящей от ответвительной линии 78А, так что элемент T4 TFT принимает сигнал синхронизации с первой линии 72 синхронизации. Контактное окно 100 обеспечивается на участке 120 переключения между ответвительной линией 78А и соединительной линией 79В. Ответвительная линия 78А и соединительная линия 79В электрически соединены друг с другом.

Кроме того, в каскаде ST(J) элементы T1 и T3 TFT соединены с ответвительной линией 78В, которая электрически соединена со второй линией 74 синхронизации при помощи контактного окна 100, так что элементы T1 и T3 TFT принимают сигнал синхронизации со второй линии 74 синхронизации. Следует отметить, что соединительные линии 79С и 79D, проходящие от ответвительной линии 78В, соединены с элементами TFT, обеспечиваемыми в последующем каскаде ST(J+1) (не показан). На участках 120 переключения между ответвительной линией 78В и соединительными линиями 79С и 79D обеспечиваются контактные окна 100. Ответвительная линия 78В электрически соединена с соединительной линией 79С и 79D.

Как описано выше, например, в каскаде ST(j) элементы T2 и T4 TFT электрически соединены с первой линией 72 синхронизации, так что первый сигнал синхронизации подается с первой линии 72 синхронизации на элементы T2 и T4 TFT. В то же время, элементы T1 и T3 TFT электрически соединены со второй линией 74 синхронизации, так что второй сигнал синхронизации подается со второй линии 74 синхронизации на элементы T1 и T3 TFT. С первой линии 72 синхронизации и второй линии 74 синхронизации выводятся сигналы с взаимно противоположными фазами.

Элементы T1 и T2 TFT, обеспечиваемые в каждом из каскадов ST, электрически соединены с линией 42 затвора, и элемент T2 TFT, обеспечиваемый в каждом из каскадов ST, соединен с ответвительной линией 78, которая электрически соединена с линией 70 источника питания с низким потенциалом при помощи контактного окна 100, так что элемент T2 TFT принимает сигнал низкого потенциала с линии 70 источника питания с низким потенциалом. Сигнал низкого потенциала представляет собой сигнал для выключения элемента TFT, и сигнал низкого потенциала подается на электрод затвора элемента TFT.

В настоящем варианте осуществления между первой схемой 60а возбуждения столбца и второй схемой 60b возбуждения столбца обеспечивается первая линия 72 синхронизации, вторая линия 74 синхронизации и линия 76 инициализации, все из которых представляют собой магистральные линии. Т.е. эти линии окружены схемой 60 возбуждения затвора.

С вышеупомянутой конструкцией ответвительные линии 78 для соединения линий 46 схемы возбуждения затвора, проходящих по направлению Y, со схемой 60 возбуждения затвора размещаются, главным образом, между первой схемой 60а возбуждения столбца и второй схемой 60b возбуждения столбца. Это уменьшает длину ответвительных линий 78, таким образом, сокращая случаи обрывов в линиях.

Конструкция в настоящем варианте осуществления такая, что первая линия 72 синхронизации, вторая линия 74 синхронизации и линия 76 инициализации, являющиеся магистральными линиями, обеспечиваются между первой схемой 60а возбуждения столбца и второй схемой 60b возбуждения столбца. Однако настоящее изобретение не ограничивается этой конструкцией. Альтернативно, по меньшей мере одна из линий 46 схемы возбуждения затвора, проходящих по направлению Y, может размещаться соответствующим образом между первой схемой 60а возбуждения столбца и второй схемой 60b возбуждения столбца, обе из которых выровнены по направлению Х.

Линия 70 источника питания с низким потенциалом представляет собой линию источника питания постоянного тока для подачи потенциала запирания элемента TFT. Потенциал запирания связан с током утечки элемента TFT в течение периода, в котором напряжение, приложенное к жидкому кристаллу, сохраняется на каждом пикселе, и также связан с качеством отображения, таким как уменьшение контрастности и неравномерность отображения. Поэтому, линия 70 источника питания с низким потенциалом, в основном, требует подачи стабильного потенциала. Для реализации низкого сопротивления линия 70 источника питания с низким потенциалом может быть образована таким образом, что ее ширина линии больше ширины других магистральных линий.

Если линия 70 источника питания с низким потенциалом размещается внутри схемы 60 возбуждения затвора (на стороне, которая ближе к области 22 отображения), часть схемы 60 возбуждения затвора может приблизиться слишком близко к краевой стороне 26 подложки жидкокристаллической панели 10 отображения (см. фиг.12) или может выйти за кромку уплотнения 90. Это может привести к пробою, вызванному статическим электричеством, в элементе, отклонениям свойств от норм, коррозии и другим дефектам. Поэтому, предпочтительно, чтобы линия 70 источника питания с низким потенциалом размещалась между краевой стороной 26 подложки и схемой 60 возбуждения затвора, т.е. вне схемы 60 возбуждения затвора.

Кроме того, в конструкции согласно настоящему варианту осуществления обеспечивается одна линия 70 источника питания с низким потенциалом. Однако это не подразумевает ограничение настоящего изобретения. Альтернативно, количество линий 70 источника питания с низким потенциалом может быть равно двум или более.

С ссылкой на фиг.5, нижеследующее описывает конструкцию существенной части другой подложки 20 матрицы TFT для сравнения с подложкой 20 матрицы TFT настоящего варианта осуществления.

Фиг.5 представляет собой вид, схематически изображающий конструкцию другой подложки 20 матрицы TFT для сравнения.

Между подложкой 20 матрицы TFT, показанной на фиг.5, и подложкой 20 матрицы TFT, показанной на фиг.1, согласно настоящему варианту осуществления различие заключается в том, обеспечиваются или нет соединительные линии 79. Т.е. подложка 20 матрицы TFT настоящего варианта осуществления обеспечивается с соединительными линиями 79, тогда как подложка 20 матрицы TFT, показанная на фиг.5, не имеет соединительных линий 79. Это описывается ниже.

Как показано на фиг.5, например, в каскаде ST(j-1) элемент T1 TFT (не показан) соединен с ответвительной линией 78А, так что элемент T1 TFT принимает первый сигнал синхронизации с первой линии 72 синхронизации. Элемент T2 TFT (не показан) соединен с ответвительной линией 78В, так что элемент T2 TFT принимает второй сигнал синхронизации со второй линии 74 синхронизации.

Т.е. в каскадах ST две ответвительные линии 78 обеспечиваются для приема сигналов синхронизации с первой линии 72 синхронизации и второй линии 74 синхронизации.

Такая конструкция увеличивает количество пересечений линий 72 и 74 синхронизации (и другой магистральной линии, например линии 76 инициализации) с ответвительными линиями 78, таким образом увеличивая паразитную емкость. Это, более вероятно, вызывает задержку сигнала.

И наоборот, в конструкции настоящего варианта осуществления, например в каскаде ST(j), элементы T1 и T3 TFT соединены с ответвительной линией 78В, которая электрически соединена со второй линией 74 синхронизации при помощи контактного окна 100, так что элементы T1 и T3 TFT принимают второй сигнал синхронизации со второй линии 74 синхронизации. В то же время, элементы T2 и T4 TFT соединены с соединительными линиями 79А и 79В, проходящими от ответвительной линии 78А соответственно, так что элементы T2 и T4 TFT принимают первый сигнал синхронизации с первой линии 72 синхронизации.

Т.е. в каскадах ST, благодаря обеспечению соединительных линий 79, можно принимать сигналы синхронизации с первой линии 72 синхронизации и второй линии 74 синхронизации с обеспечением только одной ответвительной линии 78.

Кроме того, вышеописанная конструкция уменьшает количество ответвительных линий, таким образом предотвращая снижение выхода годных изделий.

Кроме того, в вышеописанной конструкции можно предотвратить появление задержки сигнала. Это происходит потому, что вышеописанная конструкция уменьшает количество пересечений магистральных линий, линий 72 и 74 синхронизации и линии 76 инициализации с ответвительными линиями 78 и приводит к уменьшенной емкости в пересечениях. Это описывается ниже.

Соединительные линии 79 могут быть образованы более узкими, чем ответвительные линии 78 и линии 72 и 74 синхронизации по следующей причине. Т.е. соединительные линии 79 являются более короткими, чем ответвительные линии 78 и линии 72 и 74 синхронизации, и является небольшой общая емкость, вызванная соединениями с соединительными линиями 79, и это уменьшает необходимость предотвращения появления задержки сигнала посредством понижения сопротивления линий.

Поэтому, даже когда новые пересечения образуются между соединительными линиями 79 и ответвительными линиями 78, можно уменьшить вызванную емкость. Это способствует предотвращению задержки сигнала в вышеописанных линиях, таким образом способствуя улучшению свойства выходного сигнала схемы.

Более конкретно, линии 72 и 74 синхронизации в качестве магистральных линий, в основном, образованы более широкими, чем ответвительная линия 78, чтобы предотвратить появление задержки сигнала, вызванной высоким сопротивлением линий. Это, вероятно, увеличивает область перекрытия пересечений линий 72 и 74 синхронизации с ответвительными линиями 78.

И наоборот, подложка 20 матрицы TFT настоящего варианта осуществления уменьшает количество ответвительных линий 78, таким образом уменьшая область перекрытия пересечений линий 72 и 74 синхронизации с ответвительными линиями 78 соответственно.

С другой стороны, подложка 20 матрицы TFT настоящего варианта осуществления может вызывать дополнительные пересечения соединительных линий 79 с ответвительными линиями 78. Однако ширина линии соединительных линий 79 могут быть уже, чем ширина линий 72 и 74 синхронизации.

Поэтому, общая область дополнительных пересечений соединительных линий 79 с ответвительными линиями 78 меньше, чем общая область уменьшенной области перекрытия пересечений линий 72 и 74 синхронизации с ответвительными линиями 78.

Поэтому, в соответствии с подложкой 20 матрицы TFT настоящего варианта осуществления делает возможным уменьшение области пересечений разных линий, таким образом способствуя улучшению свойства выходного сигнала схемы.

Кроме того, подложка 20 матрицы TFT настоящего варианта осуществления позволяет предотвращать появление задержки сигнала, таким образом позволяя уменьшить размер элементов TFT, которые представляют собой составляющие компоненты каскадов ST. Это способствует уменьшению размеров схемы возбуждения затвора, таким образом позволяя обеспечивать подложку матрицы TFT с узкой рамкой изображения.

Кроме того, подложка 20 матрицы TFT настоящего варианта осуществления позволяет уменьшить количество ответвительных линий 78, таким образом расширяя промежуток между ответвительными линиями 78. Поэтому, можно сократить случаи утечек между линиями и, таким образом, улучшить выход годных изделий.

(Положение уплотнения)

Нижеследующее описывает уплотнение 90.

Подложка 20 матрицы TFT и противоподложка (не показана) соединяются друг с другом посредством уплотнения 90, которое составляет жидкокристаллическую панель 10 отображения.

Как показано на фиг.1, подложка 20 матрицы TFT настоящего варианта осуществления такая, что линия 70 источника питания с низким потенциалом и часть первой схемы 60а возбуждения столбца покрываются уплотнением 90, тогда как первая линия 72 синхронизации, вторая линия 74 синхронизации, линия 76 инициализации и вторая схема 60b возбуждения столбца не покрываются уплотнением 90.

Следовательно, контактные окна 100, обеспечиваемые на первой линии 72 синхронизации и второй линии 74 синхронизации, не покрываются уплотнением 90.

Вероятно, что неравномерность толщины ячейки имеет место вблизи места, где обеспечивается уплотнение 90 из-за уступов, создаваемых контактными окнами 100, и неравномерности ширины, плотности и других свойств линий, обеспечиваемых под уплотнением 90. Однако с вышеописанной конструкцией подложка 20 матрицы TFT настоящего варианта осуществления позволяет предотвратить неравномерность толщины ячейки. Это происходит потому, что конструкция согласно настоящему варианту осуществления релизует уменьшение количества контактных окон 100, покрываемых уплотнением 90.

Следует отметить, что эффект предотвращения неравномерности толщины ячейки достигается посред