Способ записи в запоминающее устройство, основанное на mram, при уменьшенной потребляемой мощности

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в уменьшении потребляемой мощности при записи в запоминающее устройство. Способ записи в запоминающее устройство, содержащее множество ячеек магниторезистивной оперативной памяти (MRAM), причем каждая ячейка MRAM, которая должна быть записана в процессе записи с использованием технологии (TAS) термического переключения, включает магнитный туннельный переход (MTJ), имеющий сопротивление, которое может быть изменено во время процесса записи, когда MTJ нагревают до высокой пороговой температуры, и выбранный транзистор, электрически присоединенный к MTJ; множество числовых и разрядных шин, соединяющих ячейки MRAM вдоль строки и столбца соответственно; в котором подают напряжение разрядной шины на одну из разрядных шин и напряжение числовой шины на одну из числовых шин для прохождения нагревающего тока через MTJ выбранной ячейки MRAM; когда MTJ достигает высокой пороговой температуры, изменяют сопротивление MTJ; и охлаждают MTJ для замораживания записанного значения упомянутого сопротивления; упомянутое напряжение числовой шины является напряжением перегрузки числовой шины, которое выше, чем базовое рабочее напряжение питания ячейки MRAM, так что нагревающий ток имеет величину, достаточно большую для нагрева MTJ до заданной высокой пороговой температуры. 7 з.п. ф-лы, 3 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее раскрытие относится к способу записи в запоминающее устройство, содержащее множество ячеек магниторезистивной оперативной памяти (MRAM), допускающих уменьшенную потребляемую мощность.

УРОВЕНЬ ТЕХНИКИ ИЗОБРЕТЕНИЯ

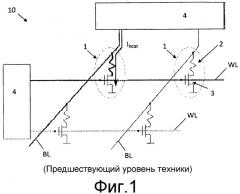

Традиционное запоминающее устройство, основанное на ячейках магниторезистивной оперативной памяти (MRAM), схематически показано на фиг.1. Запоминающее устройство 10 обычно включает массив из числовых шин (WL) и разрядных шин (BL), которые пересекаются с образованием массива. Ячейка 1 MRAM присоединена к каждому пересечению числовых шин WL и разрядных шин BL. Каждая ячейка 1 MRAM содержит магнитный туннельный переход 2, представленный сопротивлением, электрически присоединенный на одном конце к выбранному КМОП-транзистору 3. Магнитный туннельный переход 2 обычно образуют для образования изолирующего слоя-посредника между опорным слоем и запоминающим слоем (эти элементы не показаны на фиг.1). Числовые шины WL соединяют ячейки 1 MRAM вдоль строки посредством затвора их соответствующих транзисторов 3, тогда как разрядные шины BL соединяют ячейки 1 MRAM вдоль столба посредством другого конца их соответствующего магнитного туннельного перехода 2.

Одна из ячеек 1 MRAM, расположенная на соответствующем пересечении одной из разрядной и числовой шин BL, WL, может быть выбрана обеспечением соответствующих разрядных и числовых шин заданным значением напряжения смещения. В примере на Фиг.1 схема 4 выборки дает возможность выбора разрядных и числовых шин BL, WL, на которые подается напряжение смещения.

Во время процесса записи с применением так называемой технологии термического переключения (TAS) выбранной ячейки 1 MRAM данные записывают, применяя единственный нагревающий импульс тока Iheat к магнитному туннельному переходу 2 для нагрева его выше заданной высокой пороговой температуры, тогда как магнитное поле или поляризованный по спину ток применяют для переключения намагниченности запоминающего слоя. Ячейку 1 MRAM затем охлаждают выключением нагревающего импульса тока Iheat, замораживая записанное направление намагниченности запоминающего слоя.

Данные затем считывают измерением сопротивления магнитного туннельного перехода или магнитосопротивления, прикладывая напряжение считывания к магнитному туннельному переходу при температуре окружающей среды или пропуская ток считывания через магнитный туннельный переход и считывая результирующее напряжение.

Одним из основных недостатков такого процесса записи является необходимость повышения температуры запоминающего слоя нагревающим током Iheat выше его пороговой температуры. Действительно, во время процесса записи нагревающий ток регулируется напряжением смещения, подаваемым на числовые и разрядные шины WL, BL. Величина нагревающего тока Iheat, требуемая для нагрева магнитного туннельного перехода 2 выше заданной высокой пороговой температуры, накладывает ограничение на проводимость выбранного транзистора 3 в зависимости от размера магнитного туннельного перехода 2, включенного последовательно с транзистором 3. Например, для достижения пороговой температуры в 150°С в магнитном туннельном переходе 2, имеющем площадь поверхности в 3,14·10-2 мкм2, значение нагревающего тока Iheat должно быть около 200 мкА при использовании небольшого выбранного транзистора (например, 0,13 мкм). При этом нагревающий ток Iheat задается Уравнением 1:

I h e a t = A ∗ P d R A (Уравнение 1)

где А - это площадь поверхности магнитного туннельного перехода 2, Pd - плотность мощности тока в Вт·см-2, и RA - это произведение сопротивления и площади магнитного туннельного перехода (изолирующего слоя) в Ом·см2.

Так как размер ячейки 1 MRAM обычно уменьшают вследствие увеличения степени интеграции и уменьшения масштаба, длина затвора и толщина оксидной пленки выбранного транзистора 3 уменьшаются. Следовательно, используют низкое напряжение матрицы памяти или базовое напряжение питания для включения электропитания ячейки 1 MRAM, чтобы уменьшить потребляемую мощность и улучшить надежность выбранного транзистора 3. Действительно, использование высокого базового напряжения питания производило бы высокое электрическое поле канала с вероятным достижением предела значений напряжения и сопротивления выбранной оксидной пленки транзистора, таким образом, ухудшая надежность выбранного транзистора 3.

Следовательно, трудно сгенерировать значение нагревающего тока, которое является достаточно высоким в большинстве ячеек 1 MRAM, используя низкое базовое напряжение питания. Например, в случае, когда базовое напряжение питания имеет значение, равное 1,2 В, и напряжение в 1,2 В прикладывают к числовой шине WL и разрядной шине BL, результирующий нагревающий ток Iheat, текущий через магнитный туннельный переход 2, имеет значение, равное 130 мкА. Это недостаточно для достижения высокой пороговой температуры в 150°С, и ячейка 1 не может быть записана.

Патентная заявка WO 2008109768 раскрывает систему, схему и способ для регулирования напряжения числовой шины на транзисторе числовой шины в MRAM с передачей спинового момента. Первое напряжение может быть подано на транзистор числовой шины для процесса записи. Второе напряжение, которое меньше, чем первое напряжение, может быть подано на транзистор числовой шины во время процесса считывания. Риск ошибочных записей во время процесса считывания минимизируется.

Патентная заявка EP 2109111 раскрывает ячейку TAS-MRAM, содержащую магнитный туннельный переход, выбранный транзистор и электрическую линию, электрически соединенную с переходом, причем электрическая линия имеет первую функцию для прохождения первой порции тока для нагрева перехода и вторую функцию для прохождения второй порции тока для изменения сопротивления ячейки TAS-MRAM.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Настоящая заявка раскрывает способ записи в запоминающее устройство, содержащее множество ячеек магниторезистивной оперативной памяти (MRAM), которые преодолевают, по меньшей мере, некоторые ограничения предшествующего уровня техники.

Согласно вариантам воплощения способ записи в запоминающее устройство, содержащее множество ячеек MRAM, расположенных в строках и столбцах, причем каждая ячейка MRAM включает магнитный туннельный переход, имеющий сопротивление, которое может быть изменено во время процесса записи при нагреве магнитного туннельного перехода до высокой пороговой температуры, и выбранный транзистор, электрически присоединенный к магнитному туннельному переходу; множество числовых шин, соединяющих ячейки MRAM вдоль строки; и множество разрядных шин, соединяющих ячейки MRAM вдоль столбца; может содержать во время процесса записи подачу напряжения разрядной шины на одну из разрядных шин и напряжения числовой шины на одну из числовых шин для прохождения нагревающего тока через магнитный туннельный переход выбранной ячейки MRAM; отличающийся тем, что упомянутое напряжение числовой шины является напряжением перегрузки числовой шины, которое выше, чем базовое рабочее напряжение питания ячеек MRAM, так что нагревающий ток имеет величину, достаточно большую для нагрева магнитного туннельного перехода до заданной высокой пороговой температуры.

В одном варианте воплощения напряжение перегрузки числовой шины может быть импульсом напряжения с длительностью импульса, которая равна или меньше, чем приблизительно 15 нс.

В другом варианте воплощения напряжение перегрузки числовой шины может генерироваться генератором подкачки заряда или регулируемым внешним напряжением, обеспеченным портом ввода-вывода.

В еще одном варианте воплощения запоминающее устройство может дополнительно содержать схему усилителя считывания, и причем длительность импульса напряжения перегрузки числовой шины может регулироваться схемой усилителя считывания.

В еще одном варианте воплощения выбранный транзистор может быть транзистором большой мощности, имеющим низкое пороговое напряжение.

В еще одном варианте воплощения запоминающее устройство может дополнительно содержать множество исходных шин, соединяющих ячейки MRAM вдоль строки посредством стока их соответствующего выбранного транзистора, и причем способ может дополнительно содержать подачу напряжения перегрузки исходной шины на исходную шину.

В еще одном варианте воплощения напряжение перегрузки исходной шины может иметь значение, по существу, равное пороговому напряжению выбранного транзистора.

В еще одном варианте воплощения способ может дополнительно содержать процесс считывания, включающий измерение сопротивления магнитного туннельного перехода и подачу напряжения перегрузки исходной шины на исходную шину.

Раскрытый способ допускает прохождение нагревающего тока достаточной величины, так что магнитный туннельный переход может быть нагрет до температуры, которая достаточно высока для достижения высокой пороговой температуры, подходящей для изменения его сопротивления без увеличения размера транзисторов. Действительно, раскрытый способ допускает сбор высокой плотности нагревающего тока на стоке транзистора без увеличения размера транзистора. Раскрытый способ допускает использование маленьких транзисторов и, следовательно, запоминающее устройство может иметь высокую плотность записи и может быть записано при небольшой потребляемой мощности.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Предпочтительные варианты воплощения станут более понятными при помощи описания варианта воплощения, данного в качестве примера и проиллюстрированного фигурами, на которых:

Фиг.1 схематически показывает традиционное запоминающее устройство, основанное на ячейках магнитной оперативной памяти (MRAM);

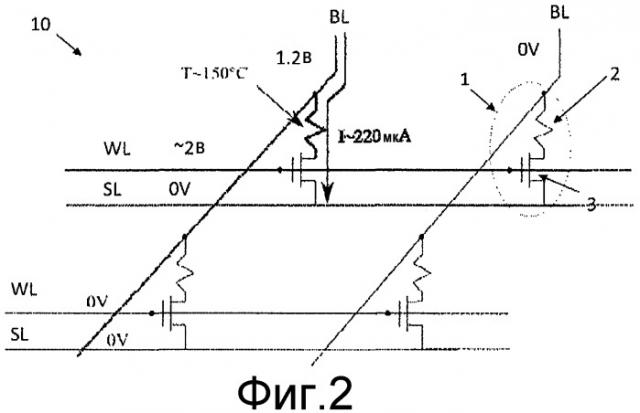

Фиг.2 представляет запоминающее устройство согласно одному варианту воплощения; и

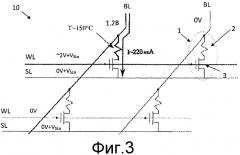

Фиг.3 представляет запоминающее устройство согласно другому варианту воплощения.

ПОДРОБНОЕ ОПИСАНИЕ ВОЗМОЖНЫХ ВАРИАНТОВ ВОПЛОЩЕНИЯ

Фиг.2 схематически представляет запоминающее устройство 10 согласно предпочтительному варианту воплощения. Запоминающее устройство 10 содержит множество ячеек 1 магниторезистивной оперативной памяти (MRAM), расположенных в строках и столбцах. Четыре таких ячейки 1 MRAM показаны на фиг.2. Каждая ячейка 1 MRAM содержит магнитный туннельный переход 2, представленный сопротивлением на фиг.1, электрически присоединенный на одном конце к выбранному КМОП-транзистору 3. Хотя на фиг.2 не показано, магнитный туннельный переход 2 может быть образован опорным слоем, имеющим постоянную намагниченность, запоминающим слоем, имеющим направление намагниченности, которое может быть переключено из первого устойчивого направления во второе устойчивое направление при записи ячейки, и изолирующим слоем между запоминающим слоем и слоем считывания. Ячейка 1 MRAM может быть записана в процессе записи с использованием технологии термического переключения (TAS). Такой процесс записи TAS требует нагрева магнитного туннельного перехода 2 до высокой пороговой температуры для переключения намагниченности запоминающего слоя и затем охлаждения магнитного туннельного перехода 2 до низкой пороговой температуры, ниже высокой пороговой температуры, для замораживания записанного состояния намагниченности запоминающего слоя. Другими словами, магнитный туннельный переход 2 имеет сопротивление, значение которого может быть изменено во время процесса записи TAS при нагреве магнитного туннельного перехода 2 до высокой пороговой температуры.

Запоминающее устройство 10 содержит множество разрядных шин BL и числовых шин WL, образующих угол, предпочтительно прямой, с разрядными шинами BL. Разрядные шины BL соединяют ячейки 1 MRAM вдоль столбца, посредством другого конца их магнитного туннельного перехода 2, а числовые шины WL соединяют ячейки 1 MRAM вдоль строки посредством затвора их выбранного транзистора 3. Запоминающее устройство 10 дополнительно содержит множество исходных шин SL, расположенных, по существу, ортогонально разрядным шинам BL, причем каждая исходная шина SL соединяет ячейки 1 MRAM вдоль строки посредством стока их соответствующего выбранного транзистора 3.

Во время процесса записи данные записывают в одну из ячеек 1 MRAM, подавая напряжение VBL разрядной шины на одну из разрядных шин BL и подавая напряжение VWL числовой шины на одну из числовых шин WL. Записываемая ячейка 1 MRAM или выбранная ячейка 1 MRAM является ячейкой 1, к которой адресуются разрядная и числовая шины BL, WL, на которые подают соответствующие напряжения VBL и VWL разрядной шины и числовой шины. Значение напряжений VBL и VWL обычно соответствуют максимальному напряжению VDD питания или базовому напряжению питания, которое определяется техническими требованиями выбранного транзистора 3, и делают возможным прохождение нагревающего тока Iheat через магнитный туннельный переход 2 выбранной ячейки 1 MRAM. Как обсуждалось выше, в случае, когда выбранный транзистор 3 имеет размер, равный 0,13 мкм, базовое напряжение питания или напряжение VGS затвор-исток выбранного транзистора 3 имеет значение, равное обычно 1,2 В.

Согласно варианту воплощения по фиг.2 во время процесса записи напряжение VWL числовой шины, подаваемое на одну из числовых шин WL, соответствует напряжению VWLo перегрузки числовой шины, которое выше, чем базовое рабочее напряжение питания ячейки 1 MRAM во время периода записи в процессе записи. Значение напряжения VWLo перегрузки числовой шины определяют таким образом, что выбранный транзистор 3 управляет нагревающим током Iheat, имеющим величину, достаточно большую для нагрева магнитного туннельного перехода 2 до высокой пороговой температуры. Более конкретно, значение напряжения VWLo перегрузки числовой шины определяют с учетом размера и плотности ячейки 1 MRAM и норм проектирования литья для нагрузки на оксидный слой магнитного туннельного перехода 2, чтобы избежать влияния на надежность запоминающего устройства 10. Напряжение VWLo перегрузки числовой шины может генерироваться внутренним генератором подкачки заряда (не показан) или регулируемым внешним напряжением VDD, которое выше, чем базовое рабочее напряжение питания, и обеспечивается портом IO ввода-вывода (также не показан). В примере на фиг.2 напряжение VWLo перегрузки числовой шины, имеющее величину, равную 2 В, допускает прохождение нагревающего тока Iheat величиной 220 мкА в случае, когда магнитный туннельный переход 2 ячейки 1 MRAM имеет диаметр, равный 100 нм, и произведение (RA) сопротивления и площади, равное около 30 Ом·см2.

Когда магнитный туннельный переход 2 достигает высокой пороговой температуры, его сопротивление может быть изменено, например, приложением магнитного поля к магнитному туннельному переходу 2 или прохождением поляризованного по спину тока через магнитный туннельный переход 2. В случае, когда магнитный туннельный переход 2 содержит опорный слой и запоминающий слой, сопротивление магнитного туннельного перехода может быть изменено регулировкой направления намагниченности запоминающего слоя. При этом, например, измеряют высокое сопротивление, когда направление намагниченности запоминающего слоя является, по существу, противоположным направлению намагниченности опорного слоя, и измеряют низкое сопротивление, когда соответствующие намагниченности запоминающего и опорного слоев ориентированы, по существу, в одном направлении. Выбранную ячейку 1 MRAM затем охлаждают выключением нагревающего импульса тока Iheat, тем самым замораживая записанное значение сопротивления магнитного туннельного перехода, например, замораживанием записанного направления намагниченности запоминающего слоя.

В варианте воплощения напряжение VWLo перегрузки числовой шины является импульсом напряжения, длительность или ширина которого может регулироваться, чтобы избежать возможной нагрузки на оксидный слой затвора выбранного транзистора 3. Это может быть особенно важным в случае, когда ячейка MRAM записывается вручную пользователем. Регулировка импульса напряжения может быть выполнена, например, с использованием встроенных таймеров (не показаны). При этом напряжение VWLo перегрузки числовой шины имеет длительность импульса напряжения, равную обычно около 15 нс или меньше.

Запоминающее устройство 10 может дополнительно содержать схему усилителя считывания (не показана), используемую для фиксации корректного состояния ячейки 1 MRAM и удержания ввода-вывода IO в таком состоянии до выбора нового адреса, соответствующего выбору другой ячейки 1 MRAM. В таком случае регулировка импульса напряжения VWLo перегрузки числовой шины должна быть синхронизирована со схемой усилителя считывания, или длительность импульса напряжения VWLo перегрузки числовой шины регулируется схемой усилителя считывания.

В другом варианте воплощения, не показанном, выбранный транзистор 3 является транзистором HP большой мощности, имеющим низкое пороговое напряжение Vth. Такой транзистор HP может управлять большим током, чем стандартный КМОП-транзистор для заданного напряжения затвора. Тем не менее, недостатком транзисторов НР является их большой ток Ioff в закрытом состоянии, когда напряжение VGS затвор-исток равно нулю. Большая утечка Ioff разрядной шины BL может ограничить количество ячеек 1 MRAM, которые могут быть присоединены к одному сегменту разрядной шины BL, так как эта утечка Ioff может, вероятно, снизить пределы рабочего режима усилителя считывания до неприемлемого уровня. Обычно более высокие пределы считывания получают для меньшей утечки тока. Использование нескольких маленьких сегментов разрядных шин BL не является предпочтительным, так как это требует использования нескольких транзисторов в сегментах разрядной шины (не показаны), которые обычно являются достаточно большими и дорогими при реализации.

В варианте воплощения утечку тока Ioff в закрытом состоянии уменьшают использованием отрицательной схемы управления затвором. Уменьшение утечки Ioff, таким образом, допускает присоединение большего количества ячеек MRAM на сегмент разрядной шины BL и, следовательно, более плотное запоминающее устройство 10 и более низкую стоимость, так как требуется меньшее количество транзисторов в сегментах.

Фиг.3 представляет еще один другой вариант воплощения запоминающего устройства 10, когда выбранными транзисторами 3 могут быть транзисторы НР. В варианте воплощения по Фиг.3 напряжение VSLo перегрузки исходной шины подают на исходную шину SL для уменьшения утечки тока Ioff. При этом напряжение VSLo перегрузки исходной шины может иметь значение, равное или близкое значению порогового напряжения Vth выбранного транзистора 3.

Во время процесса считывания данные, записанные в выбранную ячейку 1 MRAM, считывают измерением сопротивления магнитного туннельного перехода ячейки 1. Это можно выполнить приложением напряжения считывания (не показано) к магнитному туннельному переходу 2 при температуре окружающей среды или прохождением тока считывания (не показан) через магнитный туннельный переход 2 и считыванием результирующего напряжения.

В варианте воплощения потребляемая мощность запоминающего устройства 10 может быть минимизирована подачей напряжения VSLo перегрузки исходной шины на исходные шины SL во время процесса считывания, такого же, как в процессе записи. Во время процесса записи затвор выбранных транзисторов 3 может быть затем перегружен приложением напряжения VWLo перегрузки числовой шины к числовым шинам WL, так что нагревающий ток Iheat, текущий через магнитный туннельный переход 2, имеет величину, достаточно большую для нагрева магнитного туннельного перехода 2 выше заданной высокой пороговой температуры. Вышеприведенный способ допускает использование маленьких транзисторов (3) и, следовательно, запоминающее устройство может иметь высокую плотность записи и может быть записано при низкой потребляемой мощности.

ССЫЛОЧНЫЕ ПОЗИЦИИ

1 ячейка MRAM

2 магнитный туннельный переход

3 выбранный транзистор

4 схема выборки

10 запоминающее устройство

BL разрядная шина

HP большая мощность

Iheat нагревающий ток

Ioff ток в закрытом состоянии

SL исходная шина

Vc базовое напряжение питания

VDD напряжение стока

VGS напряжение затвор-исток

VSLo напряжение перегрузки исходной шины

VWLo напряжение перегрузки числовой шины

Vth пороговое напряжение

WL числовая шина

1. Способ записи в запоминающее устройство, содержащее множество ячеек магниторезистивной оперативной памяти (MRAM), расположенных в строках и столбцах, причем каждая ячейка MRAM, которая должна быть записана в процессе записи с использованием технологии (TAS) термического переключения, включает магнитный туннельный переход, имеющий сопротивление, которое может быть изменено во время процесса записи, когда магнитный туннельный переход нагревают до высокой пороговой температуры, и выбранный транзистор, электрически присоединенный к магнитному туннельному переходу; множество числовых шин, соединяющих ячейки MRAM вдоль строки; и множество разрядных шин, соединяющих ячейки MRAM вдоль столбца; способ, содержащий в процессе записи этапы, на которых:подают напряжение разрядной шины на одну из разрядных шин и напряжение числовой шины на одну из числовых шин для прохождения нагревающего тока через магнитный туннельный переход выбранной ячейки MRAM;когда магнитный туннельный переход достигает высокой пороговой температуры, изменяют сопротивление магнитного туннельного перехода; иохлаждают магнитный туннельный переход для замораживания записанного значения упомянутого сопротивления;упомянутое напряжение числовой шины является напряжением перегрузки числовой шины, которое выше, чем базовое рабочее напряжение питания ячейки MRAM, так что нагревающий ток имеет величину, достаточно большую для нагрева магнитного туннельного перехода до заданной высокой пороговой температуры.

2. Способ по п.1, в котором напряжение перегрузки числовой шины является импульсом напряжения с длительностью импульса, которая равна или меньше чем приблизительно 15 нс.

3. Способ по п.1, в котором напряжение перегрузки числовой шины генерируется генератором подкачки заряда или регулируемым внешним напряжением, обеспечиваемым портом ввода-вывода.

4. Способ по п.1, в котором запоминающее устройство дополнительно содержит схему усилителя считывания, и отличающийся тем, что длительность импульса напряжения перегрузки числовой шины регулируется схемой усилителя считывания.

5. Способ по п.1, в котором выбранный транзистор является транзистором большой мощности, имеющим низкое пороговое напряжение.

6. Способ по п.1, в котором запоминающее устройство дополнительно содержит множество исходных шин, соединяющих ячейки MRAM вдоль строки посредством стока их соответствующего выбранного транзистора, и при этом способ дополнительно содержит подачу напряжения перегрузки исходной шины на исходную шину.

7. Способ по п.6, в котором напряжение перегрузки исходной шины имеет значение, по существу, равное значению порогового напряжения выбранного транзистора.

8. Способ по п.6, дополнительно содержащий процесс считывания, включающий измерение сопротивления магнитного туннельного перехода и подачу напряжения перегрузки исходной шины на исходную шину.