Интеграция светодиодов на нитриде галлия с приборами на нитриде алюминия-галлия/нитриде галлия на кремниевых подложках для светодиодов переменного тока

Иллюстрации

Показать всеСпособ изготовления эпитаксиальной структуры включает в себя обеспечение подложки и гетеропереходного пакета на первой стороне подложки и формирование пакета светоизлучающего диода на GaN на второй стороне подложки. Гетеропереходный пакет включает в себя нелегированный слой нитрида галлия (GaN) и легированный слой нитрида алюминия-галлия (AlGaN) на нелегированном слое GaN. Пакет светоизлучающего диода на GaN включает в себя слой GaN n-типа поверх подложки, структуру на GaN/нитриде индия-галлия (InGaN) с множественными квантовыми ямами (МКЯ) поверх слоя GaN n-типа, слой AlGaN p-типа поверх структуры на GaN/InGaN n-типа с МКЯ и слой GaN p-типа поверх слоя AlGaN p-типа. Гетеропереходный пакет содержит один или более приборов, связанных с пакетом светоизлучающего диода, причем эти один или более приборов включают в себя один или более из полевого транзистора на гетеропереходе (HTEF) AlGaN/GaN и диода Шоттки на AlGaN/GaN, при этом по меньшей мере один из этих приборов соединен с пакетом светоизлучающего диода на GaN. 2 н. и 13 з.п. ф-лы, 7 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее раскрытие относится к полупроводниковым светоизлучающим диодам и, более конкретно, к светоизлучающим диодам на нитриде галлия с приборами на нитриде алюминия-галлия/нитриде галлия на подложке.

УРОВЕНЬ ТЕХНИКИ

Светоизлучающий диод (СИД) - прибор постоянного тока (DC), который нуждается в подаче постоянного напряжения. Однако, светоизлучатель на основе СИД запускается от сетевого источника переменного напряжения (AC). В связи с этим, светоизлучатель на основе СИД включает в себя возбудитель СИД, который способен управлять значительным переменным напряжением и преобразовывать его в напряжение постоянного тока. Возбудитель СИД, как правило, изготовлен из кремниевых приборов, таких, как смещенно-диффузные МОП (метал-оксид-полупроводник) (LDMOS) или мощные МОП (метал-оксид-полупроводник) полевые транзисторы (MOSFETs).

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

В одном или более вариантах реализации настоящего раскрытия способ изготовления эпитаксиальной структуры включает в себя обеспечение подложки и гетеропереходного пакета на первой стороне подложки и формирование пакета светоизлучающего диода на GaN на второй стороне подложки. Гетеропереходный пакет включает в себя нелегированный слой нитрида галлия (GaN) поверх первой стороны подложки и легированный слой нитрида алюминия-галлия (AlGaN) на нелегированном слое GaN. Пакет светоизлучающего диода на GaN включает в себя слой GaN n-типа поверх второй стороны подложки, структуру на GaN/нитриде индия-галлия (InGaN) с множественными квантовыми ямами (МКЯ) поверх слоя GaN n-типа, слой AlGaN p-типа поверх структуры на GaN/InGaN n-типа с МКЯ и слой GaN p-типа поверх слоя AlGaN p-типа.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

На чертежах:

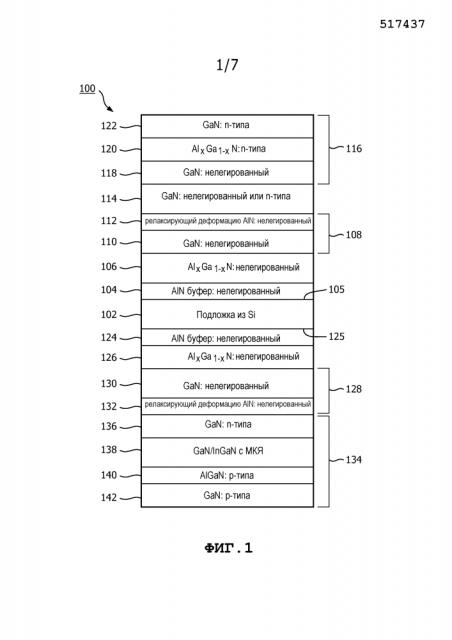

Фиг. 1 - вид поперечного сечения эпитаксиальной структуры для интегрирования светоизлучающих диодов (СИДов) на нитриде галлия (GaN) с приборами на нитриде алюминия-галлия (AlGaN)/GaN на кремниевой подложке;

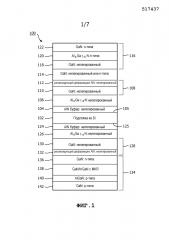

Фиг. 2 - вид поперечного сечения эпитаксиальной структуры для интегрирования СИДов на GaN с приборами на AlGaN/GaN на сапфировой подложке;

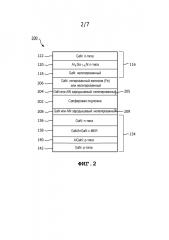

Фиг. 3 - вид поперечного сечения эпитаксиальной структуры для интегрирования СИДов на GaN с приборами на AlGaN/GaN на подложке из карбида кремния (SiC);

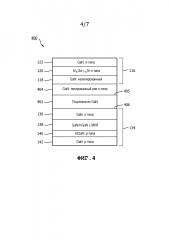

Фиг. 4 - вид поперечного сечения эпитаксиальной структуры для интегрирования СИДов на GaN с приборами на AlGaN/GaN на подложке из GaN;

Фиг. 5 показывает вид поперечного сечения структуры, возникающей из структуры по Фиг. 2, подвергшейся дополнительной обработке для формирования полевого транзистора на гетеропереходе (HFET) AlGaN/GaN и диода Шоттки на AlGaN/GaN;

Фиг. 6 - принципиальная схема мостовой цепи выпрямителя, включенной последовательно с СИД; и

Фиг. 7 показывает вид поперечного сечения структуры, возникающей из структуры по Фиг. 2, подвергшейся дополнительной обработке для формирования мостовой цепи выпрямителя по Фиг. 6, все выполненные в соответствии с вариантами реализации изобретения.

Использование одинаковых позиций на различных фигурах указывает на похожие или одинаковые элементы.

ПОДРОБНОЕ ОПИСАНИЕ

Так как нитрид галлия (GaN) имеет большую запрещенную зону, чем кремний (Si), транзисторы на GaN имеют гораздо более высокое напряжение пробоя, чем транзисторы на Si, следовательно напряжение и плотность тока, которыми могут управлять транзисторы на GaN, гораздо выше. Это позволяет меньшим транзисторам на GaN управлять тем же напряжением, что и более крупные мощные транзисторы на основе Si. С появлением технологии GaN-на-Si транзисторы на GaN, выращенные на 150 мм (6-дюймовых) кремниевых подложках, конкурентоспособны по цене с силовыми приборами на основе кремния и предлагают лучшие рабочие характеристики. При интегрировании светоизлучающих диодов (СИДов) на GaN с транзисторами на GaN на кремниевых подложках такая комбинированная архитектура будет более экономичной и будет иметь более высокую эффективность преобразования напряжения переменного тока в напряжение постоянного тока, чем при традиционном подходе, когда объединяют в пары СИДы на GaN с дискретным электрическим возбудителем на основе Si.

В соответствии с вариантами реализации настоящего раскрытия эпитаксиальная структура производится формированием СИДов на GaN на одной стороне подложки и формированием приборов на нитриде алюминия-галлия (AlGaN)/GaN (или наоборот) на другой стороне подложки. Приборы на AlGaN/GaN могут быть полевыми транзисторами на гетеропереходе (HFETs) и диодами Шоттки, используемыми для преобразования напряжения переменного тока в напряжение постоянного тока или понижающего преобразования напряжения постоянного тока (преобразования высокого напряжение постоянного тока в низкое напряжение постоянного тока). Несколько СИДов и приборов на AlGaN/GaN могут быть соединены последовательно или параллельно в зависимости от схемы преобразования.

Следует обратить внимание, что использование термина "поверх" включает в себя формирование одного слоя или пакета слоев непосредственно на другом слое или пакете слоев. В зависимости от того, располагается структура на верхней или обратной стороне подложки, "поверх" может указывать на один слой или пакет слоев выше или ниже другого слоя или пакета слоев соответственно. Термин «пакет» или «пакет слоев» может быть использован взаимозаменяемо.

Фиг. 1 - вид поперечного сечения эпитаксиальной структуры 100 для интегрирования СИДов на GaN с приборами на AlGaN/GaN на кремниевой (Si) подложке 102 в одном или более вариантах реализации настоящего раскрытия. Поскольку GaN не очень хорошо подходит для прямого эпитаксиального роста на подложках из Si в связи с тем фактом, что Ga и Si образуют эвтектический материал, который разрушает подложку из Si, первым формируется буферный слой 104 нелегированного нитрида алюминия (AlN) поверх первой стороны 105 кремниевой подложки 102 (например, на верхней стороне, как показано), чтобы служить в качестве барьера между GaN и кремнием. Тонкий буферный слой 104 AlN (например, от 100 ангстрем до 2 микрон) используется для уменьшения плотности дефектов. Нелегированный слой 106 AlxGa1-xN может быть сформирован поверх буферного слоя 104 нелегированного AlN для обеспечения дополнительного разделения между Si и GaN.

Поверх слоя 106 AlxGa1-xN может быть сформирован спроектированный с учетом деформации пакет 108. Спроектированный с учетом деформации пакет 108 компенсирует деформацию, возникающую из-за различия коэффициентов теплового расширения у Si и GaN в структуре 100. Спроектированный с учетом деформации пакет 108 включает в себя нелегированный или легированный слой 110 GaN и релаксирующий деформацию слой 112 нелегированного или легированного AlN поверх слоя 110 GaN. Слой 110 GaN пакета 108 формируется непосредственно поверх слоя 106 AlxGa1-xN. Второй спроектированный с учетом деформации пакет 108А (не показан) может быть сформирован поверх первого спроектированного пакета 108.

Нелегированный слой 114 GaN формируется поверх релаксирующего деформацию слоя 112 AlN спроектированного с учетом деформации пакета 108 для отделения спроектированного с учетом деформации пакета 108 от гетеропереходного пакета 116 AlGaN/GaN. Как альтернативный вариант, слой 114 GaN может быть легирован примесью n-типа (донорной), такой, как железо (Fe), для увеличения его сопротивления. Слой 114 GaN является непроводящим слоем, который предотвращает боковой ток утечки из любого HFET, сформированного в гетеропереходном пакете 116 AlGaN/GaN (описано далее) выше слоя 114 GaN, когда HFET выключен. Изолирующие мезы могут быть протравлены вниз до слоя 114 GaN для электрической изоляции приборов, сформированных над слоем 114 GaN.

Гетеропереходный пакет 116 AlGaN/GaN формируется поверх слоя 114 GaN. Гетеропереходный пакет 116 AlGaN/GaN включает в себя нелегированный слой 118 GaN, сильнолегированный слой 120 AlxGa1-xN n-типа на нелегированном слое 118 GaN и пассивирующий слой 122 (например, GaN n-типа) поверх слоя 120 AlxGa1-xN n-типа. Нелегированный слой 118 GaN гетеропереходного пакета 116 находится непосредственно поверх слоя 114 GaN. Гетеропереходный пакет 116 AlGaN/GaN может быть дополнительно обработан для формирования приборов, включая полевые транзисторы на гетеропереходе (HFETs) и диоды Шоттки. Дополнительные элементы схемы могут быть интегрированы с гетеропереходным пакетом 116 AlGaN/GaN или выстроены в слоях поверх него. Например, может быть изготовлен резистор с использованием слоя полупроводника гетеропереходного пакета 116 AlGaN/GaN (например, слоя 118 GaN) формированием двух металлических контактов на определенном расстоянии между ними. Кроме того, может быть изготовлен конденсатор из слоя диэлектрика (диоксида кремния или нитрида кремния), осажденного над гетеропереходным пакетом 116 AlGaN/GaN и находящегося между двумя слоями металла, а также может быть изготовлена катушка индуктивности формированием длинновитковой топологии металлизации сверху слоя полупроводника гетеропереходного пакета 116 AlGaN/GaN (например, слоя 118 GaN).

Буферный слой 124 нелегированного AlN формируется поверх второй стороны 125 кремниевой подложки 102, чтобы служить в качестве слоя барьера между GaN и кремнием. Нелегированный слой 126 AlxGa1-xN формируется поверх буферного слоя 124 нелегированного AlN для обеспечения снятия механических напряжений, возникающих из-за различия коэффициентов теплового расширения и постоянных решетки GaN и Si.

Спроектированный с учетом деформации пакет 128 может быть сформирован поверх нелегированного слоя 126 AlxGa1-xN. Спроектированный с учетом деформации пакет 128 включает в себя нелегированный слой 130 GaN и релаксирующий деформацию слой 132 нелегированного AlN поверх нелегированного слоя 130 GaN. Нелегированный слой 130 GaN пакета 128 находится непосредственно поверх слоя 126 AlxGa1-xN. Структура спроектированного с учетом деформации пакета 128 может быть повторена поверх другого спроектированного пакета 128.

Пакет 134 СИД на GaN формируется поверх релаксирующего деформацию слоя 132 нелегированного AlN спроектированного с учетом деформации пакета 128. Пакет 134 СИД на GaN включает в себя слой 136 GaN n-типа, слои 138 GaN/InyGa1-yN с множественными квантовыми ямами (МКЯ) поверх слоя 136 GaN n-типа, слой 140 AlxGa1-xN p-типа поверх слоев 138 GaN/InyGa1-yN с МКЯ и слой 142 GaN p-типа поверх слоя 140 AlxGa1-xN p-типа. Следует обратить внимание, что AlxGa1-xN и InyGa1-yN в различных слоях могут быть различного состава и могут быть в общем указаны как AlGaN и InGaN соответственно. Слой 136 GaN n-типа пакета 134 располагается непосредственно поверх релаксирующего деформацию слоя 132 нелегированного AlN. Пакет 134 СИД на GaN может быть дополнительно обработан для вскрытия площадок слоя 136 GaN n-типа и слоя 142 GaN p-типа для формирования n- и p-контактов. Дополнительные элементы схемы могут быть интегрированы с пакетом 134 СИД на GaN или выстроены в слоях поверх него.

Следует обратить внимание, что пакет 134 СИД на GaN не формируют поверх непроводящего слоя GaN, как гетеропереходный пакет 116, потому что СИДы являются вертикальными приборами, вследствие чего боковой ток утечки не вызывает серьезную обеспокоенность.

Фиг. 2 - вид поперечного сечения эпитаксиальной структуры 200 для интегрирования СИДов на GaN с приборами на AlGaN/GaN на сапфировой подложке 202 в одном или более вариантах реализации настоящего раскрытия. Первым формируют нелегированный буферный слой 204 поверх первой стороны 205 сапфировой подложки 202 (например, на верхней стороне, как показано) для обеспечения затравки для выращивания других слоев. Нелегированный буферный слой 204 может быть составлен из GaN или AlN. Следующим формируют нелегированный слой 206 GaN на нелегированном буферном слое 204. Как альтернативный вариант, слой 206 GaN может быть легирован примесью n-типа, такой, как Fe, для увеличения его сопротивления. Слой 206 GaN является непроводящим, так что он предотвращает боковой ток утечки из любого прибора HFET над этим слоем, когда HFET выключен. Изолирующие мезы могут быть протравлены вниз до слоя 206 GaN для электрической изоляции приборов, сформированных над этим слоем.

Гетеропереходный пакет 116 AlGaN/GaN (описанный ранее) формируется поверх слоя 206 GaN. Нелегированный слой 118 GaN гетеропереходного пакета 116 находится непосредственно поверх слоя 206 GaN. Гетеропереходный пакет 116 AlGaN/GaN может быть дополнительно обработан для формирования приборов, включая HFETs и диоды Шоттки. Дополнительные элементы схемы могут быть интегрированы с гетеропереходным пакетом 116 AlGaN/GaN или встроены в слои поверх него.

Нелегированный зародышевый слой 208 формируется поверх второй стороны 209 сапфировой подложки 202 (например, на обратной стороне, как показано), чтобы служить затравкой для других слоев. Нелегированный зародышевый слой 208 может быть составлен из GaN или AlN. Пакет 134 СИД на GaN (описанный ранее) формируется поверх нелегированного зародышевого слоя 208. Слой 136 GaN n-типа пакета 134 находится непосредственно поверх нелегированного зародышевого слоя 208. Пакет 134 СИД на GaN может быть дополнительно обработан для вскрытия площадок слоя 136 GaN n-типа и слоя 142 GaN p-типа для формирования n- и p-контактов. Дополнительные элементы схемы могут быть интегрированы с пакетом 134 СИД на GaN или встроены в слои поверх него.

Фиг. 3 - вид поперечного сечения эпитаксиальной структуры 300 для интегрирования СИДов на GaN с приборами на AlGaN/GaN на подложке 302 из карбида кремния (SiC) в одном или более вариантах реализации настоящего раскрытия. Первым формируют нелегированный зародышевый слой 304 поверх первой стороны 305 подложки 302 из SiC (например, на верхней стороне, как показано), чтобы служить затравкой для других слоев. Нелегированный зародышевый слой 304 может быть составлен из AlN или AlxGa1-xN. Следующим формируют нелегированный слой 306 GaN на нелегированном зародышевом слое 304. Как альтернативный вариант, слой 306 GaN может быть легирован примесью n-типа, такой, как Fe, для увеличения его сопротивления. Слой 306 GaN является непроводящим, так что он предотвращает боковой ток утечки из любого прибора HFET над этим слоем, когда HFET выключен. Изолирующие мезы могут быть протравлены вниз до слоя 306 GaN для электрической изоляции приборов, сформированных над этим слоем.

Гетеропереходный пакет 116 AlGaN/GaN (описанный ранее) формируется поверх слоя 306 GaN. Нелегированный слой 118 GaN гетеропереходного пакета 116 находится непосредственно поверх слоя 306 GaN. Гетеропереходный пакет 116 AlGaN/GaN может быть дополнительно обработан для формирования приборов, включая HFETs и диоды Шоттки. Дополнительные элементы схемы могут быть интегрированы с гетеропереходным пакетом 116 AlGaN/GaN или встроены в слои поверх него.

Нелегированный зародышевый слой 308 формируется поверх второй стороны 309 (например, на обратной стороне, как показано) подложки 302 из SiC, чтобы служить затравкой для других слоев. Нелегированный зародышевый слой 308 может быть составлен из AlN или AlxGa1-xN. Пакет 134 СИД на GaN (описанный ранее) формируется поверх нелегированного зародышевого слоя 308. Слой 136 GaN n-типа пакета 134 находится непосредственно поверх нелегированного зародышевого слоя 308. Пакет 134 СИД на GaN может быть дополнительно обработан для вскрытия площадок слоя 136 GaN n-типа и слоя 142 GaN p-типа для формирования n- и p-контактов. Дополнительные элементы схемы могут быть интегрированы с пакетом 134 СИД на GaN или встроены в слои поверх него.

Фиг. 4 - вид поперечного сечения эпитаксиальной структуры 400 для интегрирования СИДов на GaN с приборами на AlGaN/GaN на подложке 402 из GaN в одном или более вариантах реализации настоящего раскрытия. Нелегированный слой 404 GaN может быть сформирован на первой стороне 405 подложки 402 из GaN (например, на верхней стороне, как показано). Как альтернативный вариант, слой 404 GaN может быть легирован примесью n-типа, такой, как Fe, для увеличения его сопротивления. Слой 404 GaN является непроводящим, так что он предотвращает боковой ток утечки из любого прибора HFET над этим слоем, когда HFET выключен. Изолирующие мезы могут быть протравлены вниз до слоя 404 GaN для электрической изоляции приборов, сформированных над этим слоем.

Гетеропереходный пакет 116 AlGaN/GaN (описанный ранее) формируется поверх слоя 404 GaN. Нелегированный слой 118 GaN гетеропереходного пакета 116 находится непосредственно поверх слоя 404 GaN. Гетеропереходный пакет 116 AlGaN/GaN может быть дополнительно обработан для формирования приборов, включая HFETs и диоды Шоттки. Дополнительные элементы схемы могут быть интегрированы с гетеропереходным пакетом 116 AlGaN/GaN или встроены в слои поверх него.

Пакет 134 СИД на GaN (описанный ранее) формируется на второй стороне 406 подложки 402 из GaN (например, на обратной стороне, как показано). Слой 136 GaN n-типа пакета 134 находится непосредственно поверх подложки 402 из GaN. Пакет 134 СИД на GaN может быть дополнительно обработан для вскрытия площадок слоя 136 GaN n-типа и слоя 142 GaN p-типа для формирования n- и p-контактов. Дополнительные элементы схемы могут быть интегрированы с пакетом 134 СИД на GaN или встроены в слои поверх него.

Фиг. 5 показывает вид поперечного сечения структуры 500, возникающей из структуры 200 (Фиг. 2), подвергшейся дополнительной обработке с целью формирования полевых транзисторов 506 на гетеропереходе AlGaN/GaN (HFETs) и диода Шоттки 508 на AlGaN/GaN в одном или более вариантах реализации настоящего раскрытия.

Слой 142 GaN p-типа в пакете 134 СИД на GaN может быть выполнен шероховатым для улучшения световыделения. На слое 142 GaN p-типа формируется p-контакт 501. Один или более участков структуры 200 (Фиг. 2) удаляются вниз до слоя 136 GaN n-типа для формирования n-контакта 502 для СИД в пакете 134 СИД на GaN. В альтернативном варианте участок слоев 116, 206, 204, 202 и 208 может быть удален для формирования n-контакта 502. В еще одном альтернативном варианте слои 206, 204, 202, 208 и все слои пакета 134 СИД на GaN, кроме слоя 142 GaN p-типа, могут быть удалены для формирования p-контакта 501. Расположение всех контактов на одной стороне прибора способствует конфигурации методом перевернутого кристалла.

Изолирующая меза 504 протравливается через гетеропереходный пакет 116 AlGaN/GaN, слой 206 GaN и буферный слой 204 GaN или AlN вниз до сапфировой подложки 202 для электрической изоляции HFET 506 и диода Шоттки 508. HFET 506 и диод Шоттки 508 соединяются мостиками (не показаны) для образования цепи возбуждения СИД в пакете 134 СИД на GaN. Другие элементы схемы, такие, как резисторы, конденсаторы и катушки индуктивности, также могут быть сформированы в гетеропереходном пакете 116 AlGaN/GaN.

HFET 506 включает в себя затвор 512 и исток 514 и сток 516 на противоположных сторонах от затвора 512. Затвор 512 контактирует со слоем 120 AlxGa1-xN n-типа, а исток 514 и сток 516 контактируют с нелегированным слоем 118 GaN. Для затвора 512 в пассивирующем слое 122 GaN n-типа протравливается канал и металл осаждается на слой 120 AlxGa1-xN n-типа. Для истока 514 и стока 516 металл осаждается на пассивирующий слой 122 GaN n-типа и диффундирует вниз в нелегированный слой 118 GaN посредством отжига.

Диод 508 Шоттки включает в себя анодный электрод 518 и катодный электрод 520. Анодный электрод 518 контактирует со слоем 120 AlxGa1-xN n-типа. Для формирования анодного электрода 518 в пассивирующем слое 122 GaN n-типа протравливается канал и металл осаждается на слой 120 AlxGa1-xN. Катодный электрод 520 контактирует с нелегированным слоем 118 GaN. Для формирования катодного электрода 520 металл осаждается на пассивирующий слой 122 GaN n-типа и диффундирует вниз в нелегированный слой 118 GaN посредством отжига.

Фиг. 6 - принципиальная схема мостовой цепи 602 выпрямителя, соединенной с СИД 604. Мостовая цепь 602 выпрямителя преобразует напряжение питания переменного тока в напряжение постоянного тока для того, чтобы питать СИД в одном или более вариантах реализации настоящего раскрытия. Цепь 602 включает в себя диоды D1, D2, D3 и D4, расположенные в мостовой выпрямительной (ромбической) конфигурации, где катод диода D1 соединен с анодом диода D2 и одним выводом источника питания напряжения переменного тока, катод диода D4 соединен с анодом диода D3 и другим выводом источника питания напряжения переменного тока. Аноды диодов D1 и D4 являются отрицательным выводом выпрямленного напряжения питания для СИД 604 и соединены с катодом СИД 604. Катоды диодов D2 и D3 являются положительным выводом выпрямленного напряжения и соединены с анодом СИД 604.

Фиг. 7 показывает вид поперечного сечения структуры 700, возникающей из структуры 200 (Фиг. 2), подвергшейся дополнительной обработке для формирования мостовой цепи 602 выпрямителя (Фиг. 6) в одном или более вариантах реализации настоящего раскрытия. Каждый диод в цепи 602 реализован как диод Шоттки на AlGaN/GaN в гетеропереходном пакете 116. Диод D1 включает в себя анодный электрод 702 и катодный электрод 704. Диод D2 имеет анодный электрод 706 и использует общий с диодом D3 катодный электрод 708, потому что они соединены последовательно через нелегированный слой 118 GaN. Диод D3 имеет анодный электрод 710 и катодный электрод 708. Диод D4 имеет анодный электрод 712 и катодный электрод 714. Каждый анодный электрод контактирует со слоем 120 AlxGa1-xN n-типа, а каждый катодный электрод контактирует с нелегированным слоем 118 GaN. Диоды D1, D2, D3 и D4 формируют способом, описанным для формирования диода 508 в структуре 500 (Фиг. 5).

Части гетеропереходного пакета 116 AlGaN/GaN, слоя 206 GaN и буферного слоя 204 GaN или AlN удаляют для вскрытия площадок сапфировой подложки 202. На одной вскрытой площадке формируют n-контакт 722 протравливанием канала через сапфировую подложку 202 и буферный слой 208 GaN или AlN и, частично, в слой 136 GaN n-типа в пакете 134 СИД на GaN, и осаждением металла в канал. На другой вскрытой площадке формируют p-контакт 726 протравливанием отверстия через сапфировую подложку 202, буферный слой 208 GaN или AlN и пакет 134 СИД на GaN, и осаждением металла в отверстие для образования контакта со слоем 142 GaN p-типа в пакете 134 СИД на GaN. Хотя это не показано, боковые стенки отверстий для n-контакта 722 и p-контакта 726 покрывают изолятором, таким, как оксид. В альтернативном варианте реализации каналы для n-контакта 722 и p-контакта 726 являются каждый достаточно широкими, чтобы позволить столбику металла быть осажденным без контактирования с «боковинами» канала. В другом альтернативном варианте часть слоя 142 GaN p-типа оставляют на дне канала и p-контакт 726 осаждают на нешероховатую поверхность слоя 142 GaN p-типа. В этом последнем варианте реализации нет p-контакта, блокирующего любой свет от СИД, образованного пакетом 134 СИД на GaN.

Диоды D1, диоды D2, D3 и диоды D4 электрически изолированы друг от друга изолирующими мезами 716. Изолирующие мезы 716 протравливают через гетеропереходный пакет 116 AlGaN/GaN, слой 206 GaN и буферный слой 204 GaN или AlN вниз до сапфировой подложки 202 для электрической изоляции диодов D1, пар диодов D2, D3 и D4 друг от друга. Мостики соединяют диоды D1, D2, D3 и D4, как показано на Фиг. 6. В частности, мостики соединяют катодный электрод 708 (катоды D2 и D3) с p-контактом 726, анод СИД в пакете 134 СИД на GaN и анодные электроды 702 и 712 с n-контактом 722, катод СИД в пакете 134 СИД на GaN. Один вывод напряжения переменного тока подключается к катодному электроду 704 диода D1, а также анодному электроду 706 диода D2. Другой вывод напряжения переменного тока подключается к анодному электроду 710 диода D3, а также катодному электроду 714 диода D4.

Варианты реализации настоящего раскрытия предлагают следующие преимущества над традиционными светоизлучателями на основе СИД. Варианты реализации настоящего раскрытия интегрируют СИДы с цепью возбуждения СИД на том же самом шаблоне подложки. Приборы будут интегрированы на уровне пластины металлическими мостиками вместо традиционного способа изготовления дискретных СИДов и цепи возбуждения СИД отдельно и дальнейшего объединения их на уровне кристалла.

Варианты реализации настоящего раскрытия улучшают эффективность преобразования напряжения переменного тока в напряжение постоянного тока. Транзисторные переключатели на GaN имеют меньшее удельное сопротивление, чем приборы на основе Si, обеспечивая меньше омических потерь, вызванных переключением.

Варианты реализации настоящего раскрытия имеют меньший шаг сетки. Транзисторы на GaN могут управлять более высоким рабочим напряжением, чем приборы на основе Si, так что транзисторы переключения могут быть изготовлены меньшими. Необходимые конденсаторы или катушки индуктивности также могут быть изготовлены на уровнях пластины, тем самым уменьшая общую площадь.

Варианты реализации настоящего раскрытия являются более экономичными. Мостик на уровне кристалла, такой, как проводное соединение и пайка, между цепью возбуждения СИД и СИДами больше не требуется, так как они теперь находятся на уровне пластины.

Варианты реализации настоящего раскрытия обеспечивают лучшую температурную стабильность и предотвращают тепловое убегание. Ток СИД, как правило, имеет положительный температурный коэффициент, когда приводится в действие при постоянном напряжении, потому что напряжение включения СИДа становится меньше, когда СИД нагревается. В противоположность этому, полевой транзистор (FET), как правило, имеет отрицательный температурный коэффициент из-за падения подвижности носителей по мере того, как полевой транзистор нагревается. При расположении СИДов и цепи возбуждения СИД на той же самой подложке этот температурный эффект самокомпенсируется, тем самым предотвращая тепловое убегание.

Варианты реализации настоящего раскрытия позволяют упростить производство производящим СИД компаниям. Производящие СИД компании могут приобретать эпитаксиальные пластины со структурами транзисторов на AlGaN/GaN, выращенными на подложках из Si, сапфира или SiC, у других компаний и сосредоточиться на улучшении структур СИД на другой стороне подложки, не беспокоясь об оптимизации структур транзисторов. Более того, толщина структур СИД не будет влиять на структуры транзисторов, выращенные на другой стороне подложки. Другими словами, пластинная обработка СИДов и транзисторов не будет серьезно воздействовать друг на друга.

Различные другие адаптации и сочетания признаков раскрытых вариантов реализации находятся в рамках объема охраны изобретения. Многочисленные варианты реализации охватываются следующей формулой изобретения.

1. Способ изготовления эпитаксиальной структуры, содержащий: обеспечение подложки и гетеропереходного пакета поверх первой стороны подложки, причем гетеропереходный пакет содержит нелегированный слой нитрида галлия (GaN) поверх первой стороны подложки и легированный слой нитрида алюминия-галлия (AlGaN) на нелегированном слое GaN; и

формирование пакета светоизлучающего диода на GaN поверх второй стороны подложки, причем пакет светоизлучающего диода на GaN содержит слой GaN n-типа поверх второй стороны подложки, структуру на GaN/нитриде индия-галлия (InGaN) с множественными квантовыми ямами (МКЯ) поверх слоя GaN n-типа, слой AlGaN p-типа поверх структуры на GaN/InGaN с МКЯ и слой GaN p-типа поверх слоя AlGaN p-типа;

обработку гетеропереходного пакета для формирования одного или более приборов, связанных с упомянутым пакетом светоизлучающего диода, причем этот один или более приборов выбраны из группы, состоящей из полевого транзистора на гетеропереходе (HFET) AlGaN/GaN и диода Шоттки на AlGaN/GaN.

2. Способ по п. 1, при этом:

подложка является кремниевой подложкой;

обеспечение подложки и гетеропереходного пакета поверх первой стороны подложки содержит:

формирование первого спроектированного с учетом деформации пакета поверх первой стороны подложки, причем первый спроектированный с учетом деформации пакет компенсирует деформацию между кремнием и GaN; и

формирование гетеропереходного пакета поверх первого спроектированного с учетом деформации пакета; и

способ дополнительно содержит формирование второго спроектированного с учетом деформации пакета поверх второй стороны подложки, причем пакет светоизлучающего диода на GaN формируют поверх второго спроектированного с учетом деформации пакета,

при этом:

первый спроектированный с учетом деформации пакет содержит:

первый слой GaN поверх первой стороны подложки; и

первый релаксирующий деформацию слой нитрида алюминия (AlN) на первом слое GaN; и

второй спроектированный с учетом деформации пакет содержит:

второй слой GaN поверх второй стороны подложки; и

второй релаксирующий деформацию слой AlN на втором слое GaN.

3. Способ по п. 2, дополнительно содержащий:

формирование первого буферного слоя нелегированного AlN поверх первой стороны подложки; и

формирование первого нелегированного слоя AlGaN поверх первого буферного слоя нелегированного AlN, при этом первый спроектированный с учетом деформации пакет формируют поверх первого нелегированного слоя AlGaN;

формирование второго буферного слоя нелегированного AlN поверх второй стороны подложки; и

формирование второго нелегированного слоя AlGaN поверх второго буферного слоя нелегированного AlN, при этом второй спроектированный с учетом деформации пакет формируют поверх второго нелегированного слоя AlGaN.

4. Способ по п. 3, дополнительно содержащий между первым спроектированным с учетом деформации пакетом и гетеропереходным пакетом формирование непроводящего слоя GaN.

5. Способ по п. 1, при этом подложка содержит сапфировую подложку, а способ дополнительно содержит:

формирование первого зародышевого слоя GaN или AlN поверх первой стороны подложки;

формирование непроводящего слоя GaN поверх зародышевого слоя GaN или AlN, при этом гетеропереходный пакет формируют поверх непроводящего слоя GaN; и

формирование второго зародышевого слоя GaN или AlN поверх второй стороны подложки, при этом пакет светоизлучающего диода на GaN формируют поверх второго буферного слоя GaN или AlN.

6. Способ по п. 1, при этом подложка содержит подложку из карбида кремния (SiC), а способ дополнительно содержит:

формирование первого зародышевого слоя AlN или AlGaN поверх первой стороны подложки;

формирование непроводящего слоя GaN поверх первого буферного слоя AlN или AlGaN, причем гетеропереходный пакет формируют поверх непроводящего слоя GaN; и

формирование второго зародышевого слоя AlN или AlGaN поверх второй стороны подложки, причем пакет светоизлучающего диода на GaN формируют поверх второго зародышевого слоя AlN или AlGaN.

7. Способ по п. 1, при этом подложка содержит подложку из GaN, а способ дополнительно содержит формирование непроводящего слоя GaN поверх первой стороны подложки, причем гетеропереходный пакет формируют поверх непроводящего слоя GaN.

8. Способ по п. 1, при этом упомянутая обработка гетеропереходного пакета содержит:

формирование истока для HFET на AlGaN/GaN, который контактирует с нелегированным слоем GaN;

формирование стока для HFET на AlGaN/GaN, который контактирует с нелегированным слоем GaN;

формирование затвора для HFET на AlGaN/GaN, который контактирует с легированным слоем AlGaN;

формирование анода для диода Шоттки на AlGaN/GaN, который контактирует с легированным слоем AlGaN; и

формирование катода для диода Шоттки на AlGaN/GaN, который контактирует с нелегированным слоем GaN.

9. Эпитаксиальная структура, содержащая:

подложку;

гетеропереходный пакет поверх первой стороны подложки, причем гетеропереходный пакет содержит нелегированный слой GaN поверх первой стороны подложки и легированный слой AlGaN на нелегированном слое GaN; и

пакет светоизлучающего диода на GaN поверх второй стороны подложки, причем пакет светоизлучающего диода на GaN содержит слой GaN n-типа поверх второй стороны подложки, структуру на GaN/InGaN с МКЯ поверх слоя GaN n-типа, слой AlGaN p-типа поверх структуры на GaN/InGaN с МКЯ и слой GaN p-типа поверх слоя AlGaN p-типа,

при этом гетеропереходный пакет содержит один или более приборов, связанных с пакетом светоизлучающего диода, причем эти один или более приборов включают в себя один или более из полевого транзистора на гетеропереходе (HTEF) AlGaN/GaN и диода Шоттки на AlGaN/GaN,

при этом по меньшей мере один из этих приборов соединен с пакетом светоизлучающего диода на GaN.

10. Структура по п. 9, при этом подложка является кремниевой подложкой, а структура дополнительно содержит:

первый спроектированный с учетом деформации пакет поверх первой стороны подложки, причем первый спроектированный с учетом деформации пакет компенсирует деформацию между кремнием и GaN, а гетеропереходный пакет располагается поверх первого спроектированного с учетом деформации пакета; и

второй спроектированный с учетом деформации пакет поверх второй стороны подложки, причем пакет светоизлучающего диода на GaN располагается поверх второго спроектированного с учетом деформации пакета,

при этом:

первый спроектированный с учетом деформации пакет содержит:

первый слой GaN поверх первой стороны подложки; и

первый релаксирующий деформацию слой нитрида алюминия (AlN) на первом слое GaN; и

второй спроектированный с учетом деформации пакет содержит:

второй слой GaN поверх второй стороны подложки; и

второй релаксирующий деформацию слой AlN на втором слое GaN.

11. Структура по п. 9, дополнительно содержащая:

первый буферный слой нелегированного AlN поверх первой стороны подложки; и

первый нелегированный слой AlGaN поверх первого буферного слоя нелегированного AlN, причем первый спроектированный с учетом деформации пакет располагается поверх первого нелегированного слоя AlGaN;

второй буферный слой нелегированного AlN поверх второй стороны подложки;

второй нелегированный слой AlGaN поверх второго буферного слоя нелегированного AlN, причем пакет светоизлучающего диода на GaN располагается поверх второго нелегированного слоя AlGaN; и

непроводящий слой GaN поверх первого спроектированного с учетом деформации пакета, причем гетеропереходный пакет располагается поверх этого непроводящего слоя GaN.

12. Структура по п. 9, при этом подложка содержит сапфировую подложку, а структура дополнительно содержит:

первый зародышевый слой GaN или AlN поверх первой стороны подложки;

непроводящий слой GaN поверх первого зародышевого слоя GaN или AlN, причем гетеропереходный пакет располагается поверх непроводящего слоя GaN; и

второй зародышевый слой GaN или AlN поверх второй стороны подложки, причем пакет светоизлучающего диода на GaN располагается поверх второго зародышевого слоя GaN или AlN.

13. Структура по п. 9, при этом подложка содержит подложку из SiC, а структура дополнительно содержит:

первый зародышевый слой AlN или AlGaN поверх первой стороны подложки;

непроводящий слой GaN поверх первого зародышевого слоя AlN или AlGaN, причем гетеропереходный пакет располагается поверх непроводящего слоя GaN; и

второй зародышевый слой AlN или AlGaN поверх второй стороны подложки, причем пакет светоизлучающего диода на GaN располагается поверх второго зародышевого слоя AlN или AlGaN.

14. Структура по п. 9, при этом подложка содержит подложку из GaN, а структура дополнительно содержит непроводящий слой GaN поверх первой стороны подложки, причем гетеропереходный пакет располагается поверх непроводящего слоя GaN.

15. Структура по п. 9, при этом гетеропереходный пакет содержит:

исток для HFET на AlGaN/GaN, который контактирует с нелегированным слоем GaN;

сток для HFET на AlGaN/GaN, который контактирует с нелегированным слоем GaN;

затвор для HFET на AlGaN/GaN, который контактирует с легированным слоем AlGaN;

анод для диода Шоттки на AlGaN/GaN, который контактирует с легированным слоем AlGaN; и

катод для диода Шоттки на AlGaN/GaN, который контактирует с нелегированным слоем GaN.