Полупроводниковое запоминающее устройство

Иллюстрации

Показать всеИспользование: для создания элемента памяти. Сущность изобретения заключается в том, что полупроводниковое запоминающее устройство включает массив ячеек, включающий в себя множество элементов изменения сопротивления, сформированных над полупроводниковой подложкой, множество первых транзисторов ячеек, сформированных на полупроводниковой подложке и обеспеченных в ассоциации с элементами изменения сопротивления, множество первых затворных электродов, включенных в первые транзисторы ячеек и простирающихся в первом направлении, первые разрядные шины, электрически соединенные с элементами изменения сопротивления соответственно и простирающиеся во втором направлении, перпендикулярном к первому направлению, вторые разрядные шины, электрически соединенные с одним концом пути тока первых транзисторов ячеек соответственно и простирающиеся во втором направлении, и множество первых активных областей, в которых сформированы первые транзисторы ячеек и которые простираются в направлении, пересекающем первое направление под первым углом; и контроллер разрядных шин, включающий в себя множество вторых транзисторов ячеек, сформированных на полупроводниковой подложке, и каждый имеет путь тока с одним концом, электрически соединенным с первыми разрядными шинами или вторыми разрядными шинами, множество вторых затворных электродов, включенных во вторые транзисторы ячеек и простирающихся в первом направлении, и множество вторых активных областей, в которых сформированы вторые транзисторы ячеек и которые простираются в направлении, пересекающем первое направление под вторым углом. Технический результат: обеспечение возможности увеличения рабочей емкости и рабочие пределы, при сдерживании увеличения в размере микросхемы. 2 н. и 18 з.п. ф-лы, 14 ил.

Реферат

ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННЫЕ ЗАЯВКИ

Эта заявка испрашивает приоритет по предварительной заявке США, номер 61/876491, поданной 11 сентября 2013, и приоритет по заявке США, номер 14/201642, поданной 7 марта 2014, все содержимое, которых включается сюда посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ

Варианты осуществления, здесь описанные, относятся, в общем, к полупроводниковому запоминающему устройству.

УРОВЕНЬ ТЕХНИКИ

Известна магнитная оперативная память (MRAM) как одна из памятей типа изменения сопротивления. Способы записи памятей MRAM включают в себя способ записи с использованием магнитного поля и способ записи на основе спинового переноса. Из этих способов, способ на основе спинового переноса является предпочтительным в увеличении плотности интеграции, уменьшении потребления мощности и увеличении емкости, так как этот способ имеет такую характеристику, что ток спинового переноса, который является необходимым для обращения намагниченности, уменьшается по мере того, как размер магнитного тела становится меньше.

Элемент MTJ (с магнитным туннельным переходом) из способа записи на основе спинового переноса имеет многослойную структуру, которая состоит из двух ферромагнитных слоев и немагнитного барьерного слоя (изоляционной тонкой пленки), помещенного между ними, и цифровые данные сохраняются посредством изменения в магнитном сопротивлении вследствие туннельного эффекта спиновой поляризации. Элемент MTJ может принимать состояние низкого сопротивления и состояние высокого сопротивления посредством ориентации намагниченности упомянутых двух ферромагнитных слоев. Когда ориентация намагниченности (направление спина) упомянутых двух ферромагнитных слоев находится в параллельном состоянии (P (параллельном) состоянии), элемент MTJ находится в состоянии низкого сопротивления. Когда ориентация намагниченности упомянутых двух ферромагнитных слоев находится в антипараллельном состоянии (AP (антипараллельном) состоянии), элемент MTJ находится в состоянии высокого сопротивления.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

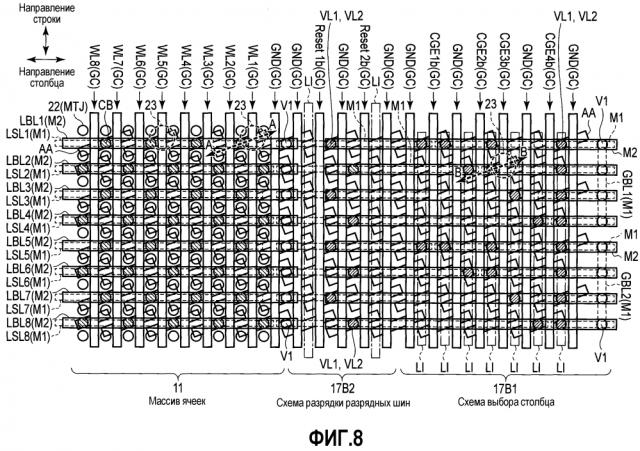

Фиг. 1 является блок-схемой, иллюстрирующей структуру полупроводникового запоминающего устройства согласно первому варианту осуществления.

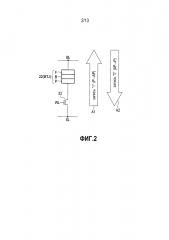

Фиг. 2 является представлением, иллюстрирующим операцию записи ячейки памяти согласно первому варианту осуществления.

Фиг. 3 иллюстрирует пример размещения массива ячеек и его периферийной схемы согласно первому варианту осуществления.

Фиг. 4 является блок-схемой, иллюстрирующей отношение между массивом ячеек и контроллером разрядных шин и шин истока согласно первому варианту осуществления.

Фиг. 5 является принципиальной схемой, иллюстрирующей отношение между массивом ячеек и контроллером разрядных шин и шин истока согласно первому варианту осуществления.

Фиг. 6 является принципиальной схемой, иллюстрирующей отношение между массивом ячеек и контроллером разрядных шин согласно первому варианту осуществления.

Фиг. 7 является принципиальной схемой, иллюстрирующей отношение между массивом ячеек и контроллером шин истока согласно первому варианту осуществления.

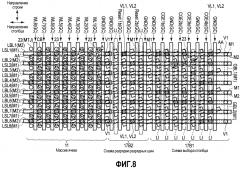

Фиг. 8 является размещением, иллюстрирующим отношение между массивом ячеек и контроллером разрядных шин согласно первому варианту осуществления.

Фиг. 9 является видом в поперечном разрезе, взятом вдоль линии A-A на фиг. 8.

Фиг. 10 является видом в поперечном разрезе, взятом вдоль линии B-B на фиг. 8.

Фиг. 11 является размещением, иллюстрирующим отношение между массивом ячеек и контроллером шин истока согласно первому варианту осуществления.

Фиг. 12 является блок-схемой последовательности операций, которая схематически иллюстрирует базовый способ производства полупроводникового запоминающего устройства согласно первому варианту осуществления.

Фиг. 13 является блок-схемой, которая схематически иллюстрирует структуру подблока.

Фиг. 14A является принципиальной схемой, иллюстрирующей инвертор схемы возбуждения для схемы выбора столбца.

Фиг. 14B является принципиальной схемой, иллюстрирующей схему возбуждения SWD схемы возбуждения для схемы выбора столбца.

Фиг. 14C является принципиальной схемой для схемы возбуждения SWD.

Фиг. 14D является принципиальной схемой для схемы возбуждения сброса BL/SL.

ПОДРОБНОЕ ОПИСАНИЕ

Также в памяти типа изменения сопротивления, которая может реализовывать мелкие ячейки, как описано в разделе "Уровень техники", адекватная емкость ячейки не может выводиться посредством простого увеличения области массива ячеек памяти вследствие увеличения в сопротивлении проводного слоя из-за микротехнологии. Таким образом, является необходимым разделять массив ячеек, тем самым уменьшая влияние увеличения в сопротивлении проводников. Разделять массив ячеек означает увеличивать количество базовых схем вокруг массива ячеек, что просто ведет к увеличению в размере микросхемы. В настоящей заявке область базовой схемы уменьшается посредством использования способа миниатюризации ячеек памяти для базовой схемы вокруг массива ячеек памяти, что тем самым реализует устройство памяти типа изменения сопротивления, которое имеет увеличенную емкость и рабочие пределы, при сдерживании увеличения в размере микросхемы.

В общем, согласно одному варианту осуществления полупроводниковое запоминающее устройство включает в себя массив ячеек, включающий в себя множество элементов изменения сопротивления, сформированных над полупроводниковой подложкой, множество первых транзисторов ячеек, сформированных на полупроводниковой подложке и обеспеченных в ассоциации с элементами изменения сопротивления, множество первых затворных электродов, включенных в первый транзистор ячейки и простирающихся в первом направлении, первую разрядную шину, электрически соединенную с элементом изменения сопротивления и простирающуюся во втором направлении, перпендикулярном к первому направлению, вторую разрядную шину, электрически соединенную с одним концом пути тока первого транзистора ячейки и простирающуюся во втором направлении, и множество первых активных областей, в которых сформированы первые транзисторы ячеек и которые простираются в направлении, пересекающем первое направление под первым углом. Полупроводниковое запоминающее устройство также включает в себя контроллер разрядных шин, включающий в себя множество вторых транзисторов ячеек, сформированных на полупроводниковой подложке, и каждый при этом имеет путь тока с одним концом, электрически соединенным с первой разрядной шиной или второй разрядной шиной, множество вторых затворных электродов, включенных во вторые транзисторы ячеек и простирающихся в первом направлении, и множество вторых активных областей, в которых сформированы вторые транзисторы ячеек и которые простираются в направлении, пересекающем первое направление под вторым углом.

В дальнейшем, сконструированные варианты осуществления будут описываться со ссылкой на сопровождающие чертежи. В описании ниже, структурные элементы, имеющие, по существу, одинаковые функции и структуры, обозначаются посредством сходных ссылочных позиций, и перекрывающее описание дается только там, где необходимо. "Буквы" или "дефис и число" после числа, которое составляет ссылочную позицию, и "число" или "дефис и число" после символа, который составляет ссылочную позицию, используются, чтобы различать элементы, которые указываются посредством ссылочных позиций, включающих в себя одно и то же число, и имеют одну и ту же структуру. Когда не является необходимым различать элементы, которые указываются посредством ссылочных позиций, включающих в себя одно и то же число, эти элементы указываются посредством ссылочной позиции, включающей в себя только число или символ. Например, когда не является необходимым различать элементы с помощью ссылочных позиций 1a и 1b, эти элементы понятным образом указываются посредством ссылочной позиции 1. В дополнение, например, когда не является необходимым различать элементы с помощью ссылочных позиций WL1 и WL2, эти элементы понятным образом указываются посредством ссылочной позиции WL.

Следует отметить, что чертежи являются схематическими чертежами, и отношение между толщиной и плоским размером, отношение в толщине между слоями и т.д. отличаются от реальных отношений. Таким образом, должны учитываться конкретные толщины и размеры при рассмотрении описаний ниже. Само собой, чертежи включают в себя части с взаимно разными отношениями или соотношениями размеров. Кроме того, варианты осуществления, которые будут описываться ниже, иллюстрируют, в качестве примера, устройства или способы для осуществления технических концепций вариантов осуществления, и технические концепции вариантов осуществления специально не ограничивают материал, форму, структуру, компоновку и т.д. структурных компонентов, теми, что описаны ниже. Различные изменения могут делаться в технических концепциях вариантов осуществления в пределах объема формулы изобретения.

(ПЕРВЫЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ)

<СТРУКТУРА ПОЛУПРОВОДНИКОВОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА СОГЛАСНО ПЕРВОМУ ВАРИАНТУ ОСУЩЕСТВЛЕНИЯ>

Прежде всего, как показано на фиг. 1, схематически описывается базовая структура полупроводникового запоминающего устройства согласно первому варианту осуществления. Фиг. 1 является блок-схемой, иллюстрирующей структуру полупроводникового запоминающего устройства согласно первому варианту осуществления.

Полупроводниковое запоминающее устройство 1 первого варианта осуществления включает в себя массив 11 ячеек памяти (также упоминаемый просто как "массив ячеек"), контроллер 12, схему 13 DQ, схему 14 команды адреса, декодер 15 строк, подблок 16, контроллер 17 разрядных шин и шин истока, усилитель 18 считывания/ схему возбуждения записи, схему 20 возбуждения числовых шин и внутренний генератор 21 напряжения. Подблок 16 генерирует сигнал управления схемы 20 возбуждения числовых шин и сигнал управления контроллера 14 разрядных шин и шин истока в ассоциации с каждым массивом 11 ячеек памяти.

Массив 11 ячеек является MRAM, в которой множество ячеек MC памяти расположены двумерно в матрице. Каждая ячейка MC памяти включает в себя элемент 22 MTJ (не показан) и транзистор 23 ячейки (не показан). Элемент 22 MTJ является элементом с магнитным туннельным переходом, который сохраняет данные посредством изменения в состоянии сопротивления, и может перезаписывать данные посредством электрического тока. Транзистор 23 ячейки обеспечен в ассоциации с элементом 22 MTJ и сконфигурирован с возможностью делаться проводящим, когда ток обусловлен течь в ассоциированном элементе 22 MTJ.

Множество числовых шин WL расположены в направлении строки и множество разрядных шин BL расположены в направлении столбца, так что числовые шины WL и разрядные шины BL пересекают друг друга. Две соседние разрядные шины BL составляют пару, и ячейка MC памяти обеспечивается в ассоциации с пересечением между числовой шиной WL и парой разрядных шин (в этом варианте осуществления, ради удобства, упоминаемых как разрядная шина BL и шина SL истока). Элемент 22 MTJ и транзистор 23 ячейки каждой ячейки MC памяти соединены последовательно между парой разрядных шин (например, между BL и SL). В дополнение, затвор транзистора 23 ячейки соединен с числовой шиной WL.

Различные внешние сигналы управления, например сигнал CS выбора микросхемы, сигнал CK тактового импульса и сигнал CKE активирования генератора тактовых импульсов, вводятся в контроллер 12. Контроллер 12 управляет схемой 14 команды адреса и различает адрес и команду.

Сигнал CAi адреса команды вводится в схему 14 команды адреса. Схема 14 команды адреса передает сигнал CAi адреса команды в декодер 15 строк и подблок 16.

Декодеры 15 строк расположены на обеих сторонах в направлении числовой шины массива 11 ячеек памяти и декодируют адрес сигнала CAi адреса команды, который был обеспечен из схемы 14 команды адреса.

Подблок 16 распознает, на основе внешнего сигнала управления, команду или адрес посредством сигнала CAi адреса команды и управляет схемой 20 возбуждения числовых шин и контроллером 17 разрядных шин и шин истока.

Контроллер 17 разрядных шин и шин истока расположены на обеих сторонах в направлении разрядной шины массива 11 ячеек памяти, и управляют разрядной шиной BL и шиной SL истока на основе сигнала управления от подблока 16.

Усилитель 18 считывания/схема возбуждения записи размещен(а) в направлении разрядной шины массива 11 ячеек памяти. Усилитель считывания соединен с разрядной шиной BL и считывает данные, сохраненные в ячейке памяти, посредством распознавания тока, текущего в ячейке MC памяти, которая соединена с выбранной числовой шиной WL. Схема возбуждения записи соединена с разрядной шиной BL и записывает данные посредством предписания току течь в ячейке MC памяти, которая соединена с выбранной числовой шиной WL.

Передача/прием данных между усилителем 18 считывания/схемой возбуждения записи и внешним терминалом DQ ввода/вывода исполняется посредством шины 19 данных и схемы 13 DQ.

Схемы 20 возбуждения числовых шин располагаются на обеих сторонах в направлении числовой шины массива 11 ячеек памяти и соединены с числовыми шинами, и сконфигурированы с возможностью прикладывать напряжение к выбранной числовой шине WL во время считывания данных или записи данных. Более конкретно, схема 20 возбуждения числовых шин сконфигурирована с возможностью прикладывать напряжение к выбранной числовой шине WL в соответствии с адресом строки, декодированным посредством декодера 15 строк.

Внутренний генератор 21 напряжения обеспечивается, чтобы генерировать внутреннее напряжение (например, напряжение, увеличенное посредством напряжения источника питания), которое необходимо для операций в полупроводниковом запоминающем устройстве 1. Этот внутренний генератор 21 напряжения тоже управляется посредством контроллера 12 и исполняет операцию увеличения и генерирует необходимое напряжение.

<ОПЕРАЦИЯ ЗАПИСИ ЯЧЕЙКИ MC ПАМЯТИ>

Далее, как показано на фиг. 2, схематически описывается операция записи ячейки MC памяти согласно первому варианту осуществления. Фиг. 2 является представлением, иллюстрирующим операцию записи ячейки MC памяти согласно первому варианту осуществления.

Как проиллюстрировано на фиг. 2, один конец элемента 22 MTJ ячейки MC памяти согласно первому варианту осуществления соединен с разрядной шиной BL, и другой конец элемента 22 MTJ соединен с одним концом пути тока транзистора 23 ячейки. Другой конец пути тока транзистора 23 ячейки соединен с шиной SL истока. Элемент 22 MTJ, который использует TMR (туннельный магниторезистивный) эффект, имеет многослойную структуру, которая составлена из двух ферромагнитных слоев F и P, и немагнитный (туннельная изоляционная пленка) B помещен между ними, и сохраняет цифровые данные посредством изменения в магнитном сопротивлении посредством туннельного эффекта спиновой поляризации. Элемент 22 MTJ может принимать состояние низкого сопротивления и состояние высокого сопротивления посредством ориентации намагниченности упомянутых двух ферромагнитных слоев F, P. Например, если состояние низкого сопротивления определяется как данные "0" и состояние высокого сопротивления определяется как данные "1", 1 битные данные могут сохраняться в элементе 22 MTJ. Не приходится и говорить, что состояние низкого сопротивления может определяться как данные "1" и состояние высокого сопротивления может определяться как данные "0".

Например, элемент 22 MTJ сконфигурирован так, что фиксированный слой (закрепленный слой) P, туннельный барьерный слой B и записывающий слой (свободный слой) F уложены последовательно. Закрепленный слой P и свободный слой F сформированы из ферромагнитного материала, и туннельный барьерный слой B сформирован из изоляционной пленки (например, Al2O3, MgO). Закрепленный слой P является слоем с фиксированным направлением ориентации намагниченности. Свободный слой F имеет изменяемое направление ориентации намагниченности, и данные сохраняются посредством использования направления намагниченности.

Если электрический ток обусловлен течь в направлении стрелки A1 во время записи, направление намагниченности свободного слоя F устанавливается в антипараллельном состоянии (AP состоянии) по отношению к направлению намагниченности закрепленного слоя P, и устанавливается состояние высокого сопротивления (данные "1"). Если электрический ток обусловлен течь в направлении стрелки A2 во время записи, направления намагниченности закрепленного слоя P и свободного слоя F устанавливаются в параллельном состоянии (P состоянии), и устанавливается состояние низкого сопротивления (данные "0"). Таким образом, в элементе MTJ могут записываться разные данные в соответствии с направлением течения электрического тока.

<СТРУКТУРА МАССИВОВ ЯЧЕЕК СОГЛАСНО ПЕРВОМУ ВАРИАНТУ ОСУЩЕСТВЛЕНИЯ И ИХ ПЕРИФЕРИЙНЫЕ СХЕМЫ>

Далее, как показано на фиг. 3 по фиг. 11, схематически описывается размещение массивов ячеек и их периферийных схем согласно первому варианту осуществления. Фиг. 3 иллюстрирует пример размещения массивов ячеек и их периферийных схем согласно первому варианту осуществления. Фиг. 4 является блок-схемой, иллюстрирующей отношение между массивом ячеек и контроллером разрядных шин и шин истока согласно первому варианту осуществления. Фиг. 5 является принципиальной схемой, иллюстрирующей отношение между массивом ячеек и контроллером разрядных шин и шин истока согласно первому варианту осуществления. Фиг. 6 является принципиальной схемой, иллюстрирующей отношение между массивом ячеек и контроллером разрядных шин согласно первому варианту осуществления. Фиг. 7 является принципиальной схемой, иллюстрирующей отношение между массивом ячеек и контроллером шин истока согласно первому варианту осуществления. Фиг. 8 является размещением, иллюстрирующим отношение между массивом ячеек и контроллером разрядных шин согласно первому варианту осуществления. Фиг. 9 является видом в поперечном разрезе, взятом вдоль линии A-A на фиг. 8. Фиг. 10 является видом в поперечном разрезе, взятом вдоль линии B-B на фиг. 8. Фиг. 11 является размещением, иллюстрирующим отношение между массивом ячеек и контроллером шин истока согласно первому варианту осуществления.

Как проиллюстрировано на фиг. 3, контроллеры 17 разрядных шин и шин истока обеспечены вдоль обоих концов вдоль направления X каждого массива 11 ячеек. Два контроллера 17 разрядных шин и шин истока, которые размещены рядом с каждым массивом 11 ячеек, используются для управления массивом 11 ячеек.

В дополнение, как показано на фиг. 3, схемы 20 возбуждения числовых шин обеспечены вдоль обоих концов вдоль направления Y каждого массива 11 ячеек. Две схемы 20 возбуждения числовых шин, которые размещены рядом с каждым массивом 11 ячеек, используются для управления массивом 11 ячеек.

Подблок 16 обеспечен на пересечении между столбцом, в котором расположены схемы 20 возбуждения числовых шин, и строкой, в которой расположены контроллеры 17 разрядных шин и шин истока.

Как проиллюстрировано на фиг. 4, контроллер 17 разрядных шин и шин истока включает в себя схему CG_BL выбора разрядной шины и схему CG_SL выбора шины истока.

Схема CG_BL выбора разрядной шины включает в себя переключающие транзисторы 24-1 по 24-n (n является целым числом, равным 1 или больше) и избирательно соединяет глобальную разрядную шину GBL усилителя 18 считывания/схемы возбуждения записи с номером n из локальных разрядных шин LBL1 по LBLn.

В дополнение, схема CG_SL выбора шины истока включает в себя переключающие транзисторы 26-1 по 26-n и избирательно соединяет глобальную шину GSL истока усилителя 18 считывания/схемы возбуждения записи с номером n из локальных шин LSL1 по LSLn истока.

В массиве 11 ячеек числовая шина, с которой соединяется вывод схемы 20 возбуждения числовых шин и которая соответствует выбранной ячейке, активируется.

Схема CG_BL выбора разрядной шины принимает выходной сигнал от подблока 16. В схеме CG_BL выбора разрядной шины, на основе этого выходного сигнала, включается переключающий транзистор 24-i, соответствующий выбранной локальной разрядной шине BLi (i является целым числом, равным 1 или больше), из числа номера n из переключающих транзисторов 24-1 по 24-n. Затем, выбранная локальная разрядная шина LBLi соединяется с глобальной разрядной шиной GBL, и соединяется с усилителем 18 считывания/ схемой возбуждения записи.

Аналогично, схема CG_SL выбора шины истока принимает выходной сигнал от подблока 16. В схеме CG_SL выбора шины истока, на основе этого выходного сигнала, включается переключающий транзистор 26-i, соответствующий выбранной локальной шине LSLi истока из числа номера n из переключающих транзисторов 26-1 по 26-n. Затем, выбранная локальная шина LSLi истока соединяется с глобальной шиной GSL истока и соединяется с усилителем 18 считывания/схемой возбуждения записи.

Как проиллюстрировано на фиг. 5, схема CG_BL выбора разрядной шины включает в себя схему 17B1 выбора столбца и схему 17B2 разрядки разрядных шин.

Схема 17B1 выбора столбца включает в себя транзисторы 24-1 по 24-n ячеек, функционирующие как переключающие транзисторы 24-1 по 24-n. Выходной сигнал от подблока 16 вводится в затворный электрод каждого из транзисторов 24-1 по 24-n ячеек, и глобальная разрядная шина GBL соединена с одним концом пути тока каждого из транзисторов 24-1 по 24-n ячеек. В дополнение, пути тока соответствующих транзисторов 24-1 по 24-n ячеек соединяются с ассоциированными локальными разрядными шинами LBL1 по LBLn.

Схема 17B2 разрядки разрядных шин включает в себя транзисторы 25 сброса между транзисторами 24-1 по 24-n ячеек и локальными разрядными шинами LBLn по LBLn. На основе сигнала сброса от подблока 16 схема 17B2 разрядки разрядных шин соединяет локальную разрядную шину с потенциалом земли. Чтобы быть более конкретными, выходной сигнал от подблока 16 вводится в затвор транзистора 25 сброса. В дополнение, любая из локальных разрядных шин LBL1 по LBLn соединена с одним концом пути тока транзистора 25 сброса, и другой конец пути тока соединен с потенциалом земли.

Кроме того, как проиллюстрировано на фиг. 5, схема CG_SL выбора шины истока включает в себя схему 17S1 выбора столбца и схему 17S2 разрядки шин истока.

Схема 17S1 выбора столбца включает в себя транзисторы 26-1 по 26-n ячеек, функционирующие как переключающие транзисторы 26-1 по 26-n. Выходной сигнал от подблока 16 вводится в затворный электрод каждого из транзисторов 26-1 по 26-n ячеек, и глобальная шина GSL истока соединена с одним концом пути тока каждого из транзисторов 26-1 по 26-n ячеек. В дополнение, пути тока соответствующих транзисторов 26-1 по 26-n ячеек соединены с ассоциированными локальными шинами LSL1 по LSLn истока.

Схема 17S2 разрядки шин истока включает в себя транзисторы 27 сброса между транзисторами 26-1 по 26-n ячеек и локальными шинами LSL1 по LSLn истока. На основе сигнала сброса от подблока 16, схема 17S2 разрядки шин истока соединяет локальную шину истока с потенциалом земли. Чтобы быть более конкретными, выходной сигнал от подблока 16 вводится в затвор транзистора 27 сброса. В дополнение, любая из локальных шин LSL1 по LSLn истока соединена с одним концом пути тока транзистора 27 сброса, и другой конец пути тока соединен с потенциалом земли.

Далее, как показано на фиг. 6, структура схемы для схемы 17B1 выбора столбца описывается более подробно. На фиг. 6 для цели простого описания показаны только четыре локальные разрядные шины LBL и четыре локальные шины LSL истока, и показаны только восемь ячеек MC памяти в массиве 11 ячеек.

Как проиллюстрировано на фиг. 6, ячейка MC1 памяти включает в себя элемент 22-1 MTJ, который имеет один конец, соединенный с локальной разрядной шиной LBL1, и транзистор 23-1, который имеет путь тока с одним концом, соединенным с локальной шиной LSL1 истока, и другим концом, соединенным с другим концом элемента 22-1 MTJ, и имеет затворный электрод, принимающий ввод из числовой шины WL1. В дополнение, ячейка MC2 памяти включает в себя элемент 22-2 MTJ, который имеет один конец, соединенный с локальной разрядной шиной LBL1, и транзистор 23-2, который имеет путь тока с одним концом, соединенным с локальной шиной LSL1 истока, и другим концом, соединенным с другим концом элемента 22-2 MTJ, и имеет затворный электрод, принимающий ввод из числовой шины WL2. Ячейка MC3 памяти включает в себя элемент 22-3 MTJ, который имеет один конец, соединенный с локальной разрядной шиной LBL2, и транзистор 23-3, который имеет путь тока с одним концом, соединенным с локальной шиной LSL2 истока, и другим концом, соединенным с другим концом элемента 22-3 MTJ, и имеет затворный электрод, принимающий ввод из числовой шины WL1. Ячейка MC4 памяти включает в себя элемент 22-4 MTJ, который имеет один конец, соединенный с локальной разрядной шиной LBL2, и транзистор 23-4, который имеет путь тока с одним концом, соединенным с локальной шиной LSL2 истока, и другим концом, соединенным с другим концом элемента 22-4 MTJ, и имеет затворный электрод, принимающий ввод из числовой шины WL2. Аналогично, ячейки MC5 и MC6 памяти соединены с локальной разрядной шиной LBL3 и локальной шиной LSL3 истока, и ячейки MC7 и MC8 памяти соединены с локальной разрядной шиной LBL4 и локальной шиной LSL4 истока. В дополнение, ячейки MC5 и MC7 памяти соединены с числовой шиной WL1, и ячейки MC6 и MC8 памяти соединены с числовой шиной WL2. Локальные разрядные шины LBL1 по LBL4 соединены с проводными линиями M1 через переходные контакты V1 соответственно. В этой связи, как показано на фиг. 6, локальная шина LSL истока является проводной линией M1. Однако посредством этапа изготовления, называемого "M1cut", который будет описываться ниже, локальная шина LSL истока (см. части в форме эллипса, указанные посредством прерывистых линий на фигуре) физически разрезается, чтобы никакое короткое замыкание не могло происходить между локальной разрядной шиной LBL и локальной шиной LSL истока в силу того, что локальная разрядная шина LBL соединена с M1 через переходной контакт V1.

В дополнение, как проиллюстрировано на фиг. 6, схема 17B2 разрядки разрядных шин включает в себя, например, транзисторы 25-1 по 25-4 сброса. Транзистор 25-1 сброса имеет путь тока с одним концом, соединенным с M1a, и другим концом, соединенным с потенциалом земли, и имеет затворный электрод, в который вводится сигнал RESET1b сброса. Транзистор 25-2 сброса имеет путь тока с одним концом, соединенным с M1b, и другим концом, соединенным с потенциалом земли, и имеет затворный электрод, в который вводится сигнал RESET2b сброса. Транзистор 25-3 сброса имеет путь тока с одним концом, соединенным с M1c, и другим концом, соединенным с потенциалом земли, и имеет затворный электрод, в который вводится сигнал RESET1b сброса. Транзистор 25-4 сброса имеет путь тока с одним концом, соединенным с M1d, и другим концом, соединенным с потенциалом земли, и имеет затворный электрод, в который вводится сигнал RESET2b сброса.

Кроме того, как проиллюстрировано на фиг. 6, схема 17B1 выбора столбца включает в себя переключающие транзисторы 24-1 по 24-4. Переключающий транзистор 24-1 включает в себя переключающие транзисторы 24-1a, 24-1b, 24-1c и 24-1d, каждый из которых имеет путь тока с одним концом, соединенным с проводной линией M1a через проводную линию LI-1, и другим концом, соединенным с глобальной разрядной шиной GBL1 (M1) через проводную линию LI-2, и имеет затворный электрод, в который вводится сигнал CGE1b управления.

В дополнение, переключающий транзистор 24-2 включает в себя переключающие транзисторы 24-2a, 24-2b, 24-2c и 24-2d, каждый из которых имеет путь тока с одним концом, соединенным с проводной линией M1b через проводную линию LI-3, и другим концом, соединенным с глобальной разрядной шиной GBL1 (M1) через проводную линию LI-4, и имеет затворный электрод, в который вводится сигнал CGE2b управления.

Переключающий транзистор 24-3 включает в себя переключающие транзисторы 24-3a, 24-3b, 24-3c и 24-3d, каждый из которых имеет путь тока с одним концом, соединенным с проводной линией M1c через проводную линию LI-5, и другим концом, соединенным с глобальной разрядной шиной GBL1 (M1) через проводную линию LI-6, и имеет затворный электрод, в который вводится сигнал CGE3b управления.

Переключающий транзистор 24-4 включает в себя переключающие транзисторы 24-4a, 24-4b, 24-4c и 24-4d, каждый из которых имеет путь тока с одним концом, соединенным с проводной линией M1d через проводную линию LI-7, и другим концом, соединенным с глобальной разрядной шиной GBL1 (M1) через проводную линию LI-8, и имеет затворный электрод, в который вводится сигнал CGE4b управления.

Между тем, проводная линия M1a и глобальная разрядная шина GBL1 (M1) физически разрезаются посредством вышеописанного этапа M1cut. Аналогично, проводные линии M1b, M1c и M1d и глобальная разрядная шина GBL1 (M1) физически разрезаются посредством вышеописанного этапа M1cut.

В дополнение, глобальная разрядная шина GBL1 (M1) соединена с глобальной разрядной шиной GBL1 (M2) через переходной контакт V1.

На фиг. 6 в каждом из переключающих транзисторов 24-1 по 24-4, четыре транзистора управляются как один транзистор. Альтернативно, в каждом из переключающих транзисторов 24-1 по 24-4 больше, чем четыре транзистора, например 8 транзисторов или 16 транзисторов, могут управляться как один транзистор.

Проводные линии, обозначенные посредством "M1", формируются посредством одного и того же этапа изготовления, проводные линии, обозначенные посредством "M2", формируются посредством одного и того же этапа изготовления, и проводные линии, обозначенные посредством "LI", формируются посредством одного и того же этапа изготовления. В дополнение, штепсели, обозначенные посредством "V1", формируются посредством одного и того же этапа изготовления. Кроме того, транзисторы 23 массива 11 ячеек, транзисторы 25, и переключающие транзисторы 24-1a, 24-1b, 24-1c, 24-1d, 24-2a, 24-2b, 24-2c, 24-2d, 24-3a, 24-3b, 24-3c, 24-3d, 24-4a, 24-4b, 24-4c, и 24-4d являются транзисторами ячеек одного и того же размера.

Далее, как показано на фиг. 7, структура схемы для схемы 17S1 выбора столбца описывается более подробно. На фиг. 7, как на фиг. 6, для цели простого описания, показаны только четыре локальные разрядные шины LBL и четыре локальные шины LSL истока, и показаны только восемь ячеек MC памяти в массиве 11 ячеек. Так как структура массива 11 ячеек является такой же как структура, описанная со ссылкой на фиг. 6, ее описание здесь пропускается.

Как проиллюстрировано на фиг. 7, схема 17S2 разрядки шин истока включает в себя, например, транзисторы 27-1 по 27-4 сброса. Транзистор 27-1 сброса имеет путь тока с одним концом, соединенным с M1a, и другим концом, соединенным с потенциалом земли, и имеет затворный электрод, в который вводится сигнал RESET1s сброса. Транзистор 27-2 сброса имеет путь тока с одним концом, соединенным с M1b, и другим концом, соединенным с потенциалом земли, и имеет затворный электрод, в который вводится сигнал RESET2s сброса. Транзистор 27-3 сброса имеет путь тока с одним концом, соединенным с M1c, и другим концом, соединенным с потенциалом земли, и имеет затворный электрод, в который вводится сигнал RESET1s сброса. Транзистор 27-4 сброса имеет путь тока с одним концом, соединенным с M1d, и другим концом, соединенным с потенциалом земли, и имеет затворный электрод, в который вводится сигнал RESET2s сброса.

Кроме того, как проиллюстрировано на фиг. 7, схема 17S1 выбора столбца включает в себя переключающие транзисторы 26-1 по 26-4. Переключающий транзистор 26-1 включает в себя переключающие транзисторы (транзисторы ячеек) 26-1a, 26-1b, 26-1c и 26-1d, каждый из которых имеет путь тока с одним концом, соединенным с проводной линией M1a через проводную линию LI-9, и другим концом, соединенным с глобальной шиной GSL1 (M1) истока через проводную линию LI-10, и имеет затворный электрод, в который вводится сигнал CGE1s управления.

В дополнение, переключающий транзистор 26-2 включает в себя переключающие транзисторы (транзисторы ячеек) 26-2a, 26-2b, 26-2c и 26-2d, каждый из которых имеет путь тока с одним концом, соединенным с проводной линией M1b через проводную линию LI-11, и другим концом, соединенным с глобальной шиной GSL1 (M1) истока через проводную линию LI-12, и имеет затворный электрод, в который вводится сигнал CGE2s управления.

Переключающий транзистор 26-3 включает в себя переключающие транзисторы (транзисторы ячеек) 26-3a, 26-3b, 26-3c и 26-3d, каждый из которых имеет путь тока с одним концом, соединенным с проводной линией M1c через проводную линию LI-13, и другим концом, соединенным с глобальной шиной GSL1 (M1) истока через проводную линию LI-14, и имеет затворный электрод, в который вводится сигнал CGE3s управления.

Переключающий транзистор 26-4 включает в себя переключающие транзисторы (транзисторы ячеек) 26-4a, 26-4b, 26-4c и 26-4d, каждый из которых имеет путь тока с одним концом, соединенным с проводной линией M1d через проводную линию LI-15, и другим концом, соединенным с глобальной шиной GSL1 (M1) истока через проводную линию LI-16, и имеет затворный электрод, в который вводится сигнал CGE4s управления.

Между тем, проводная линия M1a и глобальная шина GSL1 (M1) истока физически разрезаются посредством вышеописанного этапа M1cut. Аналогично, проводные линии M1b, M1c и M1d и глобальная шина GSL1 (M1) истока физически разрезаются посредством вышеописанного этапа M1cut.

В дополнение, глобальная шина GSL1 (M1) истока соединена с глобальной шиной GSL1 (M2) истока через переходной контакт V1.

На фиг. 7, в каждом из переключающих транзисторов 26-1 по 26-4, четыре транзистора управляются как один транзистор. Альтернативно, в каждом из переключающих транзисторов 24-1 по 24-4, более чем четыре транзистора, например, 8 транзисторов или 16 транзисторов, могут управляться как один транзистор.

Проводные линии, обозначенные посредством "M1", формируются посредством одного и того же этапа изготовления, проводные линии, обозначенные посредством "M2", формируются посредством одного и того же этапа изготовления, и проводные линии, обозначенные посредством "LI", формируются посредством одного и того же этапа изготовления. В дополнение, штепсели, обозначенные посредством "V1", формируются посредством одного и того же этапа изготовления. Кроме того, транзисторы 23 массива 11 ячеек, транзисторы сброса (транзисторы ячеек) 27 и переключающие транзисторы (транзисторы ячеек) 26-1a, 26-1b, 26-1c, 26-1d, 26-2a, 26-2b, 26-2c, 26-2d, 26-3a, 26-3b, 26-3c, 26-3d, 26-4a, 26-4b, 26-4c, и 26-4d являются транзисторами ячеек одного и того же размера.

Далее, как показано на фиг. 8 по фиг. 10, описывается размещение схемы 17B1 выбора столбца. На фиг. 8 для цели простого описания показаны только восемь локальных разрядных шин LBL и восемь локальных шин LSL истока, и показаны только восемь числовых шин WL в массиве 11 ячеек. В дополнение, на фиг. 8 по фиг. 10, направление протяженности числовых шин WL (электродов GC затвора) установлено как направление строки (первое направление), и направление, по существу, перпендикулярное к направлению строки, установлено как направление столбца (второе направление). Разрядные шины BL и шины SL истока простираются в направлении столбца.

Как проиллюстрировано на фиг. 8 по фиг. 10, в массиве 11 ячеек, схеме 17B1 выбора столбца и схеме 17B2 разрядки разрядных шин, транзисторы 23, 24, 25 ячеек обеспечены на пересечениях между электродами GC затвора и активными областями AA. Два транзистора 23, 24, 25 ячеек обеспечены в ассоциации с одной активной областью AA.

Как проиллюстрировано на фиг. 8, активные области AA массива 11 ячеек, схемы 17B2 разрядки разрядных шин и схемы 17B1 выбора столбца в первом варианте осуществления простираются в направлении, пересекающем электроды GC затвора под предварительно определенным углом. Конкретно, активные области AA наклонены под предварительно определенным углом к направлению строки. Например, активная область AA в первом варианте осуществления простирается в направлении, пересекающем электрод GC затвора под углом, равным (90-atan(1/3)). Конкретно, активная область AA наклонена под углом, равным приблизительно 71.565°, к направлению строки.

Конфигурация массива 11 ячеек памяти раскрывается в заявке на патент США, номер 13/420,106, поданной 14 марта, 2012 и озаглавленной "SEMICONDUCTOR STORAGE DEVICE". Все описания этих патентных заявок включаются сюда по ссылке.

В дополнение, в первом варианте осуществления, ширина электрода GC затвора (числовой шины WL) в направлении столбца, или расстояние между соседними электродами GC затвора (числовыми шинами WL), равняется по величине результату умножения на 3/2 или умножения на 2/3 ширины активной области AA в направлении строки, или расстояния между соседними активными областями AA.

Например, ширина электрода GC затвора в направлении столбца или расстояние между соседними электродами GC затвора равняется приблизител