Матричный накопитель для запоминающего устройства

Иллюстрации

Показать всеРеферат

МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ЗАПОМИНАМЦЕГО УСТРОЙСТВА, содержащий полупроводниковую подложку, в приповерхностном слое которой расположены диффузионные шины, на поверхности полупроводниковой подложки расположен первый диэлектрический слой с отверстиями , на котором перпендикулярно циффузионным шинам расположены металлические шины, на поверхности металлических шин и первого диэлектрического слоя расположен второй диэлектрический слой с отверстияьш, о тличающийся тем, что, с целью увеличения степени интеграции и Повышения быстродействия накопителя , он содержит другие металлические шины, расположенные на поверхностях диэлектрических слоев, в одних из отверстий диэлектрических слоев на поверхности диффузионньк пин,

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) SU (Ill

4(53) С 11 С 11 40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ HOMHTET СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНЯТИЙ (21) 3263409/18-24 (22) 26.03.81 (46) 23.01.85. Бюл. М - 3 (72) Ю.В. Кружанов, A.М. Авдеев, С.Г. Цемин, В.Э. Сафронов и В.И. Зннс (53) 681.327.66(088.8) (56) 1.Патент США Ф 3721964, кл. 340-173, опублик. 1973.

2. Авторское свидетельство СССР, N - 749257, кл. G 11 С 11/34, 1980 . (прототип). (54)(57) МЛТРИЧН61Й НЛКОПИТЕПЬ ДЛЯ

ЗЛПО11ИНЛЮЩЕГО УСТРОАСТВЛ, содержащий полупроводниковую подложку„ в приповерхностном слое которой расположены диффузионные шины, на поверхности полупроводниковой подложки расположен первый диэлектрический слой с отверс— тиями, на котором перпендикулярно циффузионным шинам расположены мегаллические шины, на поверхности металлических шин и первого диэлектрического слоя расположен второй диэлектрический слой с отверстиями, о тл и ч а ю шийся тем, что, с целью увеличения степени интеграции и повышения быстродействия накопителя, он содержит другие металлические шины, расположенные на поверхностях диэлектрических слоев, в одних из отверстий диэлектрических слоев на поверхности диффузионных шин.

959561

Изобретение относится к области микроэлектроники, а более конкретно—

,к матричным накопителям запоминающих устройств.

Известен интегральный матричный накопитель, содержащий полупроводни-, ковую подложку с диффузионными шинами, на поверхности которой расположен диэлектрический слой с отверстиями, на котором размещены металличес- 10 кие шины, соединенные через отверстия с областями, расположенными в диффузионных шинах. Для уменьшения падения напряжения на диффузионной шине и увеличения быстродействия накопителя в каждой диффузионной шине

0-типа проводимости сделана низкоомная -область, которая электрически соединена с диффузионной шиной металлическими перемычками (1) .

Известный матричный накопитель имеет невысокую степень интеграции.

Наиболее близким техническим решением к предложенному является интегральный матричный накопитель, со- 25 держащий полупроводниковую подложку с диффузионными шинами, на поверхнос ти которой расположен диэлектрический слой с отверстиями, н котором расположены металлические шины, соеди- 30 ненные через отверстия с областями, размещенными в диффузионных шинах, которые выполнены двухслойными, причем проводимость приповерхностного слоя меньше другЬго, проводимость

35 которого ограничена предельной растворимостью легирующей примеси в материале подложки.

Ограничение проводимости высоколегированного слоя предельной растворимостью легирующей примеси в материале подложки приводит к существенному ограничению быстродействия интегрального матричного накопителя.

Кроме того, применение высоколегиро 45 ванных глубинных слоев накладывает ограничения на повышение степени интеграции накопителя.

Целью изобретения является увеличение степени интеграции и повышение быстродействия накопителя.

Поставленная цель достигается тем, что матричный накопитель для запоминающего устройства, содержащий полупроводниковую подложку, в нрипо- 55 верхностйом слое которой расположены диффузионные шины, на поверхности полупроводниковой подложки расположен первый диэлектрический слой с отверстиями, на котором перпендикулярно диффузионным шинам расположены металлические шины, на поверхности металлических шин и первого диэлектрического слоя расположен второй диэлектрический слой с отверстиями, матричный накопитель дополнительно содержит другие металлические шины, расположенные на поверхностях диэлектрических слоев, в одних из отверстий диэлектрических слоев на поверхности диффузионных шин.

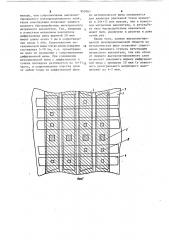

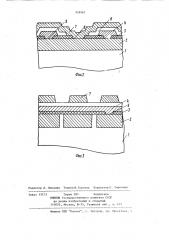

На фиг.1 изображен интегральный матричный накопитель, вид сверху; на фиг.2 — сечение интегрального матричного накопителя вдоль диффузионных шин; на фиг.3 — сечение интегрального матричного накопителя поперек диффузионных шин.

Интегральный матричный накопитель содержит полупроводниковую подложку

1, например, Р -типа проводимости, с диффузионными шинами 2 1 -типа проводимости. На поверхности подложки 1 расположен первый диэлектрический слой 3 (окиси кремния), на котором расположены металлические шины 4, перпендикулярные диффузионным шинам

2. Диффузионные 2 и металлические 4 шины образуют контакты Шоттки в отверстиях 5 в диэлектрическом слое 3, расположенных в тех узлах матрицы накопителя, в которых должно быть запомнено одно из двух логических состояний. Металлические шины 4 изолиро ваны сверху вторым диэлектрическим слоем 6 (например, окисью кремния), на котором расположены другие металлические шины 7. Металлические шины 7 расположены на поверхности диффузионных шин 2 параллельно им и соединяются с ними в точках, отстоящих друг от друга на расстоянии порядка 100 мкм, через отверстия 8 в диэлектрике, образуя невыпрямляющие контакты к областям диффузионных шин 2.

Диффузионные шины 2 оказываются соединенными с металлическими шинами

7, в результате чего сопротивление цепи от металлической шины до любой точки диффузионной шины не превышает сопротивления участка диффузионной шины длиной около 50 мкм, что позволяет существенно увеличить быстродействие накопителя.

Поскольку сопротивление металлической шины (0,03-0,06 Ом/о) намного

9595 меньше, чем сопротивление высоколегированного полупроводникового слоя, такая конструкция позволяет намного повысить быстродействие интегрального матричного накопителя. Так, например в известном матричном накопителе диффузионные шины шириной 20 мкм имеют длину около 3 мм и сопротивление около 4 кОм. Сопротивление металлической шины той же длины и ширины составляет 5- 10 Ом, т.е. пренебрежимо мало по сравнению с сопротивлением диффузионной шины. При соединении металлической шины с диффузионной в точках последняя разбивается на (0+1) 1 часть, и сопротивление участка цепи от любой точки на диффузионной шине

61 4 до металлической шины оказывается для наиболее удаленной точки примерно в 2(0+1) раз меньше, чем в известном матричном накопителе, в результате чего быстродействие накопителя может быть увеличено в десятки и даже сотни раз.

Кроме того, замена высоколегированной полупроводниковой области на металлическую шину позволяет существенно увеличить степень интеграции матри |ного накопителя, так как отказ от нижнего высоколегированного слоя позволяет уменьшить ширину диффузионной шины с примерно 20 мкм (у известного интегрального матричного накопителя) до 4-7 мкм.

959561

Заказ 137/3

Тираж 583 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Про Kòö, ë, Редактор Л. Письман Техред М.Гергель Корректор Е. Сирохман