Узел идентификации адреса магистрального модуля

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61)Дополнительное к авт. саид-ву(22) Заявлено 22. 04. 80 (21) 2914695/18-24 с присоединением заявки ¹ (23) ПриоритетОпубликовано 30.10.82. Бюллетень ¹ 40

Союз Советских

Соцналнстнческнх

Республик

«i>970369

f51tМ Nn з

G 06 F 9/36

Государственный комитет.СССР по делам изобретений и открытий (S3) УДК 681.325 (088 ° 8) ДатЭ опубликования описания 30.10.82 В.Л.Дшхунян, П.P.Èàøåâè÷ и С.С.Коваленко (72) Авторы изобретения (71) Заявитель

Ф (54) УЗЕЛ ИДЕНТИФИКАЦИИ АДРЕСА МАГИСТРАЛЬНОГО

МОДУЛЯ

1 -. 2

Изобретение относится к цифровой обработке информации, в частности к магистральным модулям, выполненным в виде больших интегральных схем.

Узел идентификации адреса магистрального модуля может применяться в микропроцессорах, однокристальных микро-ЭВМ, модулях памяти, больших интегральных схемах обмена информацией и др. модулях микропроцессорных систем с магистральной структурой. Особенностью магистрали является то,что все модули, связанные с нею, адресуются в пределах общего адресного пространства и для каждого модуля отводится определенная ее часть, т.е. число адресов °

Известен узел идентификации адреса магистральных модулей, содержащий дешифратор, входы которого подключены к старшим разрядам адресных шин магистрали, а каждый выход дешифратора подключен к входу выборки одного из модулей (11.

Основными недостатками узла являются отсутствие возможности построения системы на однотипных магистральных модулях беэ дополнительных схем (схема дешифратора является общей для всей совокупности магистральных З0 модулей); наличие дополнительных, отсутствующих в самой магистрали шин выборки и дополнительных выводов выборки в каждом модуле.

Наиболее близким по технической сущности к предлагаемому является узел идентификации адреса магистрального модуля, содержащий компаратор, один из входов которого подключен к группе старших разрядов адресных шин магистрали, а второй через дополнительные внешние выводы связан с источником кода адреса модуля, выход компаратора подключен к внутренней шине выборки модуля. Источник кода адреса модуля представляет набор логических

"1", и ".0", задаваемых обычно подключением внешних контактов к шине земли (логический 0 или к шине питания (логическая "1") .Разрядность источника кода адреса в двоичном представлении, а следовательно, и число дополнительных внешних выводов определяется по формуле (N-log P), где М - разрядность адресной шины магистрали;

Р - число адресов, занимаемых магистральным модулем Г2).

Недостатком известного узла идентификации адреса магистрального модуля является наличие дополнительных

3 97036 с внешних контактов подключения к источнику кода адреса модуля. С ростом степени интеграции появляется реальная возможность реализации модулей процессоров, периферийных контроллеров, боЛьших модулей оперативной и постоянной 5 памяти в одном кристалле. Число внешних выводов при реализации модуля в одном кристалле является важным фактором, определяющим процент выхода годных микросхем, их стоимость, надежность и последующую плотность упаковки на плате.

Цель изобретения — сокращение объема оборудования магистрального модуля.

Поставленная цель достигается тем, что узел идентификации-адреса магистрального модуля, содержащий первую ,схему сравнения, выход которой соединен с выходом выборки узла, первая группа входов первой схемы сравнения соединена с первой группой адресных ® входов узла, содержит регистр адреса модуля, блок памяти и вторую схему сравнения, причем информационные входы регистра адреса модуля соединены с второй группой адресных входов узла 5 группа выходов регистра адреса модуля соединена с второй группой входов первой схемы сравнения, вход управления записью в регистр адреса модуля соединен с выходом второй схемы срав-,ЗО ,нения, первая группа входОв которой соединена с группой выходов блока памяти, вторая группа входов второй схемы сравнения соединена с первой и третьей группами адресных входов 35 узла.

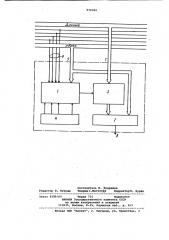

На чертеже приведена структурная электрическая схема.

Узел содержит схемы 1 и 2 сравне- 4О ния, регистр 3 адреса модуля, блок

4 памяти, груяпы адресных входов 5-7 узла, выход 8 выбора узла.

Функциональные узлы идентификации адреса Магистрального модуля осуществляются следующим образом: сначала осуществляется запись данных, передаваемых по входам 7 в регистр 3, для чего по входам 5 передается адрес, код которого равен коду, подаваемому на схему 1 блока 4, Лрн этом на выходе схемы 1 возникает сигнал, поступающий на вход управления записью регистра 3, который фиксирует информацию, пришедшую на его входы. После этого узел готов к дальнейшей работе.

Информация из регистра 3 подается на вход схемы 2, на другой вход которой поступает код с входов 5 узла. При совпадении этих кодов на выходе схемы 2 возникает сигнал, который передается на внутреннюю шину выборки модуля и служит для включения в работу магистрального модуля.

Применение изобретения позволяет сократить число внешних выводов узла.

Формула, изобретения

Узел идентификации адреса магистрального модуля, содержащий первую схему .сравнения, выход которой соединен с выходом выборки узла, первая группа входов первой схемы сравнения соединена с первой группой адресных входов узла, отличающийся тем, что, с целью сокращения объема оборудования, он содержит регистр адреса модуля, блок памяти и вторую схему сравнения, причем информационные входы регистра адреса модуля соединены с второй группой адресных входов узла, группа выходов регистра адреса .модуля соединена с второй группой входов первой схемы сравнения, вход управления записью регистра адреса модуля соединен с выходом второй схемы сравнения, первая группа входов которой соединена с группой выходов блока памяти, вторая группа входов второй схемы сравнения соединена с первой и третьей группами адресных входов узла.

Источники информации, принятые во внимание при экспертизе

1. Соучек Б. Микропроцессоры и микро-ЭВМ. М., "Советское радио", 1979,. с. 244-245.

2. Там же, с. 271, 272, 287-289

" тротатип) .

970369

Составитель М. Кудряшев

Редактор В. Петраш ТехредС.Иигунова Корректорн. Буряк

Заказ 8389/60 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, F.-35, Раушская наб., д. 4/5

- Филиал ППП "Патент", r. Ужгород, ул., Проектная, 4