Устройство для последовательного выделения нулей из @ - разрядного двоичного кода

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ПОСЛЕДоВА .ТБЛЬНОГО.ВЬЩЕЛЕНИЯ НУЛЕЙ ИЗ И-РАЗРЯДНОГО ДВОИЧНОГО КОДА, содержащее группу элементов НЕ и регистр, прИ чем входы сброса триггеров соеди- . йены с входом сброса устройства, отличающееся тем, что, с целью повьшения быстродействия и надежности устройство содержит группу элементов И и группу элементов ИЛИ, первые входи которых соединены с соответствующими информационными входами устройства, второй вход каждого элемента ИЛИ группы соединен с прямым выходом триггера соответствующего разряда регистра, выход каждого элемента ИЛИ группы соединен с входом coqiTве ствующего элемента НЕ группы, выходы элементов HF группы соединены с первыми входами соответствующих элементов И группы, выход каждого элемента ИЛИ группы соединен с соответствующими входами всех последующих элементов И группы , тактовый вход устройства соединен с соответствующим входом каждого элемента И группы, выход каж (Л дого элемента И группы соединен с единичным входом триггера соответС ствующего разряда регистра, и с соответствующим информационным выходом устройства.

(3% (И) СОЮЗ СОВЕТСКИХ

ЯОЦИАДИСТИЧЕСКИХ . РЕСПУБЛИК здр G 06 F 7/06 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3422916/18-24, (22) 22.02.82 (46).23.08.83 Бюл. Р 31. .(72) A.Â.Ãóðüÿíoâ, В.В.Витер, В.A.Ìèùåíêî и С.М.Терешко (53) 681 ° 325 (088.8) (56) 1. Авторское свидетельство СССР

Р 278215, кл. G 06 F 5/02, 1969.

2. Авторское свидетельство СССР

М 739528, кл. G 06 F 7/06, 1980 (прототип). (54)(57) УСТРОЙСГВО ДЛЯ ПОСЛЕДОВА.ТЕЛЬНОГО ВЫДЕЛЕНИЯ НУЛЕЙ ИВ И -РАЗРЯДНОГО ДВОИЧНОГО КОДА, содержащее группу элементов НЕ и регистр, при чем входы сброса триггеров соединены с входом сброса устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и надежности устройство содержит группу элементов И и группу элементов ИЛИ, первые входи которы» соединены с соответствующими информационными входами устройства, второй вход каждого элемента ИЛИ группы соединен с прямым выходом триггера соответствующего разряда регистра, выход каждого элемента

ИЛИ группы соединен с входом соответствующего элемента НЕ группы, выходы элементов HE группы соединены с первыми входами соответствующих элементов И группы, выход каждого элемента ИЛИ группы соединен с соответствующими входами всех последующих элементов И группы, тактовый вход устройства соединен с соответствующим входом кажО дого элемента И группы, выход каждого элемента И группы соединен с единичным входом триггера соответ" ствующего разряда регистра, и с соответствующим информационным выходом устройства.

1037245

Устройство относится к вычислительной re;;-нике и может быть использовано в запоминающих устройствах с ассоциативной выборкой.

Известно устройство для выделения младыего значащеro разряда, содержащее блок выделения нулей и дешифратор t 1j.

Недостатком этого устройства является низкое быстродействие.

Наиболее близким по технической сущности к изобретению является устройство для последовательного выделения нулей из И -разрядного двоичного кода, содержащее в каждом разряде элемент И-НЕ, триггер, 15 а также и элементов НЕ и параллельный И-разрядный сумматор P2).

Недостатком известного устройства является низкое быстродействие и надежность. 20

Целью изобретения является повышение надежности и быстродействия устройства.

Поставленная цель достигается тем, что в устройство для последовательного выделения нулей иэ И -разрядного двоичного кода, содержацее группу элементов НЕ и,регистр, причем входы сброса триггеров регистра соединены с входом сброса устройства, введены группа элементов И и группа элементов ИЛИ, первые входы которых соединены с соответствуюцими информационными входами устройства, второй вход каждого элемента ИЛИ группы соединен с прямым выходом триггера соответственно разряда регистра, выход каждого элемента ИЛИ группы соединен с входом соответствуюцего элемента НЕ группы, выходы элементов НЕ группы 40 соединены с первыми входами соответствующих элементов И группы, выход каждого элемента ИЛИ группы соединен с соответствующими входами всех последующих элементов И группы, так- 45 товый вход устройства соединен с соответствующим входом каждого элемента И группы, выход каждого элемента И группы соединен с единичным входом триггера одноименного раз-50 ряда регистра и с соответствующим информационным выходом устройства.

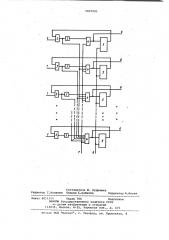

На чертеже представлена блок-схема устройства.

Устройство-содержит инфоРмационные 5 входы 1 устройства, элементы ИЛИ 2 группы, элементы HE 3 группы, элементы И 4 группы, триггеры 5 регистра, информационные выходЫ 6 устройства, тактовый вход 7 устройства, вход сброса 8 устройства.

Устройство работает следующим об- . разом.

Сигналом с входа 8 все триггеры 5 устанавливаются в нулевое состояние.

На прямых выходах триггеров устанавливается потенциал логического нуля.

После этого устройство готово к работе. На информационные входы 1 подается -разрядный двоичныи код. B тех разрядах, где присутствуют единица, проход сигнала с входа 7 через соответствующии элемент И 4 на вход установки триггера 5 в единичное состояние запрещен потенциалом, соответствующим логическому нулю с вы- . хода соответствующего элемента НЕ 3.

В тех разрядах двоичного кода, где присутствуют нули, потенциал, соответствующий,:.логической единице с выхода соответствующего элемента

HE 3, разрешает прохождение сигнала с входа 7 через:элемент И 4 данного разряда в том случае, если во всех предыдущих (младших ) разрядах :двоичного кода присутствуют единицы

1 в этом случае на входы элементов

ИЛИ 2 предыдущих разрядов подается потенциал логической единицы, который поступает па соответствующие входы элементов И. 4, Причем полное совпадение потенциалов логической единицы возможно только в самом младшем двоичном разряде считая только те разряды, где на входы устройства поступает код нуль), либо в том случае, если все предыдущие нули двоичного кода уже выделены, так как в результате выделения нулей триггер 5 соответствующего разряда импульсом с выхода элемента И

4 устанавливается в единичное состояние и потенциа.л с прямого выхода триггера через элемент ИЛИ 2 дает разреыение на выделение следующего по порядку более старшего разряда, в котором присутствует нуль.

На выходе предлагаемого устройства последовательно во времени появляются импульсы, снимаемые с выходов элементов И 4 тех разрядов, значения которых равны нулю.

Применение изобретения позволяет повысить быстродействие устроиства и его надежность.

t I II

- I l l t

Составитель М. Кудряшев.

Редактор Г.Волкова Техред A.Áàáèíåö Корректор A ° Ильин

Заказ 6011/5О Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, К-35, Раушская наб., д. 4/5

Г

Филиал ППП "Патент", г; Ужгород, ул. Проектная, 4