Способ изготовления самосовмещенных транзисторов со сверхкороткой длиной канала, получаемой нелитографическим методом

Иллюстрации

Показать всеИспользование: для изготовления транзисторов со сверхкороткой длиной канала. Сущность изобретения: способ изготовления транзисторов со сверхкороткой длиной канала включает следующие этапы: осаждение электропроводящего материала на подложку из полупроводникового материала, формирование рельефа первых параллельных полосковых электродов с шагом, определяемым соответствующими правилами конструирования, при этом оставляют открытыми области подложки в виде полосок между первыми электродами, осаждение барьерного слоя, покрывающего первые электроды вплоть до подложки, легирование подложки в открытых областях, осаждение электропроводящего материала поверх легированных областей подложки с формированием вторых параллельных полосковых электродов, удаление барьерного слоя, при котором оставляют вертикальные каналы, проходящие вниз до нелегированных областей подложки между первыми и вторыми электродами, легирование подложки в открытых областях нижней части каналов, заполнение каналов барьерным материалом, удаление первых электродов, при котором оставляют промежутки между вторыми электродами и открывают между ними области подложки, легирование открытых областей подложки в промежутках, из которых были удалены первые электроды, осаждение электропроводящего материала в указанных промежутках для восстановления первых электродов и получения тем самым электродного слоя, содержащего первые и вторые параллельные полосковые электроды, по существу, равной ширины, которые граничат с легированной подложкой и отделены друг от друга только тонким слоем барьерного материала, при этом, в зависимости от легирующих примесей, использованных на этапах легирования, первые электроды образуют электроды истока или стока, а вторые электроды - соответственно электроды стока или истока транзисторных структур, осаждение изолирующего барьерного слоя поверх электродов и разделительных барьерных слоев, осаждение электропроводящего материала поверх барьерного слоя и формирование на указанном электропроводящем материале рельефа параллельных полосковых электродов затвора, ориентированных поперечно электродам стока и истока, с получением тем самым матрицы структур полевых транзисторов с очень короткой длиной канала и произвольно большой шириной канала, определяемой шириной электрода затвора. Техническим результатом изобретения является достижение сверхмалой длины каналов транзисторов с использованием технологических приемов, не связанных с литографией, за счет совмещения элементов, при сокращении площади, занимаемой схемой на подложке. 10 з.п. ф-лы, 17 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к способу изготовления транзисторов со сверхкороткой длиной канала.

Уровень техники

Целью многих исследований является уменьшение размера электронных схем (на подложках из кремния и прочих материалов). Это сочетается с попытками увеличить скорость переключения, сокращая длину канала в большей степени, чем это позволяют правила конструирования и возможности литографии. В сфере полупроводниковых технологий большая доля усилий направлена на уменьшение габаритов электронных схем. Для фотолитографии предельно возможные размеры элементов в скором времени будут уже достигнуты и поэтому идут очень серьезные работы в области рентгеновской литографии и поиски других, более экзотических подходов с целью освоения до 2010 года в производственных условиях ширины линий и расстояний между линиями порядка 0,04 мкм (40 нм). Правда, пока указанные значения в большой степени отражают лишь цели разработчиков, например создание мономолекулярных ключей, нанопереключателей и т. п.

Более обещающими могут быть альтернативные приемы формирования рисунка рельефа без привлечения литографии, например технологии микроформирования рельефа или самосборки. Однако последние являются еще более экзотическими, чем самые смелые эксперименты в области литографии, так как они вводят совершенно новые процессы и оборудование в очень консервативную отрасль промышленности. К тому же ни одна из этих двух упомянутых технологий в настоящее время не обладает, а возможно, никогда не будет обладать фактическим потенциалом, который позволил бы строить сложные схемы, отчасти из-за проблемы совмещения, отчасти из-за проблем, связанных с построением многослойных структур. Прочие технологии (например, использование твердых штампов, см. Obducat) сопряжены с такими же трудностями.

Проблемы, которые не могут быть решены известными в настоящее время технологиями, следующие: 1) получение каналов (т.е. расстояний между электродами истока и стока) сверхмалой длины (в несколько атомов); 2) достижение сверхмалой длины каналов при помощи либо стандартных методов работы с кремнием, стандартных приемов изготовления и стандартного оборудования, либо посредством нестандартных технологических приемов, не связанных с литографией; 3) использование каналов сверхмалой длины для сокращения площади, занимаемой схемой на подложке, т.е. для построения более плотной схемы при помощи данных средств литографии/формирования рельефа; 4) достижение вышеуказанных результатов с самосовмещением элементов.

Раскрытие изобретения

Таким образом, задачей, решаемой настоящим изобретением, является создание способа, который эффективно справляется с вышеперечисленными проблемами, внутренне присущими известным на настоящее время технологическим приемам.

Решение задачи, поставленной перед изобретением, а также получение целого ряда дополнительных свойств и преимуществ достигаются при помощи способа, соответствующего настоящему изобретению, который включает следующие этапы:

a) осаждают электропроводящий материал на подложку из полупроводникового материала,

b) на электропроводящем материале формируют рельеф первых параллельных полосковых электродов с шагом, определяемым соответствующими правилами конструирования, оставляя при этом открытыми области подложки в виде полосок между первыми электродами,

c) осаждают барьерный слой, покрывающий первые электроды вплоть до подложки,

d) производят легирование подложки в открытых областях,

e) осаждают электропроводящий материал поверх легированных областей подложки, формируя вторые параллельные полосковые электроды,

f) удаляют барьерный слой, покрывающий первые электроды, оставляя вертикальные каналы, проходящие вниз до нелегированных областей подложки между первыми и вторыми электродами,

g) производят легирование подложки в открытых областях нижней части каналов,

h) заполняют каналы барьерным материалом,

i) удаляют первые электроды, оставляя промежутки между вторыми электродами и открывая между ними области подложки,

j) производят легирование открытых областей подложки в промежутках, из которых были удалены первые электроды,

k) осаждают электропроводящий материал в указанных промежутках для восстановления первых электродов и получения тем самым электродного слоя, содержащего первые и вторые параллельные полосковые электроды, по существу, равной ширины, которые граничат с легированной подложкой и отделены друг от друга только тонким слоем барьерного материала, при этом, в зависимости от легирующих примесей, использованных на этапах легирования, первые электроды образуют электроды истока или стока, а вторые электроды - соответственно электроды стока или истока транзисторных структур,

l) осаждают изолирующий барьерный слой поверх электродов и разделительных барьерных слоев,

m) осаждают электропроводящий материал поверх барьерного слоя и

n) формируют на указанном электропроводящем материале рельеф параллельных полосковых электродов затвора, ориентированных поперечно электродам стока и истока, с получением тем самым матрицы структур полевых транзисторов с очень короткой длиной канала и произвольно большой шириной канала, определяемой шириной электрода затвора.

В способе, соответствующем настоящему изобретению, электропроводящий материал предпочтительно является металлом. Альтернативно, в качестве электропроводящего материала может быть выбран органический материал, желательно полимерный или сополимерный материал.

В общем случае желательно, чтобы на этапах формирования рисунка рельефа использовалась фотомикролитография, но равным образом желательно, чтобы на этапах формирования рисунка рельефа могли быть использованы нелитографические средства.

Согласно способу по настоящему изобретению желательно, чтобы удаление барьерных слоев и/или электродов производилось посредством травления.

Формирование тонкопленочного барьерного слоя предпочтительно производится посредством селективного осаждения; как вариант, тонкопленочный барьерный слой можно формировать путем напыления.

При осуществлении способа по настоящему изобретению желательно, чтобы формирование рельефа выполнялось посредством травления.

Желательно также, чтобы в качестве материала полупроводниковой подложки был выбран кремний.

В способе, соответствующем настоящему изобретению, для получения индивидуальных полевых транзисторов или контуров, содержащих более одного транзистора данного вида, матрицу транзисторных структур предпочтительно делят на соответствующие зоны.

Краткое описание чертежей

Для лучшего понимания изобретения ниже приводится поэтапное описание способа получения транзисторов с примерами вариантов осуществления различных этапов, которое рекомендуется рассматривать вместе с прилагаемыми чертежами.

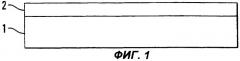

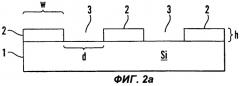

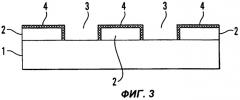

Чертежи (фиг.1, 2а, 3-11а, 12 и 13) иллюстрируют последовательность технологических этапов способа получения транзисторных структур, соответствующего настоящему изобретению, путем представления поперечного сечения структур, формируемых на каждом этапе,

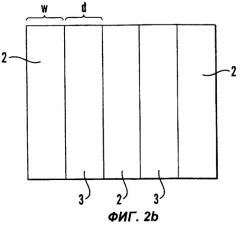

фиг.2b представляет собой вид сверху структур, изображенных в сечении на фиг.2а,

фиг.11b представляет собой вид сверху структур, изображенных в сечении на фиг.11а,

фиг.14а представляет собой вид сверху матрицы полевых транзисторов, полученной способом, соответствующим настоящему изобретению, с очертаниями каналов и электродов истока и стока, показанными штриховыми линиями,

фиг.14b представляет собой сечение матрицы по фиг.14а плоскостью А-А.

Осуществление изобретения

Далее будет приведено поэтапное описание способа, соответствующего настоящему изобретению.

На фиг.1 показана подложка 1 из полупроводникового материала с соответствующим барьерным слоем, на который произведено осаждение слоя 2 электропроводящего материала. Данный материал может являться любым электропроводящим материалом, как неорганическим, так и органическим, который пригоден для нанесения подходящим методом осаждения. Сама подложка, в зависимости от выбранного материала, может быть жесткой или гибкой. Желательно, чтобы подложка была кремниевой. Затем на электропроводящем слое 2 подходящим способом формируют, например, посредством фотомикролитографии с последующим травлением рисунок рельефа в виде первых параллельных полосковых электродов, как показано на фиг.2а и на соответствующем виде сверху (фиг.2b). Шаг, то есть ширина w электрода плюс расстояние d до следующего электрода, конечно, будет зависеть от соответствующих правил конструирования и может соответствовать минимальному размеру f элемента, который ограничен возможностями технологического процесса. В таком случае значения w и d будут примерно равными, хотя, конечно, ничто не мешает сделать величину d гораздо большей, чем w. При формировании рельефа остаются впадины 3 между первыми электродами 2, как показано на фиг.2а, и теперь эти параллельные полосковые электроды 2, которые в действительности могут быть сделаны очень тонкими, т.е. с высотой h гораздо меньшей их ширины w, покрывают, как показано на фиг.3, тонкой пленкой барьерного слоя 4, который проходит поверх первых электродов 2 и вниз до подложки 1 во впадинах 3. Толщина барьерного слоя не ограничена никакими правилами конструирования и, следовательно, может быть очень малой, вплоть до моноатомных размеров.

Дном каждой впадины 3 будет соответствующий открытый участок подложки 1, как это показано на фиг.3. Далее, как показано на фиг.4, производят легирование подложки 1 на этих открытых участках с целью получения в подложке 1 легированных областей 5 с требуемым типом проводимости, например, с электронной проводимостью (проводимостью n-типа), либо с дырочной проводимостью (проводимостью p-типа). На следующем технологическом этапе, показанном на фиг.5, впадины 3 заполняют электропроводящим материалом 6, чтобы поверх легированных областей 5 в подложке 1 образовать вторые параллельные полосковые электроды 6. После этого, как показано на фиг.6, при помощи любого подходящего процесса, например травления, удаляют барьерный слой 4 с первых электродов 2, оставляя вертикальные каналы, или канавки 7 между первыми и вторыми электродами 2, 6. В результате на дне вертикальных каналов 7 откроются нелегированные участки подложки 1, и в процессе второй операции легирования, показанной на фиг.7, производят легирование этих участков подложки с целью получения в ней легированных областей 8. Очевидно, что легирующую примесь теперь выбирают так, чтобы создать в областях 8 подложки проводимость, например, p-типа, если в областях 5 при легировании была создана проводимость n-типа, и наоборот.

Затем вертикальные каналы (канавки) 7 заполняют изолирующим барьерным материалом 4, который, например, может быть осажден путем управляемого напыления или осажден в виде барьерного слоя целиком на всю пластину с последующим удалением лишнего материала. При этом данный барьерный материал 4 будет теперь, естественно, покрывать участки подложки 1, лежащие выше легированных областей 8, как это показано на фиг.8. На следующем технологическом этапе удаляют первые электроды 2, оставляя впадины (канавки) 3' между вторыми электродами 6 с барьерными слоями 4, как это показано на фиг.9. Удаление первых электродов 2 может быть произведено, например, при помощи фотомикролитографии и травления, после чего следует третья операция легирования, посредством которой в открытые и нелегированные участки подложки 1 в канавках 3' будет внедрена примесь с целью получения в подложке легированных областей 9, как показано на фиг.10.

Легирование областей 9 будет производиться с целью получения соответствующего типа проводимости, то есть n-типа, если в областях 5 при легировании была сформирована проводимость n-типа, а в областях 8 - проводимость p-типа. Естественно, может быть получено и обратное сочетание типов проводимости. На следующем этапе технологического процесса производят восстановление первых электродов, как показано на фиг.11а, путем простого заполнения канавок 3' над легированными областями 9 подложки 1 тонкой пленкой соответствующего электропроводящего материала, который опять-таки может быть либо неорганическим, либо органическим. В любом случае следует понимать, что для первых и для вторых электродов 2, 6 желательно использовать электропроводящий материал одного и того же типа. Получаемая в итоге структура показана на фиг.11b.

Видно, что первые и вторые электроды 2 и 6, соприкасаясь с областями 5, 8, 9 в подложке 1, имеющими соответствующее легирование, могут образовать параллельные полосковые, очень близко расположенные электроды, соответственно истока и стока в транзисторной структуре. Длина канала L, т.е. расстояние между, например, электродом 2 истока и электродом 6 стока (фиг.11а) под барьерным слоем 4 определяется шириной легированной области 8 в подложке. Эта длина может быть сделана крайне малой - если требуется, гораздо меньше 1 нм, благодаря тому, что толщина δ барьерного слоя 4 получается в процессе осаждения исключительно тонкой пленки барьерного материала, а на этот процесс не накладывается никаких ограничений, связанных с правилами конструирования. Специалистам в данной области хорошо известно, что возможно осаждение таких барьерных слоев даже моноатомной толщины, о чем упоминалось ранее. Следовательно, длина L канала в транзисторной структуре, изготовленной способом, соответствующим настоящему изобретению, может быть почти сколь угодно малой, а это, как будет видно, является крайне желательным свойством, например, в полевых транзисторах.

Кроме того, верхние поверхности электродов 2, 6 истока и стока снабжают барьерным слоем 4, таким что электроды 2, 6 в любом случае оказываются взаимно изолированными, и их верхние поверхности также изолированы, как показано на фиг.12, Теперь, поверх нанесенного на всю пластину барьерного слоя 4, также на всю пластину наносят слой в виде еще одной тонкой пленки 10 электропроводящего материала, после чего на этом слое 10 формируют рельеф с целью получения электродов затвора в транзисторных структурах, изготовленных способом, соответствующим настоящему изобретению. Должно быть понятно, что фактическое формирование рельефа электродов затвора может производиться посредством технологических операций, подобных тем, какие использовались при формировании первых и вторых электродов 2, 6, и разные стадии этого процесса будут копией этапов, показанных на фиг.1, 2а, 3 и 5. Поэтому может быть получена очень плотная сетка электродов 10.

Каждый второй из набора электродов затвора создается на этапе формирования рисунка рельефа, который может основываться, например, на фотомикролитографии с последующим травлением, выполняемым перед осаждением подходящего барьерного слоя. Из этого, безусловно, вытекает, что возможные размеры электродов затвора обусловлены теми же соображениями, которые брались за основу в отношении размеров первых и вторых электродов 2, 6. Поэтому вполне возможно делать отдельные электроды 10 затвора разной ширины W. Из этого, в свою очередь, следует, что отдельные транзисторные структуры, изготовленные методом, соответствующим настоящему изобретению, можно делать с изменяющимся отношением ширины канала к длине канала, W/L. Специалистам в данной области хорошо известно, что крайне желательно иметь большое отношение W/L, так как величина тока ID стока пропорциональна этому отношению, умноженному на эффективное значение напряжения управления и на величину параметра, зависящего от технологического процесса.

Таким образом, транзисторы, изготовленные способом, соответствующим настоящему изобретению, могут дать ряд преимуществ. Например, скорость переключения транзисторов зависит от различных факторов, но главным структурным параметром, влияющим на скорость переключения, всегда будет расстояние L между электродами истока и стока, так как носителям заряда требуется определенное время, чтобы преодолеть это расстояние. Другими словами, чем меньше расстояние L, тем выше, при прочих равных условиях, скорость переключения. Известные на сегодняшний день технические решения и современные технологии содержат и будут содержать ограничения со стороны минимальных размеров элемента, допускаемых применяемыми технологическими процессами. Например, применение литографии с разрешением 0,18 мкм предполагает минимальную длину канала 180 нм. Хотя литография, в соответствии с современными стандартами, по-прежнему будет использоваться на этапе формирования рисунка рельефа электродов, очевидно, что способ, соответствующий настоящему изобретению, позволяет фактически уменьшить длину L канала до значений, например, гораздо меньших 10 нм, так как на толщину барьерного слоя нет никаких ограничений со стороны правил конструирования.

Может оказаться, что на ширину W электрода затвора, соответствующую ширине канала, правила конструирования, относящиеся к формированию рисунка рельефа, который используется для создания данного конкретного электрода, накладывают ограничение снизу. В этом случае, как показано на фиг.14b, коррекцию фактической ширины W электродов затвора, сформированных на этапе, подобном показанному на фиг.5 для создания электродов 6, можно осуществить простым увеличением толщины барьерного слоя 4 между электродами 10 затвора перед тем, как выполнять осаждение дополнительного электродного материала в канавки под электроды затвора, рисунок рельефа которых уже сформирован. Следовательно, для каждого второго электрода затвора в матрице транзисторной структуры теперь будет возможно сформировать электроды затвора так, что можно получать транзисторы с разной шириной W.

Отсюда следует, что одним из самых важных аспектов способа, соответствующего настоящему изобретению, является возможность управления соотношением ширины W канала и длины L канала, то есть отношением W/L, которое представляет собой очень важный расчетный параметр. Действительно, данный параметр служит масштабным коэффициентом для тока ID стока. Более того, настоящее изобретение позволит изготовлять полевые транзисторы любого типа. Кроме того, можно будет изготовлять на одной подложке полевые транзисторы, идентичные по структуре, но с разными значениями выбранных расчетных параметров. Например, на одной подложке можно изготовить два или большее число МОП-транзисторов, имеющих одинаковое пороговое напряжение VT, но разные предельно допустимые токи, так как будет возможно использовать различные значения для W/L. Высокие значения тока ID стока, например, порядка нескольких миллиампер, могут быть получены только у транзисторов с высоким отношением W/L. В случае технологий, применяемых в настоящее время, это означает, что речь идет о приборах, использующих очень большую площадь подложки. В случае же настоящего изобретения отношение W/L может быть выбрано почти произвольно большим, и при этом не будет занята недопустимо большая площадь на подложке. Замечено, что отношение W/L можно увеличивать с целью обеспечения любого требуемого уровня тока. Однако современная технология предполагает, что это означает увеличение площади затвора и соответственно увеличение электрической емкости прибора, что отрицательно сказывается на скорости переключения транзистора. Например, для MOSFET транзисторов отношение W/L ограничено и составляет не более 10. Эти нежелательные ограничения полностью устраняются, если изготовление транзисторов осуществлять по способу, соответствующему настоящему изобретению.

Описанный предпочтительный вариант осуществления применительно к формированию рисунка рельефа электродных структур базируется на использовании традиционных процессов микрофотолитографии и травления. Однако следует учесть, что способ, соответствующий настоящему изобретению, одинаково успешно может быть осуществлен и при использовании более сложных процессов формирования рельефа, включающих мягкую литографию и использование средств, не связанных с литографией, таких как, например, твердые или мягкие штампы для получения требуемых рисунков рельефа. Чтобы получить дополнительное снижение минимальных размеров элемента, можно также формировать рельеф электродов, например, при помощи печатной технологии. Такую печатную технологию можно осуществить на основе так называемой нанопечати, которая развивается в настоящее время. Предполагается, что данным методом можно будет получать, например, рельеф электродов с минимальным размером элемента, вплоть до 10 нм и даже менее, с сопоставимыми значениями толщины пленок. Таким образом, можно будет формировать рельеф в масштабе, сравнимом с длиной канала, которая достижима способом, соответствующим настоящему изобретению.

Кроме того, способ, соответствующий настоящему изобретению, мог бы, при надлежащем выборе дополнительных этапов последующей обработки или дополнительных промежуточных этапов, позволить изготовлять на одной и той же подложке более сложные схемные структуры. Действительно, он обеспечивает возможность выбирать соответствующие типы проводимости и расчетные размеры и использовать это для изготовления нестандартных полевых транзисторов особого типа. Кроме того, может осуществляться осаждение дополнительных промежуточных слоев, например, для изготовления устройств с матричной адресацией на основе транзисторной памяти или для формирования комплементарных транзисторных схем. Очевидно, например, что можно удалять какие-то части транзисторных структур или транзисторные структуры целиком, к примеру, на этапах травления, и заменять их различными пассивными элементами, сформированными, например, посредством тонкопленочной технологии, в частности, резисторами или соединительными линиями, создавая таким образом более сложные схемы, полностью интегрированные с первоначальными транзисторными структурами, изготовленными способом, соответствующим настоящему изобретению.

1. Способ изготовления транзисторов со сверхкороткой длиной канала, включающий следующие этапы:

a) осаждают электропроводящий материал на подложку из полупроводникового материала,

b) на электропроводящем материале формируют рельеф первых параллельных полосковых электродов с шагом, определяемым соответствующими правилами конструирования, оставляя при этом открытыми области подложки в виде полосок между первыми электродами,

c) осаждают барьерный слой, покрывающий первые электроды вплоть до подложки,

d) производят легирование подложки в открытых областях,

e) осаждают электропроводящий материал поверх легированных областей подложки, формируя вторые параллельные полосковые электроды,

f) удаляют барьерный слой, покрывающий первые электроды, оставляя вертикальные каналы, проходящие вниз до нелегированных областей подложки между первыми и вторыми электродами,

g) производят легирование подложки в открытых областях нижней части каналов,

h) заполняют каналы барьерным материалом,

i) удаляют первые электроды, оставляя промежутки между вторыми электродами и открывая между ними области подложки,

j) производят легирование открытых областей подложки в промежутках, из которых были удалены первые электроды,

k) осаждают электропроводящий материал в указанных промежутках для восстановления первых электродов и получения тем самым электродного слоя, содержащего первые и вторые параллельные полосковые электроды, по существу, равной ширины, которые граничат с легированной подложкой и отделены друг от друга только тонким слоем барьерного материала, при этом в зависимости от легирующих примесей, использованных на этапах легирования, первые электроды образуют электроды истока или стока, а вторые электроды - соответственно электроды стока или истока транзисторных структур,

1) осаждают изолирующий барьерный слой поверх электродов и разделительных барьерных слоев,

m) осаждают электропроводящий материал поверх барьерного слоя и

n) формируют на указанном электропроводящем материале рельеф параллельных полосковых электродов затвора, ориентированных поперечно электродам стока и истока, с получением тем самым матрицы структур полевых транзисторов с очень короткой длиной канала и произвольно большой шириной канала, определяемой шириной электрода затвора.

2. Способ по п.1, отличающийся тем, что электропроводящий материал является металлом.

3. Способ по п.1, отличающийся тем, что в качестве электропроводящего материала выбирают органический материал, предпочтительно полимерный или сополимерный материал.

4. Способ по п.1, отличающийся тем, что на этапах формирования рисунка рельефа используют фотомикролитографию.

5. Способ по п.1, отличающийся тем, что на этапах формирования рисунка рельефа используют нелитографические средства.

6. Способ по п.1, отличающийся тем, что удаление барьерных слоев и/или электродов выполняют посредством травления.

7. Способ по п.1, отличающийся тем, что формирование тонкопленочного барьерного слоя выполняют посредством селективного осаждения.

8. Способ по п.1, отличающийся тем, что формирование тонкопленочного барьерного слоя выполняют посредством напыления.

9. Способ по п.1, отличающийся тем, что формирование рельефа выполняют посредством травления.

10. Способ по п.1, отличающийся тем, что в качестве материала полупроводниковой подложки выбирают кремний.

11. Способ по п.1, отличающийся тем, что для получения индивидуальных полевых транзисторов или контуров, содержащих более одного транзистора данного вида, матрицу транзисторных структур делят на соответствующие зоны.