Способ изготовления подложки со структурой тонкопленочных транзисторов

Иллюстрации

Показать всеИзобретение относится к способам изготовления подложек со структурой тонкопленочных транзисторов для применения в панелях отображений. Сущность изобретения: способ изготовления подложки со структурой тонкопленочных транзисторов предусматривает этап, на котором формируют электрод затвора и первое соединение на подложке, этап, на котором формируют изолирующую пленку затвора, которая имеет контактное окно в положении, перекрывающем первое соединение, этап, на котором формируют электрод истока и электрод стока, которые перекрывают электрод затвора, и электроды отделены друг от друга, и формируют второе соединение, которое соединено с первым соединением через контактное окно в изолирующей пленке затвора, этап, на котором формируют межслойную изолирующую пленку созданием рисунка во второй изолирующей пленке после последовательного формирования оксидной полупроводниковой пленки и второй изолирующей пленки, и этап, на котором формируют пиксельный электрод путем снижения сопротивления оксидной полупроводниковой пленки, не защищенной межслойной изолирующей пленкой. Изобретение обеспечивает снижение стоимости получения подложки тонкопленочного транзистора, сформированного из оксидного полупроводника со структурой межсоединений на концевой части подложки. 3 н. и 17 з.п. ф-лы, 13 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится к способам изготовления подложек со структурой тонкопленочных транзисторов и более конкретно к способам изготовления подложек со структурой тонкопленочных транзисторов для применения в панелях отображения.

УРОВЕНЬ ТЕХНИКИ

Жидкокристаллическая панель отображения, управляемая активной матрицей, включает в себя подложку со структурой тонкопленочных транзисторов (далее называемого как «TFT»), на которой TFT, служащий в качестве переключающего элемента, создают в каждом пикселе, который является самым маленьким фрагментом изображения.

Подложка со структурой TFT может быть изготовлена, например, следующим образом. На стеклянной подложке последовательно формируют протравливаемую пленку и пленку из фоточувствительной смолы. После этого пленку из фоточувствительной смолы подвергают воздействию света через фотомаску для получения рисунка резиста. Протравливаемую пленку, не защищенную рисунком резиста, протравливают. Эту серию этапов неоднократно повторяют.

В этой связи в жидкокристаллической панели отображения, включающей в себя подложку со структурой TFT, для сокращения стоимости производства обычно предлагали такие способы изготовления подложки со структурой TFT, как увеличение размера стеклянной подложки и сокращение числа фотомасок.

Например, ПАТЕНТНЫЙ ДОКУМЕНТ 1 описывает способ изготовления подложки со структурой TFT, в котором фотомаску с полутоновым рисунком используют для формирования рисунка резиста, имеющего три разных толщины, тем самым сокращая число фотомасок.

В традиционном способе изготовления подложки со структурой TFT с использованием кремниевой полупроводниковой пленки, кремниевую пленку, служащую в качестве полупроводниковой пленки, и проводящую оксидную пленку, служащую в качестве пиксельного электрода, формируют по отдельности. В недавние годы был предложен высокопроизводительный TFT следующего поколения, в котором применяют оксидную полупроводниковую пленку в качестве полупроводниковой пленки.

Например, ПАТЕНТНЫЙ ДОКУМЕНТ 2 описывает TFT-матрицу, в которой пиксельные электроды сформированы из оксидной полупроводниковой пленки, которая составляет тонкопленочные транзисторы (TFT), и способ изготовления TFT-матрицы.

СПИСОК ЦИТИРУЕМОЙ ЛИТЕРАТУРЫ

ПАТЕНТНЫЕ ДОКУМЕНТЫ

ПАТЕНТНЫЙ ДОКУМЕНТ 1: Японская патентная публикация № 2000-164886

ПАТЕНТНЫЙ ДОКУМЕНТ 2: Японская патентная публикация № 2008-40343

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

ТЕХНИЧЕСКАЯ ПРОБЛЕМА

Фиг.13(а)-13(f) представляют виды в разрезе для описания процесса изготовления подложки 150 со структурой TFT, соответствующей TFT-матрице ПАТЕНТНОГО ДОКУМЕНТА 2.

Здесь подложка 150 со структурой TFT включает в себя, например, многочисленные линии затворов (не показаны), продолжающиеся параллельно друг другу, многочисленные линии 113 истоков (смотри фиг.13(f)), продолжающиеся параллельно друг другу в направлении, перпендикулярном линиям затворов, многочисленные тонкопленочные транзисторы 105 (TFT) (смотри фиг.13(f)), обеспеченные на соответственных соответствующих пересечениях линий затворов и линий 113 истоков, то есть в каждом случае для каждого пикселя, который представляет собой самый маленький фрагмент изображения, и многочисленные пиксельные электроды (114с, смотри фиг.13(f)), размещенные в матрице и соединенные с соответственными соответствующими тонкопленочными транзисторами 105 (TFT). Здесь подложка 150 со структурой TFT имеет отображающую область, в которой пиксельные электроды размещены в матрице и которую используют для отображения изображения, и неотображающую область, которую создают вокруг отображающей области. В неотображающей области подложки 150 со структурой TFT линии затворов соединены через контактное окно, образованное в изолирующей пленке 112 затвора, описываемой ниже, с линией соединения, размещенной в том же слое, в котором расположена линия 113 истоков, и изготовленной из того же материала, что линия 113 истоков.

Например, как показано на фиг.13(f), TFT 105 включает в себя электрод 111 затвора, который представляет собой часть или выступающую часть линии затворов на стеклянной подложке 110, изолирующую пленку 112 затвора, расположенную так, чтобы покрывать электрод 111 затвора, и полупроводниковый слой 114, размещенный на изолирующей пленке 112 затвора, перекрывающий электрод 111 затвора. Здесь, например, как показано на фиг.13(f), полупроводниковый слой 114 включает канальную область 114а, перекрывающую электрод 111 затвора, область 114b истока, смежную с канальной областью 114а и расположенную с ее левой стороны и соединенную с линией 113 истоков, и область 114с стока, смежную с канальной областью 114а и расположенную с ее правой стороны и включенную в пиксельный электрод.

Далее в общих чертах описан способ изготовления подложки 150 со структурой TFT, имеющей вышеуказанную конфигурацию.

Сначала, как показано на фиг.13(а), на стеклянной подложке 110 формируют электрод 111 затвора с использованием первой фотомаски.

Затем, как показано на фиг.13(b), с использованием второй фотомаски формируют изолирующую пленку 112 затвора, которая покрывает электрод 111 затвора и имеет контактное окно (не показано) в неотображающей области.

После этого, как показано на фиг.13(с), с использованием третьей фотомаски на изолирующей пленке 112 затвора формируют линию 113 истоков.

Кроме того, как показано на фиг.13(d), с помощью четвертой фотомаски на изолирующей пленке 112 затвора и линии 113 истоков формируют оксидный полупроводниковый слой 114.

После этого, как показано на фиг.13(е), с помощью пятой фотомаски на межсоединении 113 истоков и оксидном полупроводниковом слое 114 формируют межслойную изолирующую пленку 115.

Наконец, как показано на фиг.13(f), оксидный полупроводниковый слой 114, не защищенный межслойной изолирующей пленкой 115, обрабатывают плазмой Р для снижения сопротивления, тем самым создавая канальную область 114а, область 114b истока и область 114с стока (пиксельный электрод).

Таким образом, подложка 150 со структурой TFT может быть изготовлена с использованием пяти фотомасок.

Однако в подложке 150 со структурой TFT область 114b истока и область 114с стока, поврежденные при плазменной обработке, являются смежными с канальной областью 114а, и поэтому есть вероятность нарушения характеристик TFT 105. Более того, хотя для процесса производства требуются пять фотомасок, область 114b истока оксидного полупроводникового слоя 114, за исключением области 114с стока, действующей в качестве пиксельного электрода, не покрыта межслойной изолирующей пленкой 115, и поэтому, например, в жидкокристаллической панели отображения, включающей в себя подложку 150 со структурой TFT, потенциал линии 113 истоков приложен непосредственно к жидкокристаллическому слою, и поэтому в данном процессе производства требуется дополнительный этап создания любой изолирующей пленки, покрывающей область 114b истока. Поэтому есть простор для усовершенствования.

Настоящее изобретение было выполнено с учетом вышеописанных проблем. Целью настоящего изобретения является изготовление тонкопленочного транзистора, сформированного из оксидного полупроводника и имеющего удовлетворительные характеристики, и подложки со структурой тонкопленочных транзисторов, имеющей структуру межсоединений на концевой части подложки, настолько экономичным путем, насколько это возможно.

РАЗРЕШЕНИЕ ПРОБЛЕМЫ

Для достижения этой цели согласно настоящему изобретению в оксидной полупроводниковой пленке для формирования пиксельного электрода не создают рисунок отдельно и участок для формирования тонкопленочного транзистора из оксидной полупроводниковой пленки покрывают межслойной изолирующей пленкой.

Более конкретно, способ изготовления подложки со структурой тонкопленочных транзисторов согласно настоящему изобретению включает в себя этап формирования затворного слоя, на котором формируют электрод затвора и первое межсоединение на подложке, этап формирования изолирующей пленки затвора, на котором формируют первую изолирующую пленку, покрывающую электрод затвора и первое межсоединение, и после этого в первой изолирующей пленке создают рисунок для формирования контактного окна в положении, перекрывающем первое межсоединение, тем самым создавая изолирующую пленку затвора, этап формирования истокового слоя, на котором формируют проводящую пленку, покрывающую изолирующую пленку затвора, и после этого в проводящей пленке создают рисунок для формирования электрода истока и электрода стока, перекрывающих электрод затвора и отделенных друг от друга, и второго межсоединения, пересекающего первое межсоединение и соединенного через контактное окно с первым межсоединением, этап формирования межслойной изолирующей пленки, на котором последовательно формируют оксидную полупроводниковую пленку и вторую изолирующую пленку, покрывающие электрод истока, электрод стока и второе межсоединение, и после этого во второй изолирующей пленке создают рисунок для формирования межслойной изолирующей пленки, и этап формирования пиксельного электрода, на котором снижают сопротивление оксидной полупроводниковой пленки, не защищенной межслойной изолирующей пленкой, для формирования пиксельного электрода.

Вышеописанным способом сначала, например, на этапе формирования затворного слоя, на подложке формируют (первую) проводящую пленку, и после этого в (первой) проводящей пленке, не защищенной первым рисунком резиста, созданным с использованием первой фотомаски, создают рисунок для формирования электрода затвора и первого межсоединения. Затем на этапе формирования изолирующей пленки затвора, на электроде затвора и первом межсоединении формируют первую изолирующую пленку, и после этого в первой изолирующей пленке, не защищенной вторым рисунком резиста, созданным с использованием второй фотомаски, создают рисунок для формирования изолирующей пленки затвора, имеющей контактное окно, для создания структуры межсоединения на концевой части подложки. После этого, на этапе формирования истокового слоя, на изолирующей пленке затвора формируют (вторую) проводящую пленку, и после этого в (второй) проводящей пленке, не защищенной третьим рисунком резиста, сформированным с использованием третьей фотомаски, создают рисунок для формирования электрода истока, электрода стока и второго межсоединения. Здесь первое и второе межсоединения соединены друг с другом через контактное окно, сформированное в изолирующей пленке затвора, и поэтому на концевой части подложки специально образуется структура межсоединения. Кроме того, на этапе формирования межслойной изолирующей пленки, на электроде истока, электроде стока и втором межсоединении последовательно формируют оксидную полупроводниковую пленку и вторую изолирующую пленку, и после этого во второй изолирующей пленке, не защищенной четвертым рисунком резиста, образованным с использованием четвертой фотомаски, создают рисунок для формирования межслойной изолирующей пленки. Наконец, на этапе формирования пиксельного электрода снижают сопротивление оксидной полупроводниковой пленки, не защищенной межслойной изолирующей пленкой, для формирования пиксельного электрода. В результате получают подложку со структурой тонкопленочных транзисторов с использованием четырех из первой, второй, третьей и четвертой фотомасок, и поэтому подложку со структурой тонкопленочных транзисторов, имеющую структуру межсоединения на его концевой части, изготавливают экономично, насколько это возможно. Кроме того, в изготовленной подложке со структурой тонкопленочных транзисторов участок, который образует тонкопленочный транзистор из оксидной полупроводниковой пленки, покрывают межслойной изолирующей пленкой, и поэтому сокращают вероятность повреждения плазмой, подводимой для снижения сопротивления, и т.д., обеспечивая удовлетворительные характеристики тонкопленочного транзистора. Поэтому тонкопленочный транзистор, сформированный из оксидного полупроводника и имеющий удовлетворительные характеристики, и подложку со структурой тонкопленочных транзисторов, имеющую структуру межсоединения на концевой части подложки, изготавливают с настолько низкими затратами, насколько возможно.

Еще один способ изготовления подложки со структурой тонкопленочных транзисторов согласно настоящему изобретению включает в себя этап формирования затворного слоя, на котором формируют электрод затвора и первое межсоединение на подложке, этап формирования изолирующей пленки затвора, на котором последовательно формируют первую изолирующую пленку и оксидную полупроводниковую пленку, покрывающие электрод затвора и первое межсоединение, и после этого в многослойной пленке из первой изолирующей пленки и оксидной полупроводниковой пленки создают рисунок для формирования контактного окна в положении, перекрывающем первое межсоединение, тем самым формируя изолирующую пленку затвора, этап формирования истокового слоя, на котором формируют проводящую пленку, покрывающую оксидную полупроводниковую пленку, и после этого в проводящей пленке создают рисунок для формирования электрода истока и электрода стока, перекрывающих электрод затвора и отделенных друг от друга, и второго межсоединения, пересекающего первое межсоединение и соединенного через контактное окно с первым межсоединением, этап формирования межслойной изолирующей пленки, на котором формируют вторую изолирующую пленку, покрывающую электрод истока, электрод стока и второе межсоединение, и после этого во второй изолирующей пленке создают рисунок для формирования межслойной изолирующей пленки, и этап формирования пиксельного электрода, на котором снижают сопротивление оксидной полупроводниковой пленки, не защищенной межслойной изолирующей пленкой, для формирования пиксельного электрода.

Вышеописанным способом сначала, например на этапе формирования затворного слоя, на подложке формируют (первую) проводящую пленку, и после этого в (первой) проводящей пленке, не защищенной первым рисунком резиста, созданным с использованием первой фотомаски, создают рисунок для формирования электрода затвора и первого межсоединения. Затем, на этапе формирования изолирующей пленки затвора, на электроде затвора и первом межсоединении последовательно формируют первую изолирующую пленку и оксидную полупроводниковую пленку, и после этого в многослойной пленке из первой изолирующей пленки и оксидной полупроводниковой пленки, не защищенной вторым рисунком резиста, созданным с использованием второй фотомаски, создают рисунок для формирования изолирующей пленки затвора, имеющей контактное окно, для создания структуры межсоединения на концевой части подложки. После этого, на этапе формирования истокового слоя, на оксидной полупроводниковой пленке формируют (вторую) проводящую пленку, и после этого в (второй) проводящей пленке, не защищенной третьим рисунком резиста, сформированным с использованием третьей фотомаски, создают рисунок для формирования электрода истока, электрода стока и второго межсоединения. Здесь первое и второе межсоединения соединены друг с другом через контактное окно, сформированное в изолирующей пленке затвора (многослойной пленке из первой изолирующей пленки и оксидной полупроводниковой пленки), и поэтому на концевой части подложки специально образуется структура межсоединения. Кроме того, на этапе формирования межслойной изолирующей пленки, на электроде истока, электроде стока и втором межсоединении формируют вторую изолирующую пленку, и после этого во второй изолирующей пленке, не защищенной четвертым рисунком резиста, образованным с использованием четвертой фотомаски, создают рисунок для формирования межслойной изолирующей пленки. Наконец, на этапе формирования пиксельного электрода, снижают сопротивление оксидной полупроводниковой пленки, не защищенной межслойной изолирующей пленкой, для формирования пиксельного электрода. В результате получают подложку со структурой тонкопленочных транзисторов с использованием четырех из первой, второй, третьей и четвертой фотомасок, и поэтому подложку со структурой тонкопленочных транзисторов, имеющую структуру межсоединения на его концевой части, изготавливают экономично, насколько это возможно. Кроме того, в изготовленной подложке со структурой тонкопленочных транзисторов участок, образующий тонкопленочный транзистор из оксидной полупроводниковой пленки, покрывают межслойной изолирующей пленкой, и поэтому сокращают вероятность повреждения плазмой, подводимой для снижения сопротивления, и т.д., обеспечивая удовлетворительные характеристики тонкопленочного транзистора. Поэтому тонкопленочный транзистор, сформированный из оксидного полупроводника и имеющий удовлетворительные характеристики, и подложку со структурой тонкопленочных транзисторов, имеющую структуру межсоединения на концевой части подложки, изготавливают с настолько низкими затратами, насколько возможно.

На этапе формирования затворного слоя электрод затвора может быть сделан достаточно широким для достижения границы между электродом стока, образованным на этапе формирования истокового слоя, и пиксельным электродом, созданным на этапе формирования пиксельного электрода.

Вышеописанным способом электрод затвора делают достаточно широким для достижения границы между электродом стока и пиксельным электродом. Поэтому, когда электрод затвора поддерживают при высоком напряжении, сопротивление полупроводникового слоя под электродом стока снижается, и поэтому электрод стока и пиксельный электрод могут быть надежно соединены между собой.

Еще один способ изготовления подложки со структурой тонкопленочных транзисторов согласно настоящему изобретению включает в себя этап формирования затворного слоя, на котором формируют электрод затвора и первое межсоединение на подложке, этап формирования изолирующей пленки затвора, на котором последовательно формируют первую изолирующую пленку и проводящую пленку, покрывающие электрод затвора и первое межсоединение, и после этого создают рисунок в многослойной пленке из первой изолирующей пленки и проводящей пленки для формирования контактного окна в положении, перекрывающем первое межсоединение, тем самым формируя изолирующую пленку затвора, этап формирования истокового слоя, на котором создают рисунок в проводящей пленке для формирования электрода истока и электрода стока, перекрывающих электрод затвора и отделенных друг от друга, и второго межсоединения, пересекающего первое межсоединение в положении контактного окна, этап формирования межслойной изолирующей пленки, на котором последовательно формируют оксидную полупроводниковую пленку и вторую изолирующую пленку, покрывающие электрод истока, электрод стока и второе межсоединение, и после этого создают рисунок во второй изолирующей пленке для формирования межслойной изолирующей пленки, и этап формирования пиксельного электрода, на котором снижают сопротивление оксидной полупроводниковой пленки, не защищенной межслойной изолирующей пленкой, формируя пиксельный электрод и делая проводящими первое и второе межсоединения.

Вышеописанным способом сначала, например, на этапе формирования затворного слоя, на подложке формируют (первую) проводящую пленку, и после этого в (первой) проводящей пленке, не защищенной первым рисунком резиста, созданным с использованием первой фотомаски, создают рисунок для формирования электрода затвора и первого межсоединения. Затем, на этапе формирования изолирующей пленки затвора, на электроде затвора и первом межсоединении последовательно формируют первую изолирующую пленку и (вторую) проводящую пленку, и после этого в многослойной пленке из первой изолирующей пленки и (второй) проводящей пленки, не защищенной вторым рисунком резиста, созданным с использованием второй фотомаски, создают рисунок для формирования изолирующей пленки затвора, имеющей контактное окно, для создания структуры межсоединения на концевой части подложки. После этого, на этапе формирования истокового слоя, в (второй) проводящей пленке, не защищенной третьим рисунком резиста, сформированным с использованием третьей фотомаски, создают рисунок для формирования электрода истока, электрода стока и второго межсоединения. Кроме того, на этапе формирования межслойной изолирующей пленки, на электроде истока, электроде стока и втором межсоединении последовательно формируют оксидную полупроводниковую пленку и вторую изолирующую пленку, и после этого во второй изолирующей пленке, не защищенной четвертым рисунком резиста, образованным с использованием четвертой фотомаски, создают рисунок для формирования межслойной изолирующей пленки. Наконец, на этапе формирования пиксельного электрода, снижают сопротивление оксидной полупроводниковой пленки, не защищенной межслойной изолирующей пленкой, для формирования пиксельного электрода, и делают проводящими первое и второе межсоединения. Здесь первое и второе межсоединения соединены между собой через проводящий участок, имеющий сниженное сопротивление оксидной полупроводниковой пленки внутри контактного окна, сформированного в изолирующей пленке затвора (многослойной пленке из первой изолирующей пленки и второй проводящей пленки), и поэтому на концевой части подложки специально сформирована структура межсоединения. В результате получают подложку со структурой тонкопленочных транзисторов с использованием четырех из первой, второй, третьей и четвертой фотомасок, и поэтому подложку со структурой тонкопленочных транзисторов, имеющую структуру межсоединения на его концевой части, изготавливают экономично, насколько это возможно. Кроме того, в изготовленной подложке со структурой тонкопленочных транзисторов участок, образующий тонкопленочный транзистор из оксидной полупроводниковой пленки, покрывают межслойной изолирующей пленкой, и поэтому сокращают вероятность повреждения плазмой, подводимой для снижения сопротивления, и т.д., обеспечивая удовлетворительные характеристики тонкопленочного транзистора. Поэтому тонкопленочный транзистор, сформированный из оксидного полупроводника и имеющий удовлетворительные характеристики, и подложку со структурой тонкопленочных транзисторов, имеющую структуру межсоединения на концевой части подложки, изготавливают с настолько низкими затратами, насколько возможно.

Этап формирования изолирующей пленки затвора может включать в себя этап, на котором формируют пленку из фоточувствительной смолы на проводящей пленке и выполняют полутоновое экспонирование пленки из фоточувствительной смолы для формирования рисунка резиста с углубленным участком, и этап, на котором проводят травление многослойной пленки из первой изолирующей пленки и проводящей пленки, не защищенной рисунком резиста, для формирования контактного окна. На этапе формирования истокового слоя толщина рисунка резиста может быть уменьшена для удаления нижней части углубленного участка рисунка резиста, чтобы обнажить проводящую пленку, и в открытой проводящей пленке может быть создан рисунок путем травления.

Вышеописанным способом, на этапе формирования изолирующей пленки затвора, сначала на электроде затвора и первом межсоединении последовательно формируют первую изолирующую пленку, (вторую) проводящую пленку и пленку из фоточувствительной смолы, и после этого пленку из фоточувствительной смолы подвергают полутоновому экспонированию с использованием второй фотомаски для получения второго рисунка резиста, имеющего углубленный участок. Затем многослойную пленку из первой изолирующей пленки и (второй) проводящей пленки, не защищенную вторым рисунком резиста, протравливают для формирования изолирующей пленки затвора, имеющей контактное окно. После этого, на этапе формирования истокового слоя, толщину второго рисунка резиста уменьшают для удаления нижней части углубленного участка второго рисунка резиста для обнажения (второй) проводящей пленки, и открытую (вторую) проводящую пленку протравливают для формирования электрода истока, электрода стока и второго межсоединения. В результате вышеупомянутая третья фотомаска больше не требуется, и подложку со структурой тонкопленочных транзисторов изготавливают с использованием трех из первой, второй и четвертой фотомасок, и поэтому подложку со структурой тонкопленочных транзисторов получают даже с меньшими затратами.

На этапе формирования пиксельного электрода оксидная полупроводниковая пленка, не защищенная межслойной изолирующей пленкой, может быть обработана плазмой.

Вышеописанным способом, на этапе формирования пиксельного электрода, оксидную полупроводниковую пленку, не защищенную межслойной изолирующей пленкой, обрабатывают плазмой. Поэтому так называемое пороговое напряжение (Vth) тонкопленочного транзистора смещается в отрицательном направлении, и поэтому сопротивление оксидной полупроводниковой пленки, не защищенной межслойной изолирующей пленкой, то есть пиксельного электрода, специально снижается.

На этапе формирования пиксельного электрода в оксидную полупроводниковую пленку, не защищенную межслойной изолирующей пленкой, может быть имплантирована примесь.

Вышеописанным способом, на этапе формирования пиксельного электрода, в оксидную полупроводниковую пленку, не защищенную межслойной изолирующей пленкой, имплантируют примесь. Поэтому так называемое пороговое напряжение (Vth) тонкопленочного транзистора смещается в отрицательном направлении, и поэтому сопротивление оксидной полупроводниковой пленки, не защищенной межслойной изолирующей пленкой, то есть пиксельного электрода, конкретно снижается.

На этапе формирования пиксельного электрода толщина оксидной полупроводниковой пленки, не защищенной межслойной изолирующей пленкой, может быть уменьшена травлением.

Вышеописанным способом, на этапе формирования пиксельного электрода, толщину оксидной полупроводниковой пленки, не защищенной межслойной изолирующей пленкой, уменьшают травлением. Поэтому так называемое пороговое напряжение (Vth) тонкопленочного транзистора смещается в отрицательном направлении, и поэтому сопротивление оксидной полупроводниковой пленки, не защищенной межслойной изолирующей пленкой, то есть пиксельного электрода, конкретно снижается.

Второе межсоединение может представлять собой линию истоков с проводимостью до электрода истока. Первое межсоединение может представлять собой первую линию соединения, сконфигурированную для соединения с линией истоков.

В вышеописанном способе второе межсоединение представляет собой линию истоков, и первое межсоединение представляет собой первую линию соединения, конфигурированную для соединения с линией истоков. Поэтому линия истоков продолжается до контактного участка и т.д. неотображающей области концевой части подложки через первую линию соединения, сформированную в том же слое, в котором создан электрод затвора, и сделанную из того же материала, что и электрод затвора.

Первое межсоединение может представлять собой линию затворов с проводимостью до электрода затвора. Второе межсоединение может представлять собой вторую линию соединения, сконфигурированную для соединения с линией затворов.

Согласно вышеописанному способу первое межсоединение представляет собой линию затворов, и второе межсоединение представляет собой второе межсоединение, сконфигурированное для соединения с линией затворов. Поэтому линия затворов продолжается до контактного участка и т.д. неотображающей области концевой части подложки через вторую линию соединения, сформированную в том же слое, в котором создан электрод истока, и сделанную из того же материала, что и электрод истока.

ПРЕИМУЩЕСТВА ИЗОБРЕТЕНИЯ

Согласно настоящему изобретению в оксидной полупроводниковой пленке для формирования пиксельного электрода не создают рисунок по отдельности, и участок для формирования тонкопленочного транзистора из оксидной полупроводниковой пленки покрывают межслойной изолирующей пленкой. Поэтому тонкопленочный транзистор, сформированный из оксидного полупроводника и имеющий удовлетворительные характеристики, и подложка со структурой тонкопленочных транзисторов, имеющая структуру межсоединения на концевой части подложки, могут быть изготовлены с настолько низкими затратами, насколько возможно.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

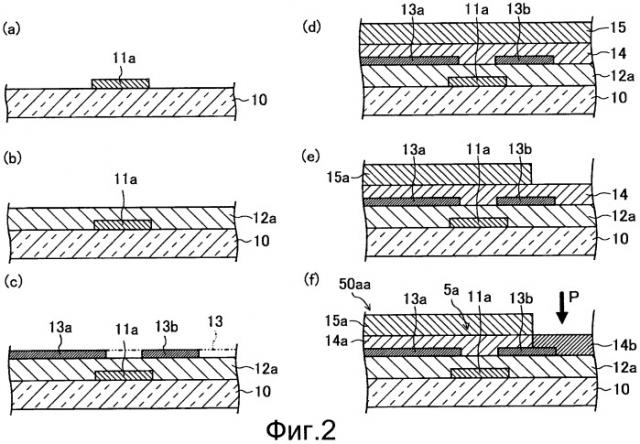

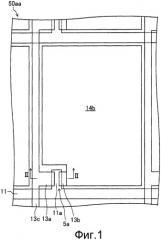

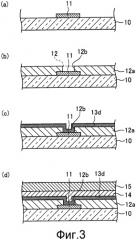

(Фиг.1) Фиг.1 представляет вид сверху подложки со структурой TFTa 50аа согласно первому варианту осуществления.

(Фиг.2) Фиг.2 представляет вид в разрезе отображающей области для описания процесса изготовления подложки 50аа со структурой TFT.

(Фиг.3) Фиг.3 представляет вид в разрезе неотображающей области для описания процесса изготовления подложки 50аа со структурой TFT.

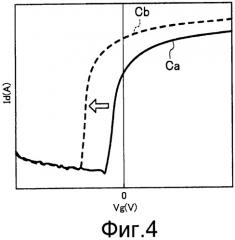

(Фиг.4) Фиг.4 представляет график, показывающий характеристики TFT 5а, включенного в подложку 50аа со структурой TFT.

(Фиг.5) Фиг.5 представляет вид в разрезе подложки 50ab со структурой TFT согласно первому варианту осуществления.

(Фиг.6) Фиг.6 представляет вид в разрезе подложки 50ас со структурой TFT согласно первому варианту осуществления.

(Фиг.7) Фиг.7 представляет вид в разрезе отображающей области для описания процесса изготовления подложки 50b со структурой TFT согласно второму варианту осуществления.

(Фиг.8) Фиг.8 представляет вид в разрезе неотображающей области для описания процесса изготовления подложки 50b со структурой TFT.

(Фиг.9) Фиг.9 представляет вид в разрезе отображающей области для описания процесса изготовления подложки 50с со структурой TFT согласно третьему варианту осуществления.

(Фиг.10) Фиг.10 представляет вид в разрезе неотображающей области для описания процесса изготовления подложки 50с со структурой TFT.

(Фиг.11) Фиг.11 представляет вид в разрезе отображающей области для описания процесса изготовления подложки 50d со структурой TFT согласно четвертому варианту осуществления.

(Фиг.12) Фиг.12 представляет вид в разрезе неотображающей области для описания процесса изготовления подложки 50d со структурой TFT.

(Фиг.13) Фиг.13 представляет вид в разрезе для описания процесса изготовления традиционной подложки 150 со структурой TFT.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Далее варианты осуществления настоящего изобретения будут описаны подробно со ссылкой на сопроводительные чертежи. Следует отметить, что настоящее изобретение не ограничивается описанными ниже вариантами осуществления.

Первый вариант осуществления изобретения

Фиг.1-6 показывают первый вариант осуществления подложки со структурой тонкопленочных транзисторов согласно настоящему изобретению. Более конкретно, фиг.1 представляет вид сверху подложки 50аа со структурой TFT согласно первому варианту осуществления. Фиг.2(а)-2(f) представляют виды в разрезе отображающей области для описания процесса изготовления подложки 50аа со структурой TFT. Фиг.3(а)-3(d) представляют виды в разрезе неотображающей области для описания процесса изготовления подложки 50аа со структурой TFT. Следует отметить, что фиг.2(f) представляет вид в разрезе подложки 50аа со структурой TFT, взятый вдоль линии II из фиг.1. Следует отметить, что фиг.4 представляет график, показывающий характеристики TFT 5, включенного в подложку 50аа со структурой TFT.

Как показано на фиг.1 и 2(f), подложка 50аа со структурой TFT включает в себя стеклянную подложку 10, многочисленные линии 11 затворов, размещенные на стеклянной подложке 10, продолжающиеся параллельно друг другу, многочисленные линии 13с истоков, продолжающиеся параллельно друг другу в направлении, перпендикулярном линиям 11 затворов, многочисленные TFT 5а, созданные на соответственных соответствующих пересечениях линий 11 затворов и линий 13с истоков, то есть в каждом случае для каждого пикселя, который представляет собой самый маленький фрагмент изображения, межслойную изолирующую пленку 15а, размещенную так, что она покрывает TFT 5а, и многочисленные пиксельные электроды 14b, размещенные в соответствующих надлежащих окнах, сформированных и размещенных в матрице в межслойной изолирующей пленке 15а и соединенных с соответственными соответствующими TFT 5а. Здесь, на подложке 50аа со структурой TFT, многочисленные пиксели (пиксельные электроды 14b) размещены в матрице, которая образует отображающую область, где отображается изображение, и неотображающей области, которая располагается вокруг отображающей области. Линия 11 затворов продолжается до неотображающей области и соединена со второй линией 13d соединения через контактное окно 12b, сформированное в изолирующей пленке 12а затвора так, что на концевой части подложки формируется структура межсоединения (смотри фиг.3(с) и 3(d)).

Как показано на фиг.1 и 2(f), TFT 5а включает в себя электрод 11а затвора, размещенный на стеклянной подложке 10, изолирующую пленку 12а затвора, сформированную так, что она покрывает электрод 11а затвора, электрод 13а истока и электрод 13b стока, созданные на изолирующей пленке 12а затвора, перекрывающие электрод 11а затвора и отделенные друг от друга, и полупроводниковый слой 14а, созданный на изолирующей пленке 12а затвора, перекрывающий электрод 11а затвора, с электродом 13а истока и электродом 13b стока, размещенными между полупроводниковым слоем 14а и электродом 11а затвора. Здесь, как показано на фиг.1, электрод 11а затвора представляет собой выступающую вбок часть линии 11 затворов, и электрод 13а истока представляет собой выступающую вбок часть линии 13с истоков и соединенную с истоковой областью полупроводникового слоя 14а. Электрод 13b стока соединен со стоковой областью полупроводникового слоя 14а и пиксельным электродом 14b.

Полупроводниковый слой 14а и пиксельный электрод 14b формируют, например, из прозрачной оксидной полупроводниковой пленки, изготовленной из In-Ga-Zn-O (IGZO), In-Si-Zn-O (ISiZO) или In-Al-Zn-O (IAlZO), и т.д. Здесь, как показано на фиг.2(е) и 2(f), пиксельный электрод 14b представляет собой часть оксидной полупроводниковой пленки 14, которая не защищена межслойной изолирующей пленкой 15а, и, как показано на фиг.4, имеет меньшее электрическое сопротивление, чем сопротивление полупроводникового слоя 14а. Следует отметить, что кривая Са обозначает характеристики TFT 5а, имеющего полупроводниковый слой 14а, кривая Cb показывает характеристики TFT, содержащего полупроводниковый слой, который соответствует пиксельному электроду 14b, имеющему пониженное сопротивление. Оксидную полупроводниковую пленку нельзя непосредственно использовать в качестве пиксельного электрода, поскольку оксидная полупроводниковая пленка имеет высокое электрическое сопротивление, когда напряжение Vg на затворе составляет 0 В (смотри кривую Са на фиг.4). Однако, как показано на фиг.4, если оксидную полупроводниковую пленку обрабатывают плазмой из N2O или водорода, пороговое напряжение (Vth) TFT смещается в отрицательном направлении (смотри кривую Cb на фиг.4), и если электрическое сопротивление, где напряжение Vg на затворе составляет 0 В, устанавливают на уровень, равный приблизительно сопротивлению элемента в открытом или включенном состоянии, то оксидную полупроводниковую пленку можно использовать в качестве пиксельного электрода.

Например, сформированная таким образом подложка 50аа со структурой TFT, подложка цветного фильтра (CF), находящаяся напротив подложки 50аа со структурой TFT, и жидкокристаллический слой, размещенный между этими подложками, составляют жидкокристаллическую панель отображения.

Далее будет описан способ изготовления подложки со структурой 50аа TFT согласно этому варианту осуществления со ссылкой на фиг.2 и 3. Следует отметить, что способ изготовления в этом варианте осуществления включает в себя этап формирования затворного слоя, этап формирования изолирующей пленки затвора, этап формирования истокового слоя, этап формирования межслойной изолирующей пленки и этап формирования пиксельного электрода.

Этап формирования затворного слоя

Сначала, например, на всей стеклянной подложке 10, имеющей толщину 0,7 мм, путем распыления формируют первую металлическую проводящую пленку (не показана), такую как алюминиев