Бистабильная ячейка памяти на базе однослойной наноструктуры

Иллюстрации

Показать всеИспользование: для создания интегральных схем памяти с элементами нанометровых размеров. Сущность изобретения заключается в том, что бистабильная ячейка памяти на базе однослойной наноструктуры, имеющая горизонтально ориентированные слои, содержит диэлектрическую подложку, размещенные на диэлектрической подложке первый, второй логические транзисторы, первый, второй нагрузочные диоды и выполнена наноразмерной со ступенчатым профилем, где рабочие переходы «база-эмиттер», «база-коллектор» двух транзисторов являются поверхностными переходами, которые обладают низкой мощностью потребления и наименьшими поверхностями переходов. Технический результат: обеспечение возможности снижения потребляемой мощности при одновременном повышении быстродействия за счет снижения паразитных емкостей рабочих переходов. 8 ил.

Реферат

Изобретение относится к полупроводниковой микроэлектронике и наноэлектронике и может быть использовано при создании интегральных схем памяти с элементами нанометровых размеров.

Известна комплементарная Би-МОП ячейка памяти конденсаторного типа, содержащая биполярный транзистор, нагрузочный МОП-транзистор и конденсатор, сформированный областями вертикального МОП-транзистора (Патент США №7199417, МПК H01L 29/76, опубл. 03.04.2007).

Недостатками известного устройства являются низкое быстродействие из-за большого времени рассасывания зарядов из емкости, хранящей информацию, и сложность получения большого количества различных слоев.

Техническая задача, на решение которой направлено предлагаемое изобретение, состоит в создании бистабильной ячейки памяти на базе однослойной структуры нанометрового размера, обладающей повышенным быстродействием.

Поставленная техническая задача решается тем, что предложена бистабильная ячейка памяти на базе однослойной наноструктуры, содержащая диэлектрическую подложку, в которой расположены первая область первого типа проводимости, на которую подается напряжение питания, выполнена наноразмерной, шириной от 20 нм до 60 нм, длиной от 130 нм до 390 нм, являющаяся общим анодом нагрузочных диодов; имеет непосредственный контакт с первой областью второго типа проводимости, которая является катодом первого нагрузочного диода и коллектором первого переключающего транзистора, выполнена наноразмерной, со ступенчатым профилем шириной от 30 нм и до 90 нм, длиной от 60 нм до 180 нм, к которой подключен контакт, соответствующий инверсному выходу ячейки памяти; имеет непосредственный контакт со второй областью первого типа проводимости, которая является базой первого переключающего транзистора, выполнена наноразмерной, со ступенчатым профилем шириной от 15 нм до 45 нм, длиной от 60 нм до 180 нм, к которой подключен контакт, соответствующий прямому выходу ячейки памяти; имеет непосредственный контакт со второй областью второго типа проводимости, которая является первым эмиттером первого переключающего транзистора, выполнена наноразмерной, длиной и шириной от 30 нм до 90 нм, к которой подключена шина записи нуля, с третьей областью второго типа проводимости, которая является вторым эмиттером первого и второго переключающих транзисторов, выполнена наноразмерной, длиной от 50 нм до 150 нм, шириной от 30 нм до 90 нм, к которой подключена шина опорного напряжения; имеет непосредственный контакт с третьей областью первого типа проводимости, которая является базой второго переключающего транзистора, выполнена наноразмерной, со ступенчатым профилем шириной от 15 нм до 45 нм, длиной от 60 нм до 180 нм, к которой подключен контакт, соответствующий инверсному выходу ячейки памяти; имеет непосредственный контакт с четвертой областью второго типа проводимости, которая является вторым эмиттером второго переключающего транзистора, выполнена наноразмерной, длиной и шириной не менее 30 нм, к которой подключена шина записи единицы, с пятой областью второго типа проводимости, которая является катодом второго нагрузочного диода и коллектором второго переключающего транзистора, выполнена наноразмерной, со ступенчатым профилем шириной от 30 нм до 90 нм, длиной от 60 нм до 180 нм, к которой подключен контакт, соответствующий прямому выходу ячейки памяти, связан с первой областью первого типа проводимости, первая и пятая области второго типа проводимости разделены областью с диэлектрическими свойствами шириной от 10 нм до 30 нм, вторая и третья области первого типа проводимости разделены областью с диэлектрическими свойствами шириной от 10 нм до 30 нм.

В качестве диэлектрика могут выступать как окислы, так и газы.

Технический результат, достижение которого обеспечивается реализацией всей заявленной совокупности существенных признаков, состоит в снижении потребляемой мощности при одновременном повышении быстродействия за счет снижения паразитных емкостей рабочих переходов.

Создана новая бистабильная ячейка памяти на базе однослойной структуры нанометровых размеров с горизонтально ориентированными слоями, в которой рабочими переходами «база-эмиттер», «база-коллектор» двух транзисторов являются поверхностные переходы, которые обладают низкой мощностью потребления и наименьшими поверхностями переходов, что и обеспечивает снижение потребляемой мощности при одновременном повышении быстродействия за счет снижения паразитных емкостей рабочих переходов.

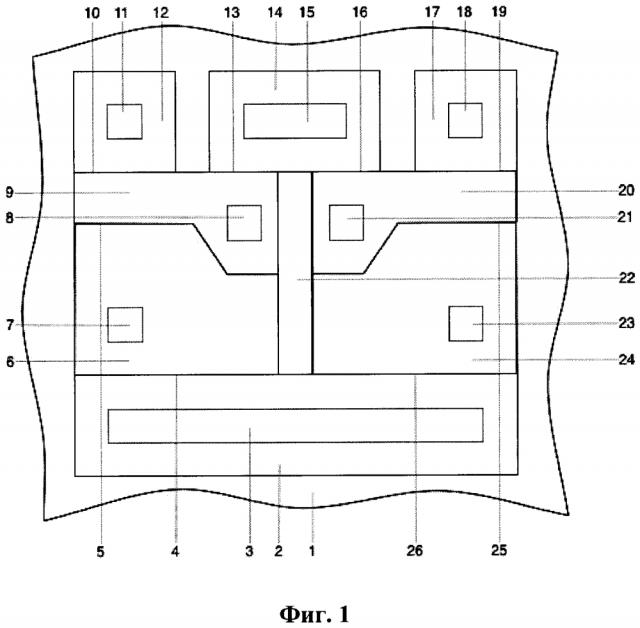

Сущность заявляемого изобретения поясняется рисунками, где

на фиг. 1 приведена принципиальная обобщенная схема заявляемой бистабильной ячейки памяти;

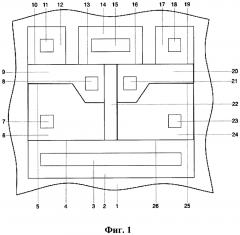

на фиг. 2 приведен вид сбоку схемы заявляемой ячейки памяти на базе однослойной наноструктуры фиг. 1;

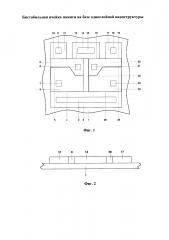

на фиг. 3 приведена схема, поясняющая работу устройства;

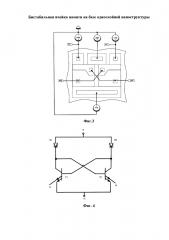

на фиг. 4 приведена эквивалентная транзисторная схема;

на фиг. 5, фиг. 6 и фиг. 7 приведены результаты работы наноструктуры бистабильной ячейки памяти, включенной по схеме (фиг. 3) в двух режимах: когда на вход S подается напряжение логической единицы и когда на вход R подается напряжение логического нуля для следующих параметров:

на фиг. 5 а) - распределение электронной плотности; б) - распределение дырочной плотности; в) - абсолютное значение плотности электронного тока в наноструктуре бистабильной ячейке памяти;

на фиг. 6 а) - распределение пространственного заряда; б) - распределение электростатического потенциала;

на фиг. 7 а) - график общего тока через контакт, подключенный к шине записи единицы (18); б) - график общего тока через контакт, подключенный к шине сброса в ноль (11);

на фиг. 8 а) и б) приведены передаточная характеристика для прямого и обратного выходов наноструктуры бистабильной ячейки памяти, которая демонстрирует выполнение наноструктурой, включенной по схеме (фиг. 3), реализацию функции установки в единицу и сброса состояния, что говорит о ее работоспособности.

Рисунок на фиг. 1 содержит следующие позиции:

1 - диэлектрическая подложка,

2 - первая область первого типа проводимости,

3 - контакт, подключенный к питанию,

4 - поверхностный переход первого нагрузочного диода,

5 - поверхностный переход «база-коллектор» первого переключающего транзистора,

6 - первая область второго типа проводимости,

7 - контакт, соответствующий инверсному выходу ячейки памяти,

8 - контакт для подключения ко второй области первого типа проводимости,

9 - вторая область первого типа проводимости,

10 - первый поверхностный переход «база-эмиттер» первого переключающего транзистора,

11 - контакт, подключенный к шине записи нуля,

12 - вторая область второго типа проводимости,

13 - второй поверхностный переход «база-эмиттер» первого переключающего транзистора,

14 - контакт для подачи опорного напряжения,

15 - третья область второго типа проводимости,

16 - первый поверхностный переход «база-эмиттер» второго переключающего транзистора,

17 - четвертая область второго типа проводимости,

18 - контакт, подключенный к шине записи единицы,

19 - второй поверхностный переход «база-эмиттер» второго переключающего транзистора,

20 - третья область первого типа проводимости,

21 - контакт для подключения к третьей области первого типа проводимости,

22 - слой диэлектрика,

23 - контакт, соответствующий прямому выходу ячейки памяти,

24 - пятая область второго типа проводимости,

25 - поверхностный переход «база-коллектор» второго переключающего транзистора,

26 - поверхностный переход второго нагрузочного диода.

Ячейка памяти на базе однослойной наноструктуры (фиг. 1 и фиг. 2) содержит диэлектрическую подложку (1), область анодов нагрузочных диодов (первого типа проводимости) (2) шириной от 20 нм до 60 нм, длиной от 130 нм до 390 нм, контакт, подключенный к питанию (3), области катодов нагрузочных диодов и коллекторов переключающих транзисторов (второго типа проводимости) шириной от 30 нм до 90 нм, длиной от 60 нм до 180 нм (6, 24), области баз переключающих транзисторов (первого типа проводимости) шириной до 15 нм до 45 нм, длиной от 60 нм до 180 нм (9, 20), области эмиттеров переключающих транзисторов (второго типа проводимости) длиной и шириной от 30 нм от 90 нм (12, 17), длиной от 50 нм до 150 нм, шириной от 30 нм до 90 нм (14), контакты эмиттеров переключающих транзисторов (11, 15, 18), поверхностные переходы «база-эмиттер» (10 13, 16, 19), поверхностные переходы «база-коллектор» (5, 25), поверхностные переходы нагрузочных диодов (4, 26), контакты, соответствующие прямому выходу (8, 23), контакты, соответствующие обратному выходу (7, 21), диэлектрическая область шириной от 10 нм до 30 нм (22). Ячейка памяти на базе однослойной наноструктуры выполнена наноразмерной.

Уменьшение минимальных размеров перечисленных элементов ведет к увеличению воздействия квантовых эффектов, что нарушает работу заявляемой структуры.

Увеличение максимальных размеров перечисленных элементов ведет к увеличению площади, тем самым:

- уменьшая информационную плотность,

- увеличивая потребляемую мощность,

- уменьшая быстродействие.

Ячейка памяти на базе однослойной наноструктуры выполнена наноразмерной.

Нанослои могут быть сформированы с использованием любой известной технологии формирования поверхностных полупроводниковых нанослоев, например, молекулярным выращиванием.

Режим записи единицы: При подаче на контакт 18 высокого уровня напряжения (выше, чем u0), а на контакт 11 низкого уровня напряжения, транзистор Т1 закрывается, а транзистор Т2 открывается, основная часть тока течет через области (2, 6, 9, 12), на коллекторе Т2 низкий потенциал, что соответствует инверсному выходу, низкий потенциал поступает на базу Т1, закрывая транзистор Т1, при этом потенциал на его коллекторе растет до напряжения логической единицы, что соответствует записи логической единицы бистабильной ячейки.

Режим записи нуля: При подаче на контакт 11 высокого уровня напряжения (выше, чем u0), а на контакт 18 низкого уровня напряжения, транзистор Т2 закрывается, а транзистор Т1 открывается, основная часть тока течет через области (2, 24, 20, 17), на коллекторе Т1 низкий потенциал, что соответствует прямому выходу, низкий потенциал поступает на базу Т2, закрывая транзистор Т2, при этом потенциал на его коллекторе растет до напряжения логической единицы, что соответствует сбросу в логической ноль ячейки памяти на базе однослойной наноструктуры.

Режим хранения информации: В случае подачи на контакт записи единицы (18) и контакт записи нуля (11) напряжения логического нуля происходит неизменение режима работы схемы. Ячейка памяти сохраняет предыдущее состояние.

Комбинация высоких потенциалов на обеих шинах является запрещенной, как для обычного RS-триггера.

Анализ работы наноструктуры бистабильной ячейки памяти доказывает ее работоспособность и выполнения функции RS-триггера.

Предлагаемая ячейка памяти на базе однослойной наноструктуры обеспечивает высокое быстродействие (за счет использования поверхностных переходов биполярного транзистора, имеющих наименьшую паразитную емкость), наличие всего одного слоя позволяет экономить на производстве и использовать менее дорогостоящие технологические процессы.

Бистабильная ячейка памяти на базе однослойной наноструктуры, содержащая диэлектрическую подложку, отличающаяся тем, что на подложке расположены первая область первого типа проводимости, на которую подается напряжение питания, выполнена наноразмерной, шириной от 20 нм до 60 нм, длиной от 130 нм до 390 нм, являющаяся общим анодом нагрузочных диодов; имеет непосредственный контакт с первой областью второго типа проводимости, которая является катодом первого нагрузочного диода и коллектором первого переключающего транзистора, выполнена наноразмерной, со ступенчатым профилем шириной от 30 нм и до 90 нм, длиной от 60 нм до 180 нм, к которой подключен контакт, соответствующий инверсному выходу ячейки памяти; имеет непосредственный контакт со второй областью первого типа проводимости, которая является базой первого переключающего транзистора, выполнена наноразмерной, со ступенчатым профилем шириной от 15 нм до 45 нм, длиной от 60 нм до 180 нм, к которой подключен контакт, соответствующий прямому выходу ячейки памяти; имеет непосредственный контакт со второй областью второго типа проводимости, которая является первым эмиттером первого переключающего транзистора, выполнена наноразмерной, длиной и шириной от 30 нм до 90 нм, к которой подключена шина записи нуля, с третьей областью второго типа проводимости, которая является вторым эмиттером первого и второго переключающих транзисторов, выполнена наноразмерной, длиной от 50 нм до 150 нм, шириной от 30 нм до 90 нм, к которой подключена шина опорного напряжения; имеет непосредственный контакт с третьей областью первого типа проводимости, которая является базой второго переключающего транзистора, выполнена наноразмерной, со ступенчатым профилем шириной от 15 нм до 45 нм, длиной от 60 нм до 180 нм, к которой подключен контакт, соответствующий инверсному выходу ячейки памяти; имеет непосредственный контакт с четвертой областью

второго типа проводимости, которая является вторым эмиттером второго переключающего транзистора, выполнена наноразмерной, длиной и шириной не менее 30 нм, к которой подключена шина записи единицы, с пятой областью второго типа проводимости, которая является катодом второго нагрузочного диода и коллектором второго переключающего транзистора, выполнена наноразмерной, со ступенчатым профилем шириной от 30 нм до 90 нм, длиной от 60 нм до 180 нм, к которой подключен контакт, соответствующий прямому выходу ячейки памяти, связан с первой областью первого типа проводимости, первая и пятая области второго типа проводимости разделены областью с диэлектрическими свойствами шириной от 10 нм до 30 нм, вторая и третья области первого типа проводимости разделены областью с диэлектрическими свойствами шириной от 10 нм до 30 нм.