Блок согласования с магистралью

Иллюстрации

Показать всеРеферат

ОП HCAH HE

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (51)М. Кл.2 (22) Заявлено 2906,77 (21) 2501719/18-24 (085959) с присоединенИем заявки ¹

G 06 F 3/04

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 05.05.8(1Бюллетень № 17

Дата опубликования описания 050580 (53) УДК 681.327 (088. 8) В.Л.Дшхунян, С.С.Коваленко, В.Т,Желудов, П.Р.Машевич, В.В.Теленков и Ю.E.×è÷åðèí (72) Авторы изобретения (71) Заявитель (54) БЛЭК СОГЛАСОВАНИЯ С МАГИСТРАЛЬЮ

1 1

0 1 0 0 0

1О

Формирование на сигнальной шине строб (на которой формируется сигнал выдачи информации ) уровн я логического О соответствует формированию на выходе магистрального элемента неопределенного уровня (-) . При формировании на сигнальной шине

Строб уровня логической 1 на выходе магистрального блока формируется логический уровень, соответствую. щий поступающей информации.

Изобретение относится. к вычислительной технике и может быть использовано при проектировании цифровых интегральных схем.

Известен магистральный элемент, используемый в интегральных схемах.

Он предназначен для работы на внешнюю магистраль и содержит формирователь логического уровня, выход которого соединен с выходом магистрального элемента и схему управления, выход которой подключен ко входу формирователя логического уровня,а входы к информационной шине и шине управления выдачей информации.

По технической сущности наиболее близким к предлагаемому является блок согла сования с магистралью, содержащий формирователь логического уровня, элементы НЕ, И-НЕ, ИЛИНЕ, информационную шину, подключенную к первым входам первых элементов И-НЕ и ИЛИ вЂ , шина управления блока подключена ко второму входу первого элемента И-НЕ, и через первый элемент НЕ ко второму входу первого элемента ИЛИ-НВ, выход которого подключен к первому входу формирователя логического уровня, Логика работы блока согласования с магистралью может быть представ,лена следующим образом:

Инф.Строб.Вых.И-НЕ Вых.ИЛИ-HE Вых.М,В

Х 0 1 0

При организации магистральной структуры состояние Отключено должно соответствовать уровню логического

О, при этом любой выходной блок этой магистрали должен иметь возможность установить на магистрали уровень логической 1.

В известном магистральном элемен30 те состояние Отключено соответст73?841

15

25

45

55

60 вует неопределенному логическому уровню, а уровень логического О активный и не позноляет установить извне уровень логической 1.

Время восстановления уровня логического О н этом блоке после выдачи логической 1 существенно велико.

Это определяется тем, что к выходу блока подключен высокоомный резистор, обеспечивающий формиронание на выходе в состояние Отключено уровня логического о. Поэтому при переключении блока с уровня логической 1 в состояние Отключено (доопределяется до уроння логического о) требуется существенное время.

Цель изобретения — повышение надежности и бьгстродействия.

Цель достигается тем, что блок согласования с магистралью содержит элемент И и триггер, первый вход которого является выходом блока, второй в ход подключен к шине упра нления, выход триггера и шина управления подключены соответственно к первому и второму входу второго элемента ИЛИ-НЕ, выход которого подклю,чен к первому входу второго элемента И-НЕ, второй вход которого через второй элемент НЕ подключен к выходу блока согласования, входы элемента

И подключены соответственно к выходам первого и второго элементов

И-НЕ, выход элемента И подключен ко второму входу формирователя логического уровня, а формирователь логического уровня содержит дна р-канальных транзистора и один и-канальный ,МДП транзистор, стоки которых подключены к выходу формирователя логического уровня, истоки двух р-канальных МДП транзисторон подключены к ,шине питания, сток и-канального МДП транзистора подключен к шине нулевого потенциала, затвор — к первому входу формирователя логического уровня, затвор первого р-канального

МДП транзистора подключен ко второму входу формирователя логического уровня, затвор второго р-канального транзистора подключен к шине нулевого потенциала.

Триггер предназначен для запоминания импульса выдачи информации под действием уровня логической 1 с выхода блока и сигнала с выхода триггера на одном входе формирователя внешнего логического уровня устанавливается сигнал обеспечивающий формирование на выходе магистрального элемента уровня логического О. После установления на выходе блока уровня логического

О триггер сбрасывается .и выходной элемент отключается.

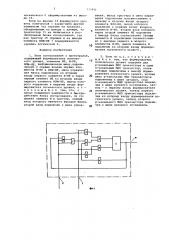

На фиг.1 представлена функциональная схема магистрального элемен. та; на фиг.2 — принципиальная схема формирователя выходного уровня.

Маг истральный элемент содержит информационную шину 1, шины 2 управления, элементы НЕ 3 и 4, элементы И вЂ” НЕ 5 и б, элементы ИЛИ

7 и 8, элемент И 9, триггер 10, формирон атель 11 выходного уровня, входы l 2 и 1 3 формирователя выходгного уровня, выход 14 блока согла сования <= магистралью, р-канальный

МДП транзистор 15, п-канальный транзистор 16, р-канальный МДП транзистор 17.

Вход 12 формирователя 11 подключен к затвору транзистора 15, а вход

13 к затвору транзистора )6. Стоки транзисторов 15, 16 и 17 объединены и образуют выход 14 магистрального элемента.

Рассмотрим выдачу информации, соответствующую выдаче логического О (высокий уровень потенциала на выходе 14 блока согласования с ма— гистралью) и логической 1 (низкий уровень сигнала на выходе )4).

Выдаче логического О соответствует возбуждение элемента И-НЕ 5, формирование на его выходе логического О. На ныходе элемента И 9 формируется уровень логического О, который поступает на вход 12 формирователя 11. Включается р-канальный транзистор 15 и на выходе 1.4 формируется уровень логического О. Когда на вход 2 не поступает стробирующий сигнал, транзистор 15 отмечается и на выходе 14 блока согласования с магистралью поддерживается уровень логического О за счет постоянно включенного нысокоомного транзистора 17. Все остальные элементы блока в режиме выдачи логического О не работают. При ныдаче логической 1 на выходе элемента ИЛИ—

НЕ 8 формируется уровень логической 1, который поступает на вход

13 формирователя 11, включается и-канальный транзистор 16 и на выходе 14 формируется уронень логической 1. Триггер 10 переключается и формирует на своем выходе логический О . После окончания выдачи информации (на вход 2 поступает уровень логического О) элемент И вЂ” НЕ 7 формирует на своем выходе уровень логической 1. На выходе элемента НЕ 4 уровень логической 1. Возбуждаются элементы И-НЕ 6, И 9, р-канальный транзистор 15 соответственно.

Транзистор 15 открыт до тех пор, пока на выходе 14 не сформируется уровень логического О. Это обеспечивается обратной связью через элемент

НЕ 4, элемент И-HE б и элемент И 9, транзистор 15 отключается. Уровень логического О на .выходе 14 поддерживается высокоомным транзистором 17.

Триггер 10 сбрасывается уровнем

732R41

Формула изобретения логического 0 сформированным на выходе 14.

Если на выходе 14 формируется уровень логической 1 каким-либо другим элементом (на чертеже не показан), объединенным по выходу с данным, то транзистор 15 не включается в рассмотренном блоке согласования, так как триггер 10 сброшен и на выходе элемента ИЛИ-НЕ 7 поддерживается уровень логической О.

1. Блок согласования с магистралью, содержащий формирователь логического уровня, элементы НЕ, -HE, 15

HJIH — HE, информационную шинулюдключенную к первым входам первых элементов И-НЕ и ИЛИ-НЕ, шина управления блока подключена ко второму входу первого элемента И-HE и через 20 первый элемент НЕ ко второму входу первого элемента ИЛИ-НЕ, выход которого подключен к первому входу формирователя логического уровня, о т л и ч а ю Ш и я с ÿ тем, что, с целью повышения надежности и быстродействия блока согласования, он содержит элемент И и триггер, первый вход которого является выходом блока, второй вход подключен к шине управления, выход триггера и шина управления подключены соответственно к первому и второму входу второго элемента ИЛИ вЂ” НЕ, выход которого подключен к первому входу второго элемента И-НЕ, второй вход которого через второй элемент НЕ подключен к выходу блока согласования (входы элемента И подключены соответствен— но к выходам первого и второго элементов И-НЕ, выход элемента И подключен ко второму входу формирователя логического уровня) .

2. Блок по п.1, о т л и ч а ю шийся тем, что формирователь логического уровня содержит два р-канальных МДП транзистора и один п-канальный МДП транзистор, стоки которых подключены к выходу формирователя логического уровня, истоки двух р-канальных МДП транзисторов подключены к шине питания, сток и-канального МДП транзистора подключен к шине нулевого потенциала, затвор — к первому входу формирователя логического уровня, затвор первого р-канального МДП транзистора подключен ко второму входу формирователя логического уровня, затвор второго р-канального МДП транзистора подключен к шине нулевого потенциала..

732841

Составитель В.Теленков

Техред Ж.Кастелевич

Редактор З.Шубенко

Корректор М,Вигула

Заказ 1553/9

Тираж 751

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4